最近,中科院微电子研究所刘明院士、李泠研究员团队在先进逻辑工艺可靠性问题的紧凑模型取得最新研究成果,此研究成果以题为“A Unified Physical BTI Compact Model in Variability-Aware DTCO Flow: Device Characterization and Circuit Evaluation on Reliability of Scaling Technology Nodes”的文章入选2021 VLSI Technology。

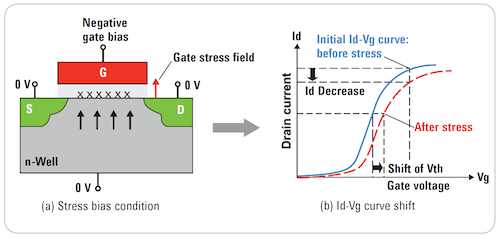

BTI效应会影响到器件的使用,并随着技术节点的降低,BTI逐渐成为器件可靠性的瓶颈,因此如何降低BTI效应是器件可靠性的重要研究方向。下图是PMOS碰到BTI问题后,器件性能受到影响,同样NMOS也会有类似的问题,假如这种问题发生在像高密度的SRAM应用中,会严重影响 static noise margin (SNM) and write noise margin (WNM) 。

图1 PMOS NBTI的原理,和对器件性能的影响

在这种背景下,偏置温度不稳定(BTI)效应成为集成电路(IC)器件可靠性的关键问题之一,微电子所团队开发了一个统一的物理和统计紧凑模型,可以预测BTI对不同工艺节点的器件及电路(低至14nm)的影响,包含复杂的应力/恢复模式表征、超长期老化预测和工艺统计变量(TSV)的影响,实现cycle to cycle/device to device的可靠性评估。

该模型基于2/4态的缺陷中心(DC)理论,针对缺陷的物理特性(如能级分布、占据概率等)建模。通过TCAD仿真验证和对鳍状场效应晶体管(FinFET)、平面晶体管等可靠性实验测试结果的校准,成功地嵌入了BSIM-CMG通用模型,用于器件及电路的动态时间演化和动态电压缩放分析。这种物理的、可变性的和具有耐久性感知的紧凑模型有潜力将VLSI可靠性设计技术协同优化(DTCO)流程提升到下一代技术节点。

随着节点的提升,Design for reliability 变得越来越重要,因为一次流片设计价格不菲,很多中小企业禁不起几轮流片失败。因此,如何把BTI等可靠性模型嵌入现有设计中,显得尤其重要。同时,如果有了这个武器,设计带来的附加价值和寿命就会明显提高。

随着电子产品应用的广泛,在不同领域,比如汽車、医疗、工业、航天天空及国防应用等产品都会遇到生命週期可靠性的问题,因此,在这个层面,基于半导体厂工艺的模型开发是重中之重,同时如何和EDA厂商合作,获得接近产品实际特性的仿真结果也有很多协同工作要做。

有一点可以确认,模型从业人员通过模型二次开发的核心价值来获得独特的设计这个角度去看,相信将来会有很多基于模型扩展基础上的小而美的设计公司创立,因为欧洲已经有很多创新公司值得我们借鉴。

编辑:jq

-

器件

+关注

关注

4文章

310浏览量

27824

原文标题:偏置温度不稳定(BTI)的模型开发应用

文章出处:【微信号:弘模半导体,微信公众号:弘模半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于偏置温度不稳定(BTI)的技术

基于偏置温度不稳定(BTI)的技术

评论