Chip First工艺

自从Fan-Out封装问世以来,经过多年的技术发展,扇出式封装已经形成了多种封装流程、封装结构以适应不同产品需要,根据工艺流程,可以分为先贴芯片后加工RDL的Chip First工艺和先制作RDL后贴装芯片的Chip Last工艺两大类,其中,结构最简单的是采用Chip First工艺的eWLB,

其工艺流程如下:

1

将切割好的芯片Pad面向下粘贴在带临时键合胶的载片上;

2

从芯片背面对载片进行灌胶塑封;

3

移除临时载片形成塑封后的二次晶圆(扇出式晶圆);

4

去除Pad上的残留胶并在Pad面形成RDL层;

5

在RDL层上植球并切割成单个成品。

此技术的优势是制程相对简单,成本优势明显。但由于移除载片后,扇出晶圆的翘曲难以控制,对RDL线路的生长技术提出了挑战,难以制作高密度的RDL,因此该技术主要应用于布线密度较低的中低端的产品。

真正让Chip First扇出式封装成为行业热点的原因无疑是因为台积电(TSMC)在2016年在I-phone7中使用了InFOTM结构。

其工艺流程如下:

1

在晶圆Pad上制作一层预制铜柱;

2

将切割好的芯片Pad面向上粘贴在带临时键合胶的载片上;

3

对载片进行灌胶塑封;

4

对塑封好的扇出晶圆进行研磨,露出预制铜柱的顶部;

5

在预制铜柱的顶部进一步制作RDL及植球移除载片;

6

将完成植球的扇出式晶圆切割成单个成品。

该技术由于布线工艺在载片上完成,没有翘曲等因素的影响,因而能够实现高密度布线,同时整体封装厚度也能控制的很低,多应用在高端手机处理器等高价值芯片上。缺点是工艺控制要求高,而且RDL良率直接会影响到芯片成品率,因此最终成品价格较高。

以上方式都是先贴芯片后制作RDL的工艺,所以称为Chip-First工艺,如果先制作RDL,然后在RDL上贴装芯片,便称为Chip-Last工艺。此工艺需要在RDL上倒装植球后的芯片,通常适用于空间要求略高的FcBGA产品,但由于只在检验合格的RDL上贴装芯片,可避免RDL工程良率给芯片带来的损失,因此对于价格昂贵的高端芯片而言,有较明显的价格优势。

长电科技Chip Last工艺

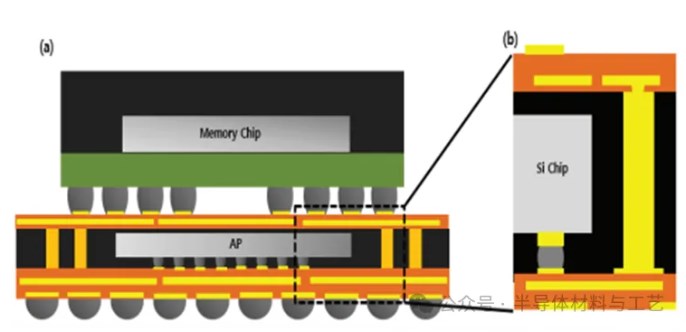

长电科技2021年7月正式推出了一款使用Chip-Last封装工艺的高密度扇出式封装 — XDFOITM-FcBGA-H。

其工艺流程如下:

1

在带临时键合胶的载片上制作RDL线路层;

2

倒装焊接上已植球切割好的芯片;

3

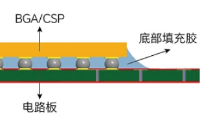

芯片底部焊接区域进行底部填充,再对整张贴好芯片的基板进行整体塑封;

4

移除载片并在圆片底部形成Bump;

5

对此整个扇出式原片进行研磨与切割后形成XDFOITM Fan-Out Unit颗粒;

6

将Fan-Out Unit倒装封装在基板上并进行底部填充;

7

贴装散热盖及植球,最终形成XDFOITM-FcBGA-H封装。

此技术的优点在于:避免了RDL良率造成的芯片损失,具有更高的成本竞争力,且直接在载片上布线RDL,简化了工艺。另外RDL的布线间距也可以达到2um水准,大大提高布线密度,能满足高性能产品封装需求。

Fan-Out封装发展趋势

随着Chip-Let技术会越来越得到半导体业界的重视,封装技术的发展已经成为了半导体行业发展的重要支点,而先进高密度Fan-Out封装也必然是发展中的热点。

根据目前的发展趋势看,Fan-Out封装主要有以下几个发展趋势:

01|高密度布线

根据行业发展预测,下一代Fan-Out技术RDL的布线间距将达到1um以下,这将对RDL布线技术的发展提出进一步挑战。

02|产品大型化

由于突破了单个硅芯片限制, 多Die合封的封装单元尺寸很容易突破原有单颗硅芯片常规上限(通常为830mm2)的限制,各大OSAT的合封单元目标都在1500mm2以上,有的面积甚至将达到2500mm2,这对封装工艺以及封装材料开发提出了巨大的挑战。

03|封装结构复杂化

在Chip-Let技术发展路线图中,芯片互联种类越来越复杂,不仅有RDL互联,还有硅基板Interposer互联,桥接芯片互联等封装方式都在快速发展中。封装模式的多元化对制程能力开发也提出了更高的要求。

台积电、Intel、Samsung等国际顶尖半导体公司都已成功进军先进封装市场。各大先进半导体公司都确立发展高密度扇出式封装为技术战略方向。值此变革之时,长电科技紧跟时代潮流,在先进封装上积极投入,率先在国内开发出了自己的先进高密度Fan-Out封装。长电科技不但要在国内企业中保持技术领先优势,还要进一步开拓进取,继续在先进封装上加大研发力度,力争在后摩尔时代的半导体技术开发的国际竞争中占得先机。

责任编辑:haq

-

芯片

+关注

关注

455文章

50712浏览量

423106 -

封装

+关注

关注

126文章

7873浏览量

142890 -

长电科技

+关注

关注

5文章

351浏览量

32499

原文标题:先进高性能计算芯片中的扇出式封装(下篇)

文章出处:【微信号:gh_0837f8870e15,微信公众号:长电科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

轴承结构生产工艺流程柴油机轴承的结构与安装

SMT工艺流程详解

简述连接器的工艺流程

芯片底部填充工艺流程有哪些?

扇出式封装的工艺流程

扇出式封装的工艺流程

评论