FPGA方案

随着一款产品在研发阶段的日渐成熟,实现的功能也日趋复杂化和多样化,对产品功能实现重定义的应用需求也在日益加大。产品功能重定义就是在不改动设备硬件设计的前提下,通过更改FPGA的程序文件,达到产品功能重定义的方法。

一般的产品在设计时,研发会按照产品的定义完成功能代码的开发,然后用JTAG接口进行烧录、调试,但是等产品上线时,所有的固件就会被固化,并且因为JTAG接口过于笨重,我们一般是不保留该接口;所以也无法在产品完成固化后进行重新烧录进行重定义的操作。

目前也有一些应用方案会使用BLE/WIFI SOC+存储芯片的架构,BLE/WIFI SOC负责存储芯片的读写,存储芯片作为FPGA的程序代码存储器,工作时,BLE/WIFI SOC将存储芯片中的数据读出,并按照特定时序(FPGA加载时序)发送到FPGA,此过程即为FPGA的数据加载流程,如果需要升级功能,通过无线进行远程OTA升级。而本方案是无需其它芯片参与的情况下通过逻辑设计和UART口进行产品功能的重定义。

逻辑设计

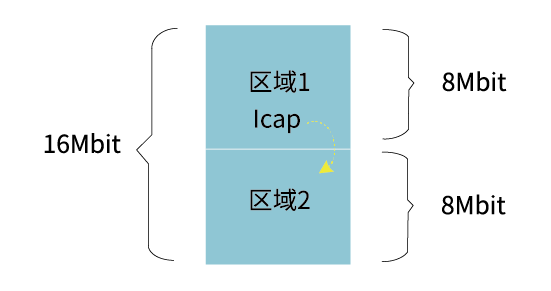

本方案的核心就是双启动,其中区域1为固化区域,此区域非功能区域,而是负责区域2的管理,其中区域2为功能区域,每次的功能重定义就是对区域2的刷新。区域2的刷新通过PC和串口调试助手模拟上位机,传输工程的 Bin文件到 fpga启动配置的 Flash中,实现两个存储到 flash程序的跳转完成固件升级操作。

设置两个区域,第一个区域执行程序1,完成对区域2的管理和升级工作。第二个区域的程序2是我们用户设计的功能程序或者说产品程序。在 FPGA启动中,如果我们不升级区域 2的程序,那么自动通过 ICap接口跳转到区域2的程序中。区域1起始地址 0x0,区域2起始地址 0x0100000。

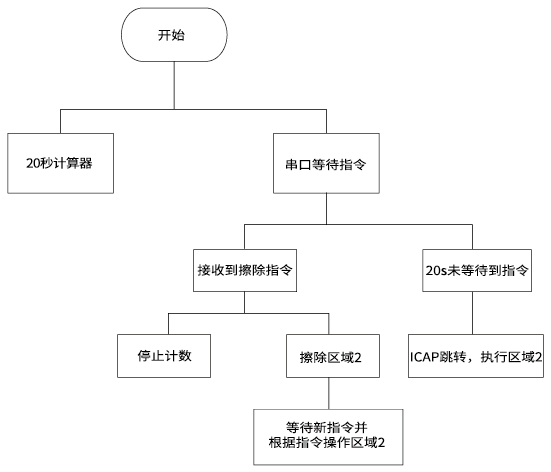

在本方案中,设计区域1的程序实现的功能为:上电后自动加载此程序,此时开始计时如果 20秒内没有检测到串口发送的擦除指令,那么我们启动 icap跳转,跳转到区域 2程序中。

如果希望再次升级的话必须重新给板卡上电使得程序回到区域1中。

流程图如下:

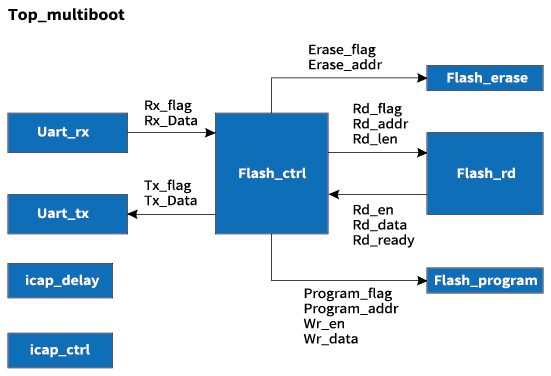

顶层结构图如下:

FPGA uart接收模块,接收上位机发送的数据,并实现波特率为115200的uart协议的串行数据到并行数据的转换,将数据发送至flash_ctrl模块,Flash_ctrl模块是flash的控制模块,该模块自定义了一个简单的协议,根据uart指令来控制flash的擦除、读、写,协议包括三种数据包来对应相应的指令,再将数据发送至对应的模块;而由flash擦除、读、写三个模块处理的数据返回后经过uart_tx模块返回上位机,本文中即返回PC机串口模块。

编辑:YYX

-

芯片

+关注

关注

455文章

50714浏览量

423113 -

上位机

+关注

关注

27文章

941浏览量

54789

发布评论请先 登录

相关推荐

百灵鸟电路的设计方案

FPGA设计大赛设计方案提交规则和截止时间须知

多种EDA工具的FPGA设计方案

基于FPGA的百变设计方案分享

基于FPGA的百变设计方案分享

评论