Q1

产品客户在上板后测试功能异常2%,拆下的不良品开盖发现芯片表面皲裂,有可能是那个环节出了问题?严重的芯片背面也裂。

A

顶针工位导致的可能性最大,检查蓝膜上顶针痕迹,看看是不是顶偏了,存在开始痕迹不明显,应用过程加剧,回流焊应力可以加剧恶化,可以抽样去做回流,然后复测一下,如果回流焊一片都没有发现,那就继续切片看下不同裂纹的走向,以及排查装配过程是否单板大的硬件,以及是否离螺钉位的距离,总之既要从材料生产过程排查,又要从应用层面出发

总结:关于芯片Die裂开这个问题,大概有这几种可能:

1. 芯片内部有应力,过高温炉加大了应力,导致裂开。

2. 客户高温炉温度设定超标。

3. Wafer的设计或者生产工艺不合理。

4. 曲线设计不合理(如温升、温降、保持)

Q2

有没有可以使用INCAL老化板做LTOL的资源?

A

如果金手指要插到INCAL机器里,国内应该没有,第三方实验室只有季丰有INCAL老化炉

Q3

LFBGA产品,球径0.4,pitch0.8,FT时对不良品进行3次复测,然后将若干枚失效样品放入袋子里混装寄出。拿到样品后,发现袋子里有脱落的锡球。这个锡球脱落正常吗?结合力有这么脆弱吗?哪个标准是验证ball的结合力的?

A

放在袋子里混装寄出的操作不太规范。如果怀疑结合力弱,可以做锡球推拉力实验。

参考标准:JESD22-B115A,JESD22-B117B

Q4

请教一下可靠性方面的专家,请问HTOL实验的样品数量是依据什么确定的?

A

参考文献:LTPD,JESD47

Q5

一般大家客户要求的抽检不良率会要求到多少PPM(非汽车电子)

A

1000-3000PPM,这边需求的标准指的是会写在采购框架合同上的,实际上千分之1-3确实可能比较高了,但是肯定是想给自己留buffer的。工业级这个标准要求还可以。

一般来说,客户报告的不良率会比真实不良率高很多。一个原因是因为基数可能太少。另外一个原因是因为客户会拿 fail芯片除以本次测试的数量,导致整体DPPM偏高。

Q6

DPPM在设计端和coverage强相关,其中数字coverage比较好统计,vwin coverage有什么方法或工具可以统计吗?

A

数字部分 存储部分 模拟部分 都要评估测试覆盖率,包括hard defect 还有soft defect(EFR need ATE DVS rescreen)

参考标准:J1752_3_201709

Q7

请教下相同测试项经过CP测试的,FT阶段出现很高比例的电性参数偏小失效,一般有什么可能情况?这个封装厂同期同封装其他型号无异常,而且此型号前期未出现此良率异常现象。有没有可能和wafer工艺或trim有关,此电压参数CP测试涉及trim。如果这个IC加热一段时间后,电压正常了,这一般是什么可能?

A

CP和FT数据不一致,主要原因是封装的电性影响和应力影响。至于具体原因还需要具体案例和数据才能分析,考虑下封装应力,取die出来再测下,当然还有其他因素。

如果是CP trim,然后FT在相同条件测试Post Trim结果,然后CP post trim 比FT post trim要小的话可以考虑看看是不是上面他们说的CP测试机台或者硬件问题导致CP测试结果实际上出现shift,但是从data 上看正常,结果到FT就反映出这个shift了。这个对比一下正常wafer和异常wafer批次的pre trim分布应该可以看出是否是这种情况。

建议CP测试完后bake 一下,模拟封装需要的bake,再来测试CP trim,验证是否是ft/CP测试差异。有遇到过fab 漏做一道工艺导致bandgap 电压trimming 后的电压ft 时发生变化

Q8

谁有了SRM转塔机测试如何防esd打坏芯片的规避方案吗。

A

ask handler vendor

Q9

请教下大家,relaxation effects指的是什么?

A

驰豫效应,简单点说就是从非平衡态恢复到平衡态的这个过程,内在计算挺复杂,参考半导体物理

Q10

请问 ‘Cosmetic package defects and degradation of lead finish’怎么理解?

A

这是HTSL JEDEC标准,外观缺陷和引脚电镀缺陷

Q11

请教一下关于EFUSE烧写fail的问题,在BI后我们在ATE测试的时候发现有3颗读EFUSE check的fail,分别fail在不同的block,都是0-1跳变。看了历史数据,测试过200K都没有这种fail,一般是什么原因?现在也没方向,到底是在老化阶段出现的误接触电源导致的二次烧写,还是ATE阶段被二次烧写?

A

嵌入式的EFUSE特别容易在ATPG等多个老化pattern运行及切换中发生变化。往往不是efuse问题。设计难以解释此现象,一般认为跟ATPG的随机现象相关。建议把其它pattern的老化和EFUSEpattern分开,做两次老化。也是一些公司的常用方法。

之前遇到一个一模一样的问题,解决方案可供参考:用的是UMC的EFUSE IP,做HTOL时发生EFUSE改写,最后分析出由scan pattern 引起的,你看看你的scan pattern 是不是电流较大,然后在BI过程中与其它电流较小的pattern是串在一起?这样切换时容易引起较大电流振荡,地上会不干净。另外,要研发看看scan pattern跑的过程中是不是会有一些逻辑电路有概率同时碰到EFUSE的power supply pin已经write enable pin。我们当时看过,约有40万分之一的概率会导致改写,所以如果不停跑scan pattern可能每隔150小时有机会出来一个fail。当然终极原因是UMC的IP的设计冗余不够。

Q12

有什么的好的方法,可以满足bHAST的正常试验,从外界材料上面?或者考虑电压周期性拉偏,应该怎么样去拉偏?

A

bHAST只是做直流拉偏,是在相邻管脚加上正负电压,以形成电势差。但是设计只允许拉高或拉低的管脚除外,比如电源和地等。不跑pattern。参考jedec规范的注解。

因为条件的问题,普通的FR4材料往往因为材料密度疏松,引起楼电,严格的公司固定bHAST不能用bHAST板材。这会增加PCB成本,但是真正的可靠性工程师应该包容这个成本。

编辑:jq

-

芯片

+关注

关注

455文章

50711浏览量

423104 -

pcb

+关注

关注

4318文章

23079浏览量

397434 -

IC

+关注

关注

36文章

5944浏览量

175468 -

机器

+关注

关注

0文章

780浏览量

40710

原文标题:季丰电子IC运营工程技术知乎 – 21W48

文章出处:【微信号:zzz9970814,微信公众号:上海季丰电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

成都季丰获批CNAS实验室认可证书

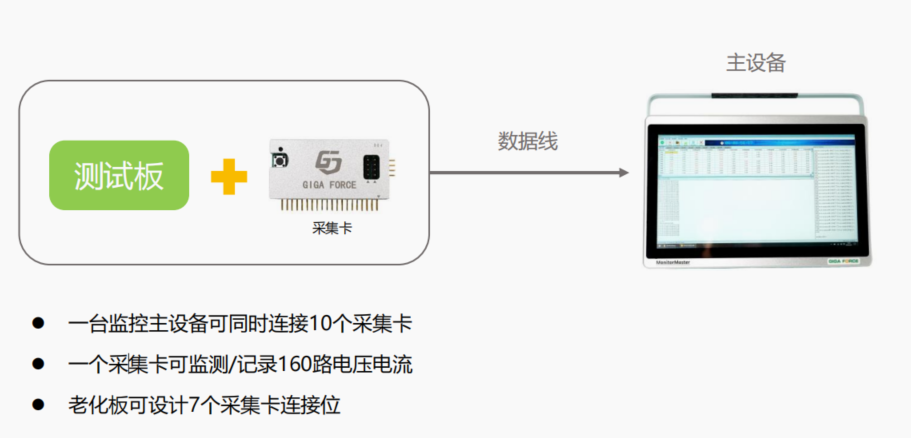

季丰电子MonitorMaster系统在BHAST实验中的应用

衢州季丰获得CMA扩项资质认定证书

2024季丰电子技术交流研讨会深圳站圆满结束

衢州季丰获得CNAS扩项认证

杭州季丰成功获得CNAS认可证书

季丰电子与数字电源设计公司华源智信携手建立联合实验室

季丰电子成功通过IECQ换证审核

珠海中京电子成功获得“广东省电子电路工程技术研究中心”认定

季丰电子IC运营工程技术快问快答03

季丰电子IC运营工程技术快问快答03

评论