Q1

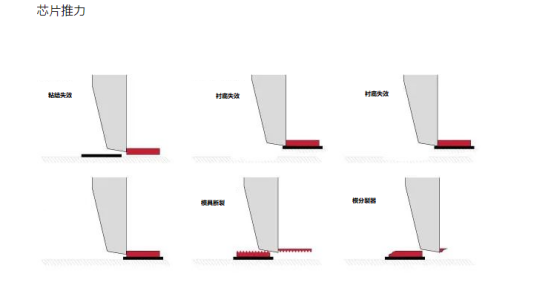

请教一下各位大侠,一般芯片增加CP测试之后,可靠性需要重新评估么?评估哪些内容?

一般是这样子,大公司CP都要评估的,如果是新process,那CP部门要做DOE,防止die crack等,但是如果是已经released的,连DOE也不用做。可靠性就更不必谈了,除非是发生了问题,并且确认是CP引起的,可能需要讨论做一些可靠性与FA。

Q2

谁有jesd22-a104e这个版本的标准,可以分享下吗?

Q3

有人知道IMC层怎么观察吗?行业内有规范吗?季丰对IMC有没有相关的DPA标准?

WB站会用显微镜和软件染色来看面积,可靠性后我们会做下Cross-section看IMC生长

Q4

各位大佬,有没有扫分层的SAT资料分享一下呀?

超声波扫描显微镜Sonoscan D9650,

老炼前后的对比照片,老炼后焊球的压痕还算正常吗?

如果目的是筛选的就会出货一般都是100%,目的是寿命的不出货一般是samples。

Q6

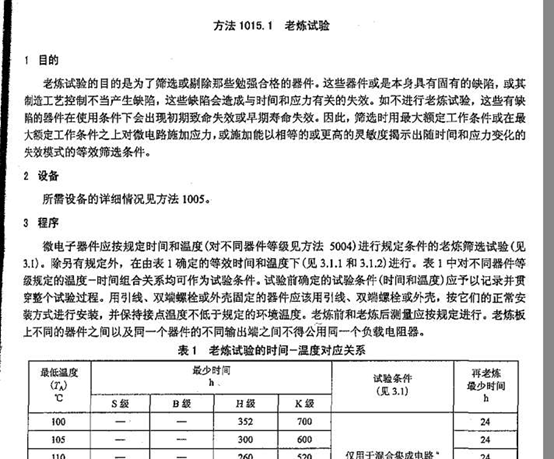

什么是老炼?

国军标叫老炼,就是寿命实验的意思,就是加应力加速失效的过程。比如THB,ELFR,HTSL,TC,HTOL,……

Q7

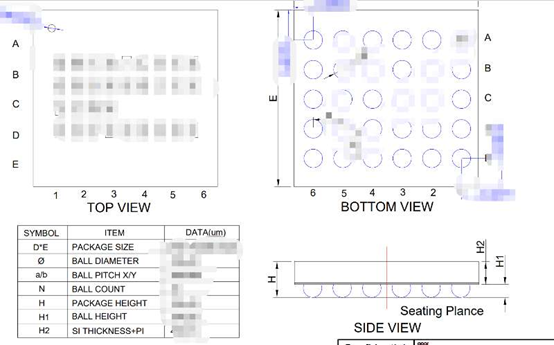

请问大家,WLCSP的 solder ball 下有passivation crack的问题,调整什么参数会有明显改善,例如可以通过更高次数的TC, solder ball 本身没有问题,这个是WLCSP封装,有RDL的。

加underfill一般会有帮助,但也不是所以情况都可以加。UF分CUF和MUF,CUF在很多位置没有solder ball的情况下,即有大面积空位的情况下UF材料毛细效应弱,流不过去,会有空洞,这样加UF适得其反;MUF要看这颗IC周围是不是适合做molding,周围的器件要不要一起mold起来,有些时候限制太多MUF就不可能了,即使可以做MUF,你也要开模具,增加一道工序,甚至要做热仿真。passivation crack 的话最好有crack位置的照片和量测数据,还有repassivation的材料和厚度,它下面RDL trace处的台阶高度,RDL trace宽度和间距等,这些信息可以帮助判断原因和提改进方法。其实这些都有design rule,逐一排查一下吧

Q8

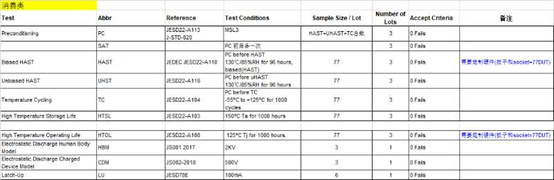

咨询一下,对于消费类电子,一般会做哪些可靠性项目?

IC类:

pkg-qual:precon, HTSL, TC, uHAST, bHAST,

product-qual:ESD(IBM.CDM), LU, HTOL

可以多做,不少做

Q9

pkg qual与product qual的区别是?

Pkg qual是面向封装,Product Qual是面向产品(芯片本身的设计和工艺)

Q10

那product qual就不需要做precon, HTSL, TC, uHAST, bHAST实验了么?

如果只改了芯片设计,别的都没动,可以不做。

Q11

再咨询一下,这些rule适用于所有消费类IC产品嘛?比如IC+MOS,这样的ACDC产品,是否也适用于该可靠性rule?

一般性适用,实际分具体情况。比如,如果是NVM往往要看data retention之类。

Q12

1000hrs,1000cycles,这些时间或者周期可以缩短嘛?

可以啊,等效时间不同。大致意思是,可靠性实验是以加压的方式vwin 自然(典型)时间条件,加速时间和典型时间会有个换算关系,比如你看到的1000hrs等效为10年,而你的产品不必保那么久,自然可以少做点。

Q13

各位大神,请教下,中测trim过的,到成品测试恢复到熔丝前了,这一般有哪些情况?trim过有烧断痕迹的,开盖后探针测试没有阻值,没有熔断。

建议先看看成品熔丝恢复的情况再做推断,通常现象是成品熔丝有细微裂缝,但是连通电路,这就可能是wt熔断的冗余度不够,在封装时受到挤压连上了,再去看wafer的熔断情况,仅供参考。

Q14

请教诸位个问题啊,汽车电子AECQ100中的常温、高温、低温FT测试,业界一般都怎么做呀?如果用热流罩的话,测试效率太低了,有没有啥别的好的办法呢?

三温handler,可以编程设计。

Q15

请教各位大佬, 固态硬盘BGA颗粒和PCB焊接有很多气泡,影响和主要改善方向有哪些?(怀疑是baseline问题)

我们出现过类似的问题,问题原因是:Flux没按固定存放。

Q16

咨询一个问题,工业上的IC,一般MSL是要求几的?

伺服驱动器上用的IC是MSL2或MSL1,分立器件用的都是MSL1。

Q17

请问一下,在做HBM时,芯片的测试条件是所有管脚都需要上1.1倍的设计工作电压呢,还是按照设计时使用的ESD管子的最大电压来做?

HBM芯片不用上电的,latch up电源管脚才说上电的,IO管脚是电流。

原文标题:季丰电子IC运营工程技术知乎 – 21W50

文章出处:【微信公众号:上海季丰电子】欢迎添加关注!文章转载请注明出处。

-

芯片

+关注

关注

455文章

50711浏览量

423104 -

软件

+关注

关注

69文章

4921浏览量

87383 -

显微镜

+关注

关注

0文章

558浏览量

23019

原文标题:季丰电子IC运营工程技术知乎 – 21W50

文章出处:【微信号:zzz9970814,微信公众号:上海季丰电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CP测试与FT测试有什么区别

tlv320aic3254evm-m评估板进行测试,测试过程中烧录了内部程序后就无法识别了,为什么?

半导体制造的关键环节:芯片测试

芯片增加CP测试之后需要重新评估么

芯片增加CP测试之后需要重新评估么

评论