1、参考https://forums.xilinx.com/t5/%E5%B5%8C%E5%85%A5%E5%BC%8F-%E7%A1%AC%E4%BB...

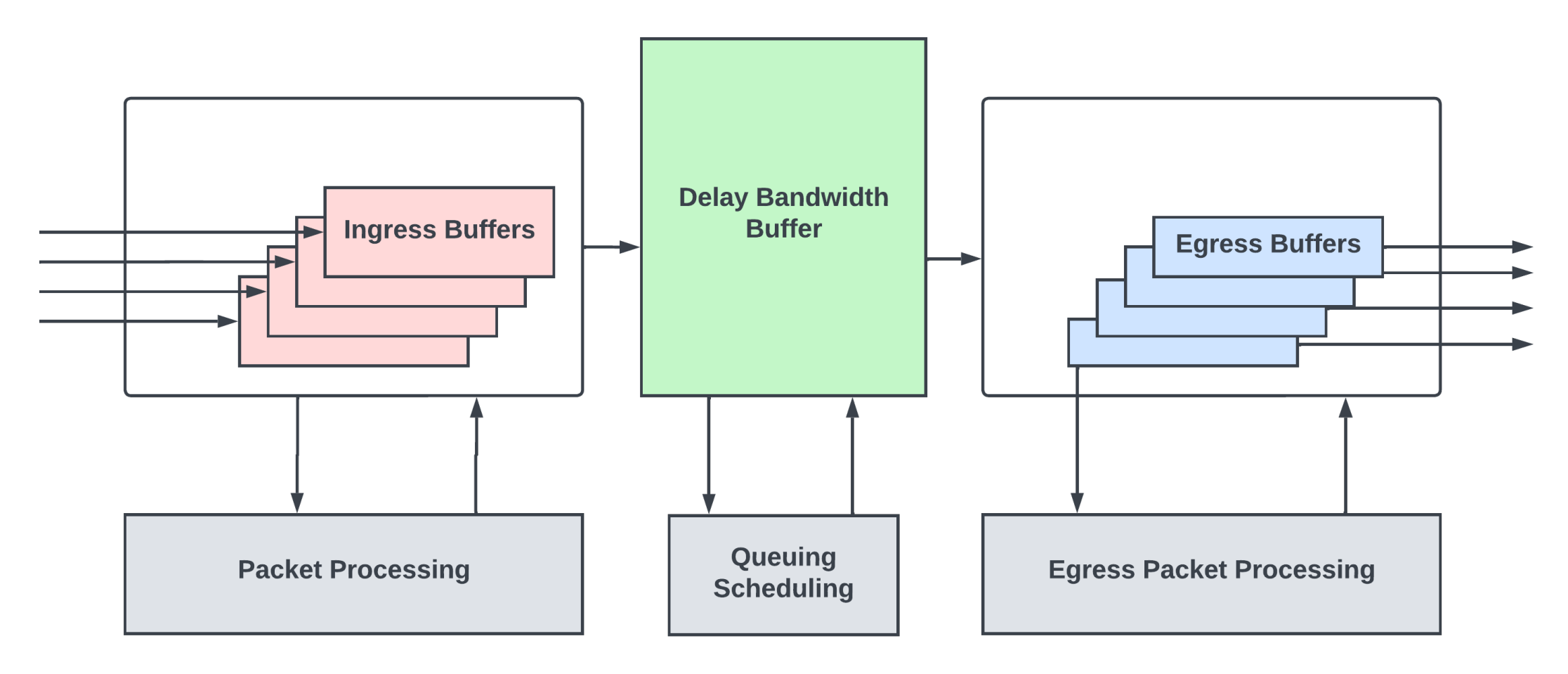

按照官方说明,copy数据速率基本为系统ddr的带宽。

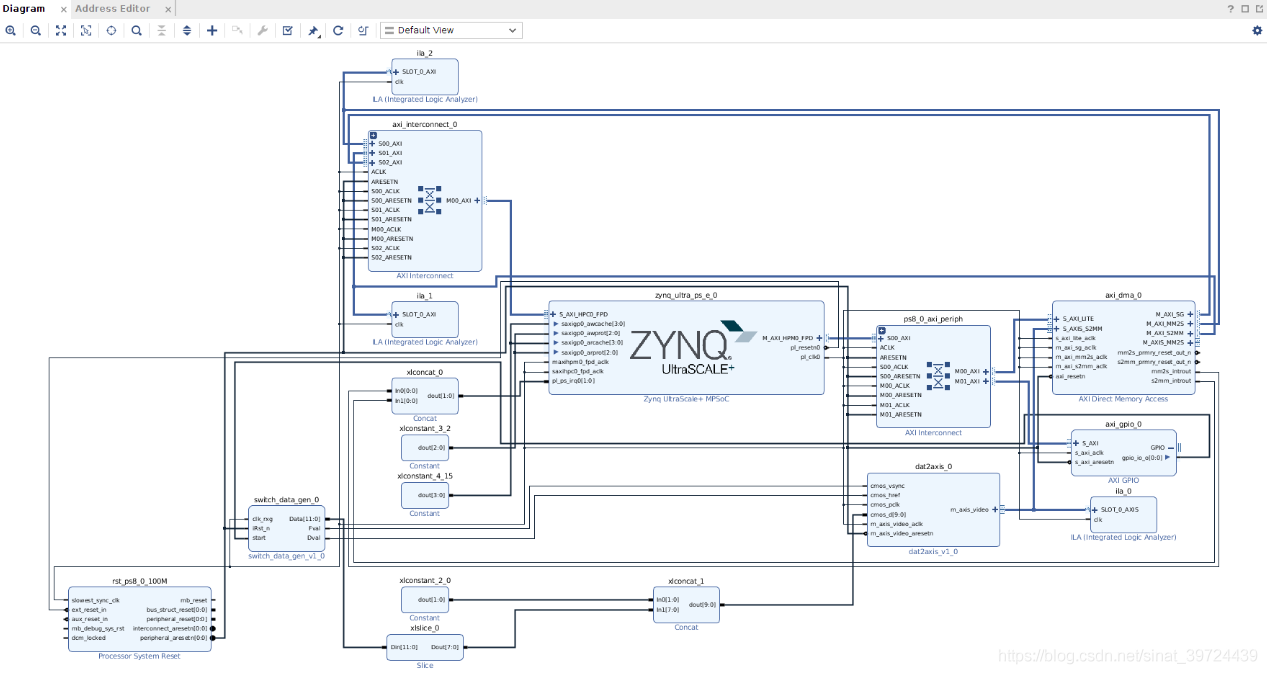

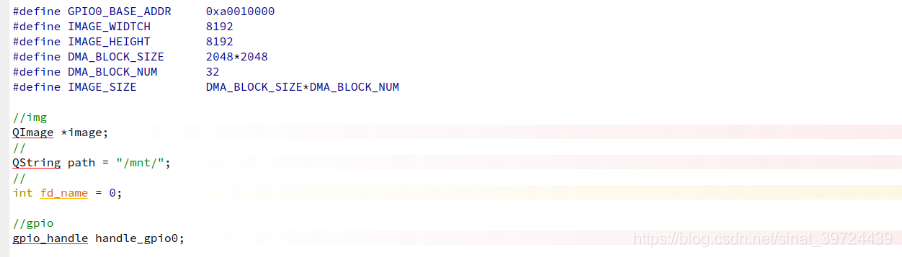

2、工程 生成数据大小2048X2048 4MB 也就是一次dma数据大小,一次dma数据的大小与axi-dma核中buffer lenght registr有关,长度最大26,也就是2^26个字节,为64MB,工程中加入ila核用来调试。

3、生成bit后,导出xsa文件。

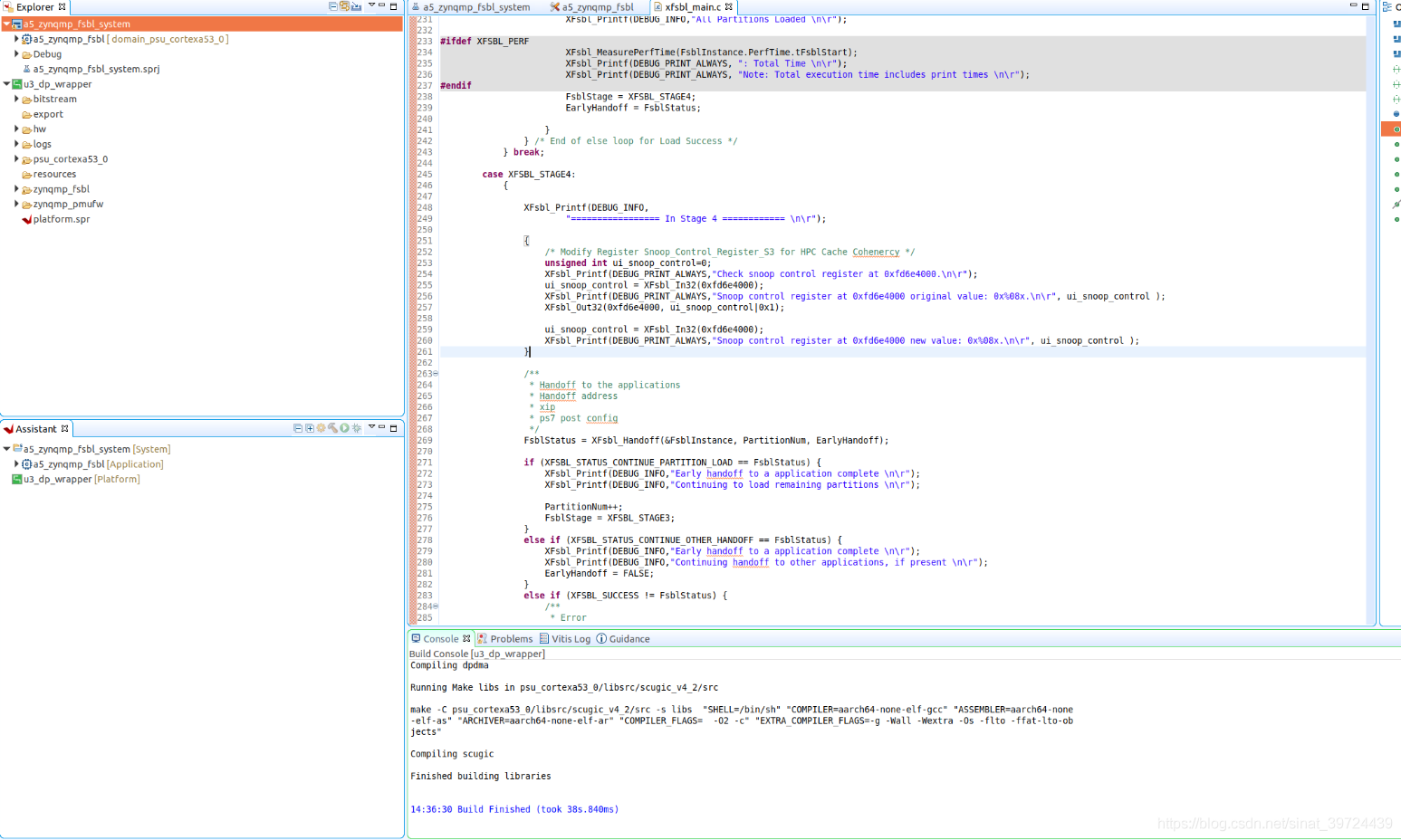

4、在vitis中应用xsa文件,新建a5_zynqmp_fsbl工程,按照官方说明,修改sfsbl_main.c,并编译,在debug文件夹中可以找到a5_zynqmp_fsbl.elf文件。

5、在petalinux环境中新建工程,参考以前的博客,直到petalinux-build。

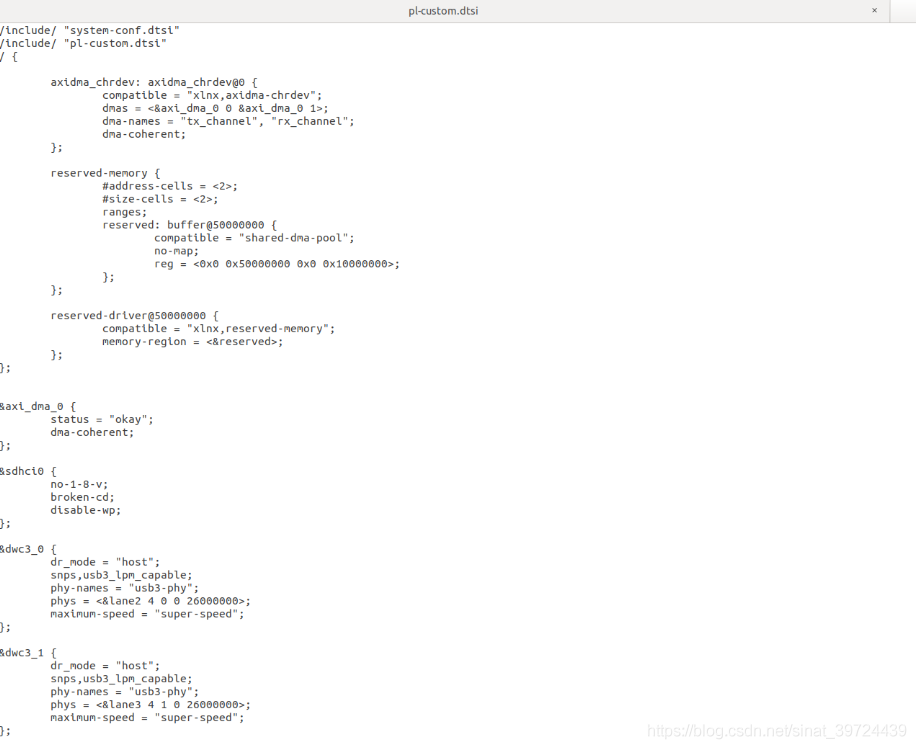

6、修改设备树

7、重新petalinux-build。

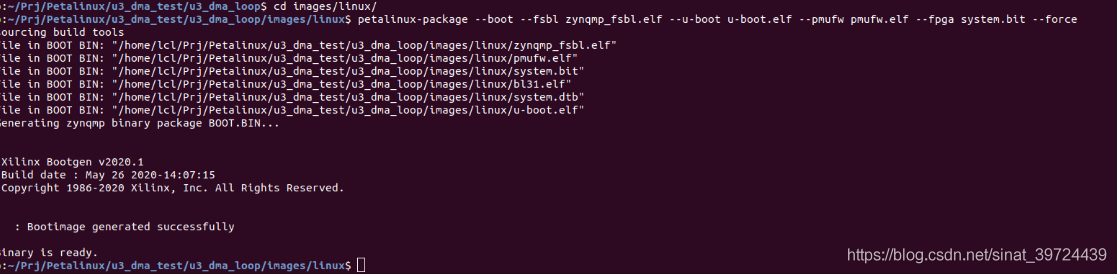

8、在image/linux文件夹下

9、拷贝出bl31.elf boot.scr image.ub pmufw.elf system.bit system.dtb u-boot.elf 七个文件,以及vitis中生成的a5_zynqmp_fsbl.elf共8个文件,到linux_dma_test.

10、在petalinux工程中,build文件夹中拷贝bootgen.bif文件,并修改成如下

11、新建regs.init

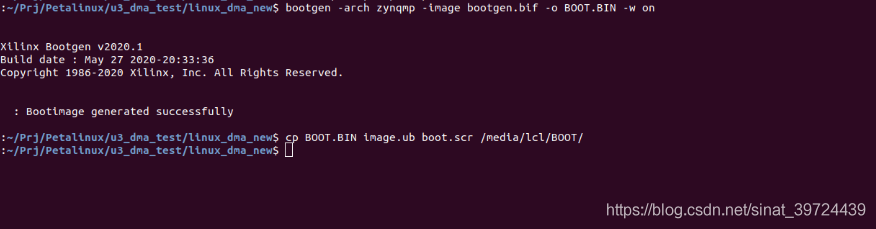

12、生成BOOT.BIN,然后一起将BOOT.BIN image.ub和boot.scr复制到sd卡。

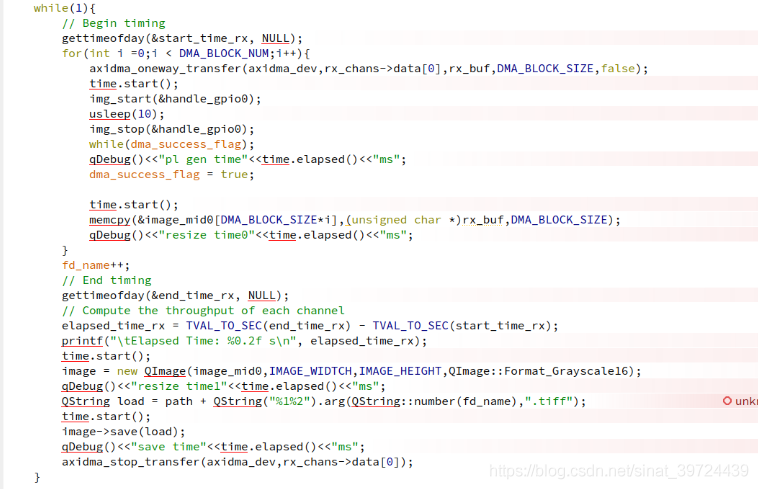

13、测试

14、上电开机,加载axi-dma的驱动,将3.0U盘挂在到mnt下

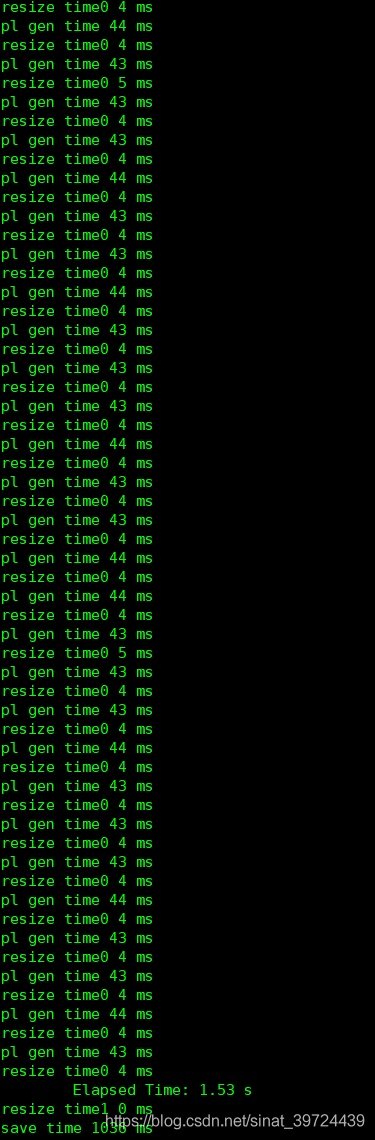

由以上可以看出,pl生成一张4MB的数据耗时43ms,将4MB数据由dma读缓冲区copy到内核缓冲区耗时4ms,基本接近ddr的带宽。整个链路中的带宽完全受限于U盘的存储速度。

15、U盘中的图片,大小128MB,数据正确。

审核编辑:符乾江

-

文件

+关注

关注

1文章

565浏览量

24727 -

编译

+关注

关注

0文章

657浏览量

32852

发布评论请先 登录

相关推荐

单片机中的几种环形缓冲区的分析和实现

ESP8266有双缓冲区吗?

创建DMA通道时,能否将DMA缓冲区的大小指定为8字节,并将DMA缓冲区的编号指定为1?

如何确保在负载量小于或大于DMA缓冲区大小的情况下完全提交数据?

FX3多通道DMA在切换DMA缓冲区时仍会丢失数据,为什么?

stm32野火开发板上做USB通信,PC端USB的缓冲区和串口缓冲区的大小是多少?

交换机与路由器缓冲区:寻找完美大小

Petalinux加速axi-dma内核驱动缓冲区读过程

Petalinux加速axi-dma内核驱动缓冲区读过程

评论