缓冲放大器作为一种特殊的电路,虽然以运算放大器为核心组成,但多用于隔离、阻抗匹配、增强电路输出能力,反而不太注重放大能力。此前的缓冲放大器,大多基于FET输入放大器的分立式方案,需要数十个分立元件,诸如场效应晶体管、保护二极管和晶体管。这种设计下的缓冲放大器,一来成本高,二来系统复杂,还无法提供与ASIC相同的带宽,大大限制了信号吞吐量。

为了解决此类问题,TI在不久前发布了具有业界超宽带宽的高输入阻抗(Hi-Z)缓冲放大器BUF802。BUF802 3.1GHz的大信号带宽以及7000V/µs的压摆率能实现更高的信号吞吐量并大幅缩短输入稳定时间。

(图源:TI,下同)

作为业界领先的放大器厂商,TI BUF802的单芯片缓冲放大器方案发布后引得了不少关注,为了探究BUF802背后的技术特点,电子发烧友网就相关技术问题与德州仪器(TI)高速运算放大器系统工程主管Shreenidhi Patil进行了交流。

复合环路友好型架构提升设计简易性

BUF802的单芯片缓冲放大器方案最主要的特点在于其设计简易性。从下图中可见,由精密环路和高速环路组成的复合环路要求对每个单独的环路进行补偿和匹配。BUF802采用创新的复合环路友好型架构,简化了多环路的设计和补偿。在复合环路中,该器件能够在需要1µV/℃最大温漂的应用中实现高直流精度和3GHz带宽。

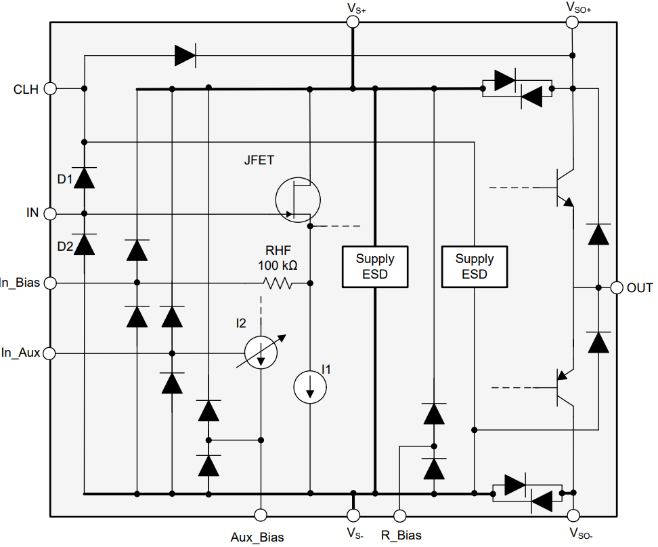

对于任何缓冲放大器来说,实现复合循环架构最大的限制来自低频和高频路径之间的相互依赖性。据Shreenidhi Patil介绍,为了克服这一限制,BUF802可解耦低频和高频路径之间的相互依赖性(如下图所示)。这使得设计人员能够独立设计低频和高频路径,从而简化这两条路径的补偿和匹配。

低频和高频路径的解耦使设计人员能够将交叉区域推到更高的频率,从而实现更好的过载恢复、更低的噪声和更小的元件尺寸。BUF802将来自精密放大器的低频电压信号转换为等效电流,然后用来改变主JFET(结型场效应晶体管)的偏置。这种架构将低频信号添加到高频信号中,而不会在两条路径之间产生任何闭合环路或正反馈。

增强电路过载恢复与ESD保护

在某些测量应用中,虽然不少半导体制造商提供的缓冲放大器具有低偏置和输入偏置电流,但配上传感器电缆仍然可能会因为ESD(静电放电)对放大电路造成损害。同时,器件可能进入从输入或输出过度驱动导致的饱和状态中,这同样会对器件造成损害。

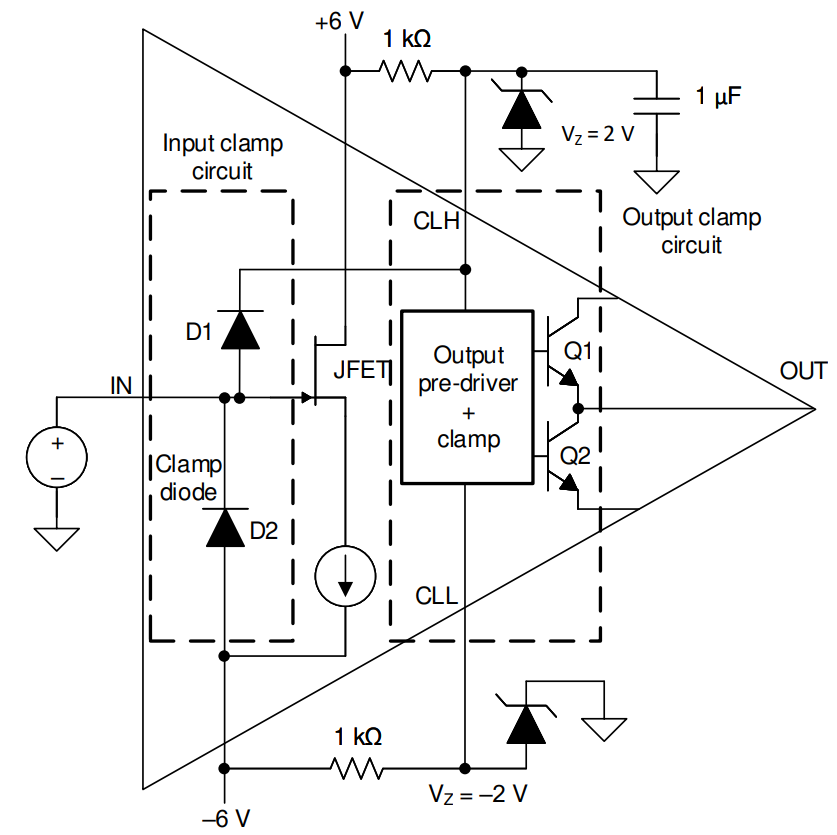

ESD对于放大电路的损害主要从结构和二极管上来解决,如下图。图中的D1和D2二极管能够承受100 mA的连续电流,从而使电路设计人员能够保护IN引脚免受任何ESD冲击以及高压瞬变的影响。

BUF802加入了输出保护电路来确认快速的过载回复,施加在CLH和CLL以及内部电压节点上的电压可以确保输出端的晶体管不会硬饱和。但为了达到快速恢复的效果,BUF802牺牲了轨到轨输出的实现。Shreenidhi Patil也表示,对于这种取舍,还是要视具体应用而定,例如在AFE中,高达4 Vpp的输入和输出电压范围已经可以满足大多数用例的需求,也极大地降低BUF802无法实现轨到轨输入及输出的影响。

添加缓冲器时如何保证精度与性能?

在了解了高阻抗缓冲器业界领先性能背后的技术特点后,Shreenidhi Patil以BUF802为例介绍了如何在给系统添加缓冲器时候保证性能。就BUF802来说,其2.8 nV /sqHz的噪声系数和大于50 dB THD @ 1 GHz的总谐波失真,可确保与任何高带宽AFE信号链一起使用。复合环路中的直流精度则由精密放大器决定,因此设计人员可以通过选择合适的精密放大器来轻松选择直流精度。

高阻抗缓冲器能够输入帮助设计人员将现有的AFE转换为高输入阻抗AFE。在这些设计中,确保原始信号链的SNR和THD不会因在输入端添加缓冲器而降低非常重要。为了保证给系统添加缓冲器不影响精度和性能,缓冲器本身自身的噪声和失真性能应该要远远优于AFE信号链。

-

ti

+关注

关注

112文章

8064浏览量

212354 -

ASIC技术

+关注

关注

0文章

19浏览量

7575 -

高输入阻抗

+关注

关注

0文章

5浏览量

9316

发布评论请先 登录

相关推荐

共源共栅放大器的优缺点是什么

请问仪表放大器的带宽为什么只有几MHz?

缓冲放大器的几种类型介绍

什么是缓冲放大器

缓冲放大器的工作原理和优点

TI技术专访:挖掘高带宽高阻抗缓冲放大器背后的特色技术设计

TI技术专访:挖掘高带宽高阻抗缓冲放大器背后的特色技术设计

评论