没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

同步和异步复位

在ASIC/FPGA设计中,何时使用异步复位或同步复位总是导致设计者头脑混乱。同步复位信号在时钟边缘和数据路径的一部分进行采样,而异步复位信号的采样与时钟信号无关,而与数据路径或数据输入逻辑的一部分无关。本节介绍使用异步和同步复位的Verilog RTL for 触发器。

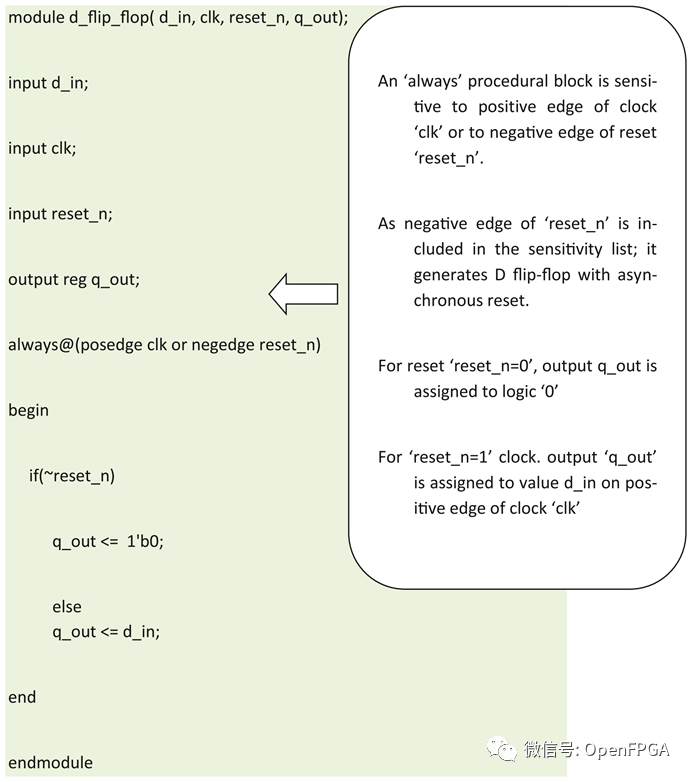

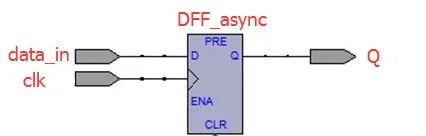

D触发器异步复位

异步复位不是数据路径的一部分,用于初始化触发器,而不考虑时钟边沿,因此称为异步复位。这种初始化触发器的技术不推荐用于生成内部复位信号,因为它容易出现故障。设计者需要注意在内部同步该复位信号,以避免出现故障。内部同步复位信号应用于存储元件。复位解除(reset deassertion)是异步复位信号的主要问题,采用两级同步器可以克服这一问题。两级同步器(Level synchronizer)避免了复位解除期间的绕线情况。

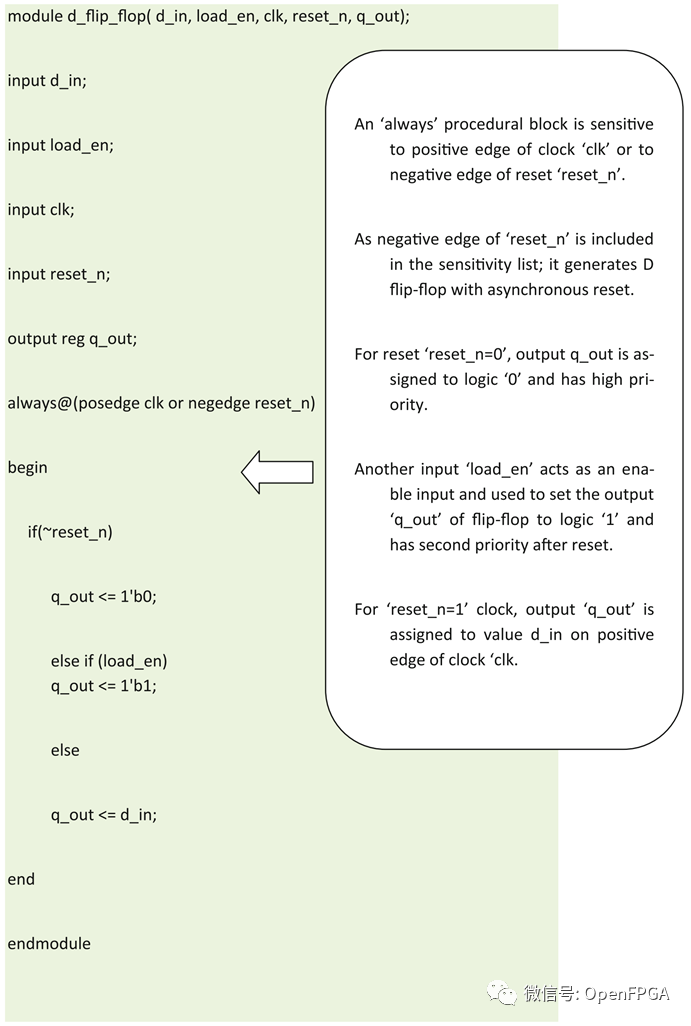

Verilog RTL如图所示,使用低电平异步复位信号“reset_n”(示例5.3)。

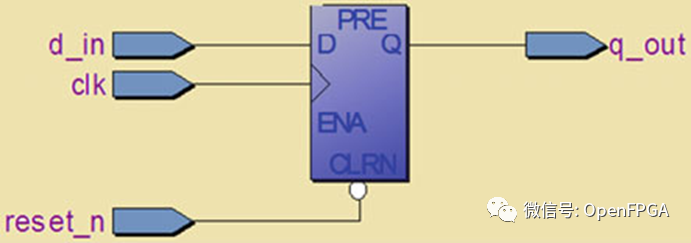

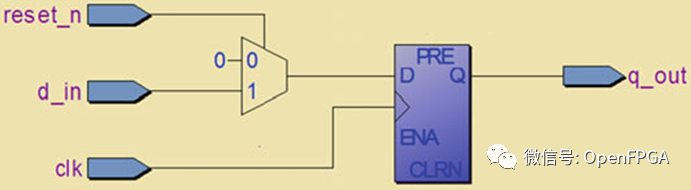

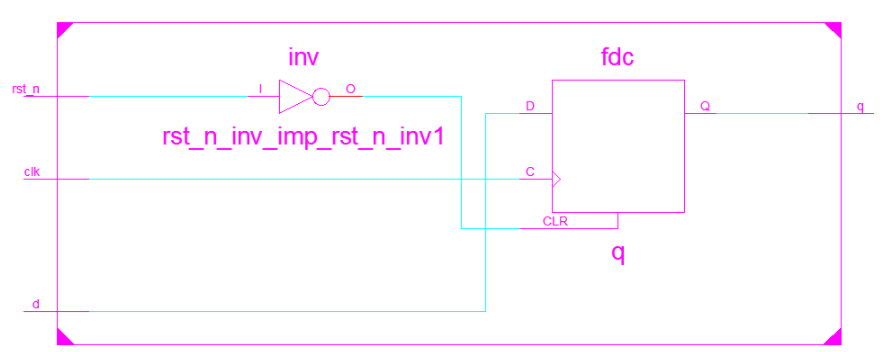

图5.10显示了具有异步复位“reset_n”的D触发器的综合逻辑。

示例5.3 D触发器,带低电平异步复位信号“reset_n”输入

图5.10 带低电平异步复位信号输入的综合D触发器

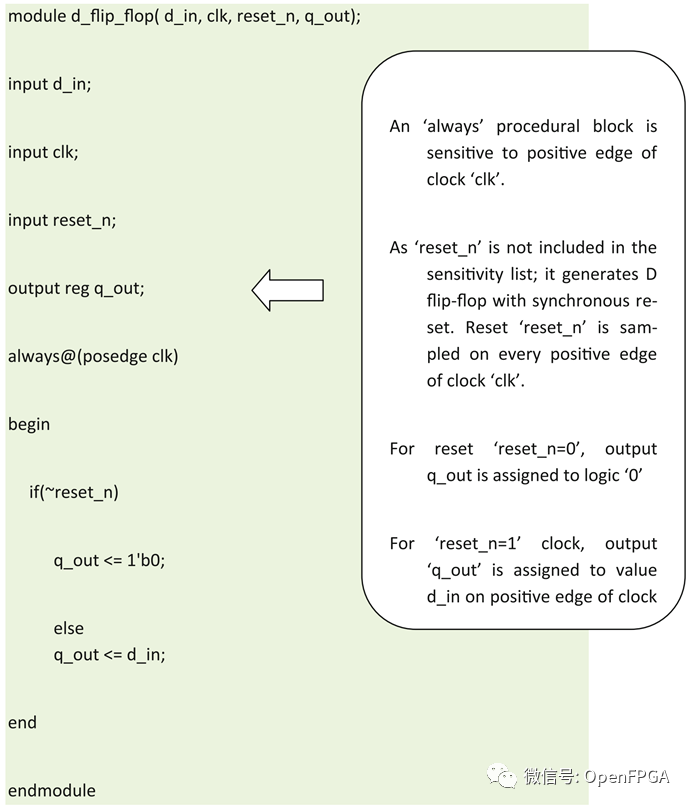

D触发器同步复位

在同步复位中,复位信号是作为数据路径的数据输入的一部分,取决于活动时钟边沿。同步复位不存在故障或危险(glitches or hazards)问题,因此这种方法最适合设计。该机制不需要额外的同步电路。

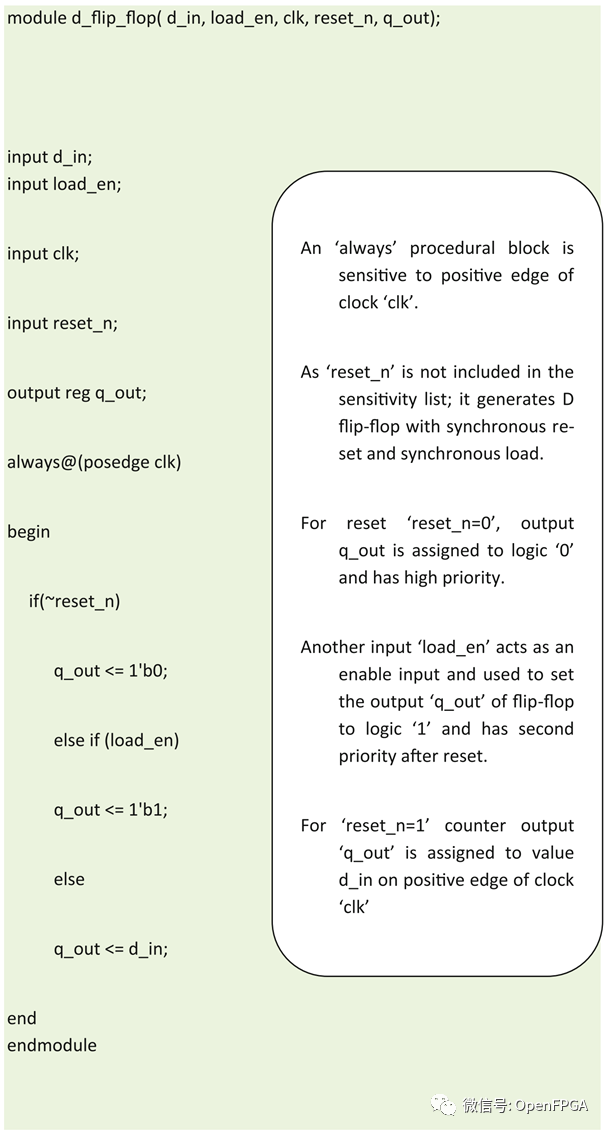

例5.4中描述了Verilog RTL,它使用低电平同步复位信号“reset_n”。

示例5.4 D触发器,带有源低同步复位输入

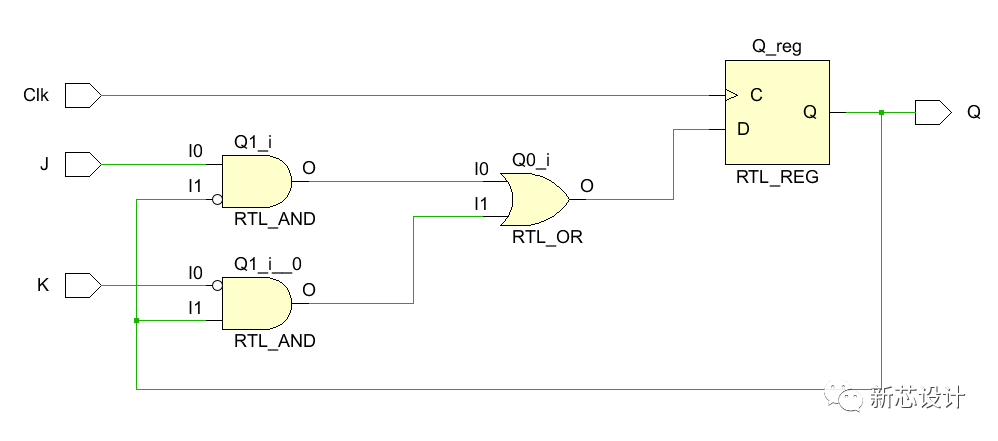

图5.11同步复位D触发器的综合逻辑

带同步复位输入的正边沿触发D触发器的综合逻辑如图5.11所示。

带使能异步复位的触发器

在大多数实际应用中,需要多个异步输入。考虑一个应用程序,当激活输入时,它需要加载输入数据。即使在复位信号激活且有效时,也必须等待初始化寄存器。如果两个异步输入同时到达,则输出应取决于这些信号的优先级分配。

如示例5.5所示,两个异步输入被命名为“reset_n”和“load_en”。“ reset_n”具有最高优先级,“load_en”具有最低优先级。使用“if-else”构造优先级。

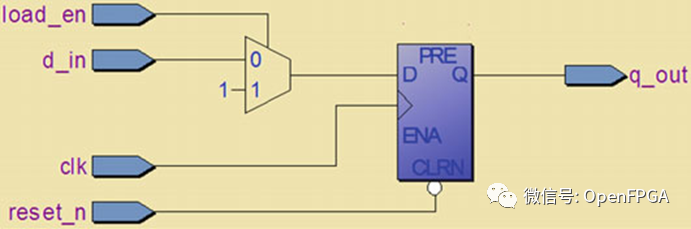

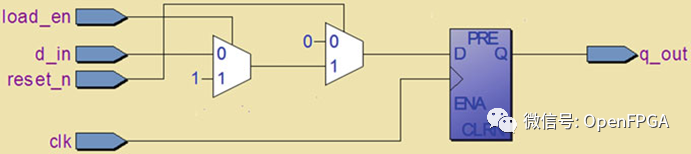

综合逻辑如图5.12所示。

示例5.5带异步“reset_n”和“load_en”的D触发器的Verilog RTL

图5.12异步复位D触发器的综合输出

带使能同步复位的触发器

如果多个信号或输入是数据路径的一部分,并且在时钟的活动边沿上采样,则在时钟的活动边缘上分配时序单元的输出。考虑示例5.6中所示的Verilog RTL,输入“reset_n”和“load_en”是同步输入并在时钟的正边上采样。同步输入“reset_n”具有最高优先级,“load_en”具有最低优先级。

综合逻辑如图5.13所示,“reset_n”和“load_en”是数据路径的一部分。

示例5.6带同步“reset_n”和“load_en”的D触发器

图5.13带同步“reset_n”和“load_en”的综合逻辑

审核编辑:郭婷

-

FPGA

+关注

关注

1628文章

21728浏览量

602949 -

asic

+关注

关注

34文章

1199浏览量

120428 -

触发器

+关注

关注

14文章

2000浏览量

61129

原文标题:Verilog时序逻辑硬件建模设计(二)同步和异步复位

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

verilog描述异步置0,异步置1功能的D触发器

同步复位和异步复位的比较(转载)

FPGA的复位设计分析(Verilog HDL与RTL图)

D触发器中PRN与CLRN区别在哪

异步复位信号亚稳态的原因与D触发器的Verilog描述

Verilog RTL和触发器中的同步和异步复位功能分析

Verilog RTL和触发器中的同步和异步复位功能分析

评论