全球数据量仍然处于持续的爆炸式增长当中,不仅现有的应用对数据的生成量快速增加,新的应用领域如人工智能/机器学习(AI/ML)等,也都在不断生成更多的数据。同时,数据中心也必须要有完善的架构和基础设施来支持如此庞大数据量的传输以及存储。在中国,数据中心市场整体发展得还是非常迅速的,而且每年都有非常大幅的增长和提升。近期,中国还提出了“东数西算”工程,数据中心的发展迎来政策利好。

随着数据总量继续大幅爆炸式增长,数据中心正在采用新的计算模式,如分解式计算(Disaggregated Computing)或者可组合式计算(Composable Computing),这也要求同时保证数据传输速率的提升和数据传输的安全性。

Rambus在数据中心及其细分市场的收入占比达到75%以上,做为数据中心高速互连方案的芯片及IP供应商,Rambus始终站在技术和市场的前沿。最近,Rambus发布了全新的PCIe 6.0控制器IP。Rambus战略营销副总裁Matt Jones,和大中华区总经理苏雷在媒体交流会中对这项新技术、新品和应用前景进行了详细的解读。

PCIe6调制信号重大变化:从NRZ到PAM4

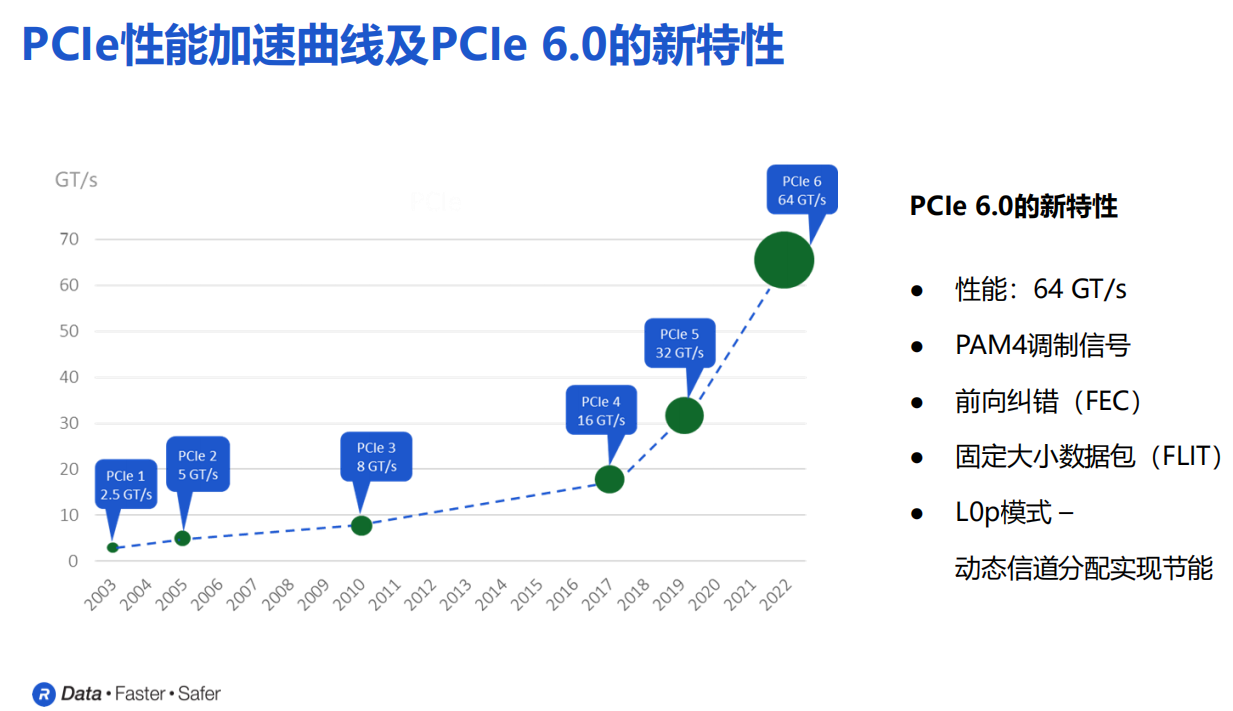

自21世纪初PCIe标准正式创立以来,它就已经成为数据中心和计算应用中芯片间数据传输的行业标准。今年1月份,PCIe 6.0的相关规范正式出台,标志着我们进入PCIe 6.0时代。

PCIe 每次的技术迭代,数据传输速率的性能指标基本上都是翻倍的。PCIe 1.0和2.0时代,理论数据传输率大概是2.5和5GT/s,但考虑到具体采用的编码技术和信号传导模式,实际的数据传输速率大概是2和4GT/s。到现在的PCIe 6.0速率高达64GT/s。

为了更好地在PCIe技术规范之下实现64GT/s的数据传输速率,并克服整个通道传输长度以及距离的限制,新规范采用了全新的PAM4调制信号,也就是四电平脉冲幅度调制。

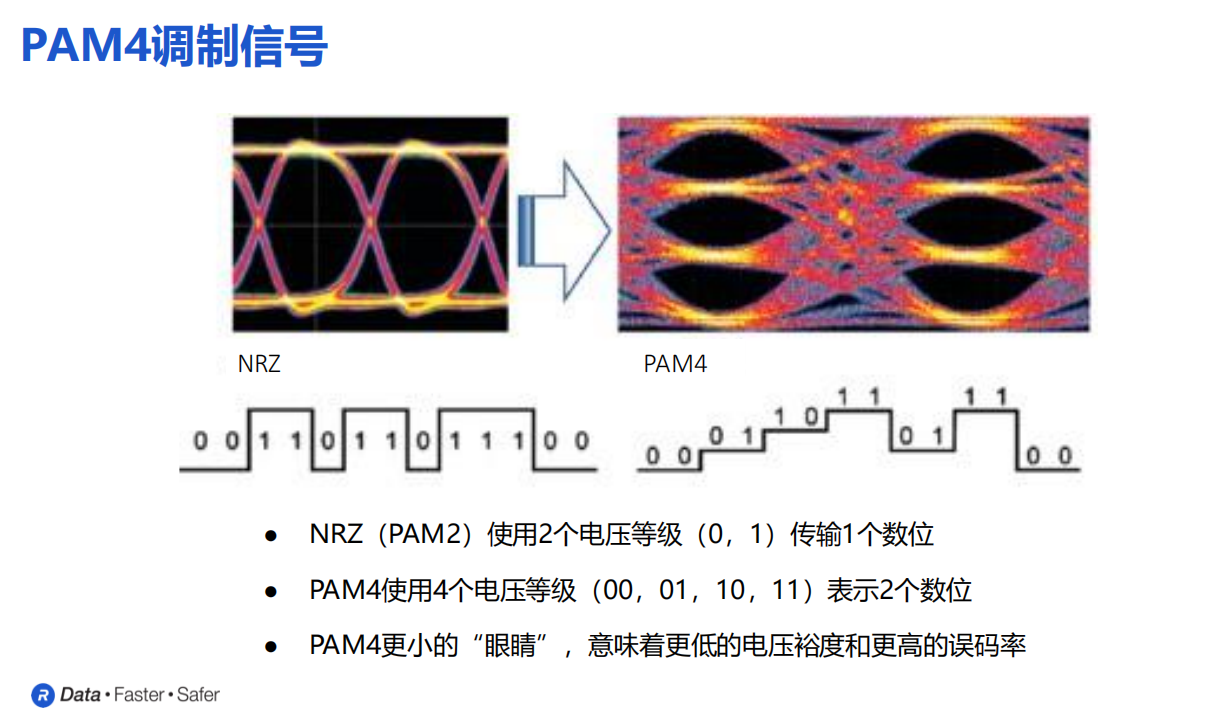

Rambus高管具体分析道,在PCIe 6.0之前,各代PCIe采用的都是NRZ调制信号,即不归零编码,它采用0或1两个电压等级,每一个时钟周期只能传输1bit的信号。也就是说,它只采用了高低两种信号电平。因此,相对于PAM4采用的四电平,我们也将NRZ称作PAM2 。

为了实现高达64GT/s的数据传输速率,PCIe 6.0采用PAM4调制信号。通过PAM4,每个时钟周期的数据传输可以达到2bit,而并不仅仅是单bit的数据传输。PAM4采用四个不同的电平等级,在每个时钟周期表达2个数位,从00、01、10再到11,这就意味着在同样的电压波动范围之内和同样的时钟周期内,由于PAM4的电压等级比PAM2高了两个,即眼图中黑色的区域“眼睛“这个部分更多、更小了。这种变化带来了另外两个重要的影响,即更低的电压裕度和更高的误码率,使得在设备中保证信号完整性成为了一个非常关键的难题。

进一步来说,考虑到PAM4要确保PCIe 6.0达到64GT/s数据传输速率,需要在保持数据传输速率的前提下解决PAM4本身的问题。为此,PCIe6.0采用了前向纠错技术(FEC)。 FEC本质上是一种算法技术,可以在数据传输链路中确保所有信号的完整性。

同时,FEC技术的采纳还改变了数据流控制单元的情况,要求我们也必须针对数据包本身的大小做出调整和改变。在PCIe6.0之前的几代规范,包括PCIe5.0、3.0等,采用的是可变大小的数据包;但由于FEC技术的采纳,PCIe 6.0必须采用固定大小数据包(FLIT),以更好地保证FEC技术的实现和操作。

数据传输速率的上升以及PAM4这项技术本身带来了另一个问题,即设备的能耗可能会上升,每一比特数据传输造成的单位数据能耗也会增加。为了减少整体系统的能耗,PCIe 6.0采用了颠覆式的L0p模式,其本质是通过动态的信道分配,允许将每个通道进行封闭或者打开来实现系统性的节能。

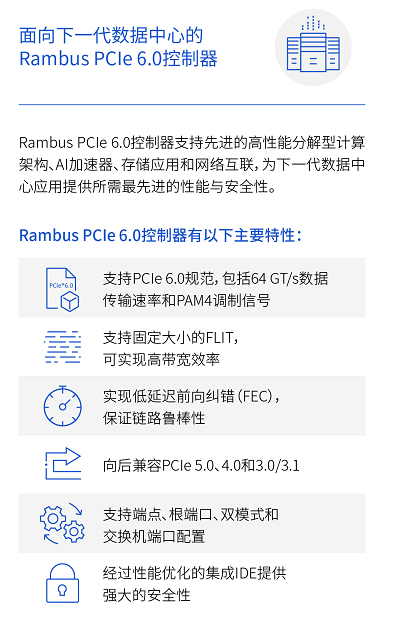

Rambus的PCIe 6.0控制器不仅数据传输速率高达64GT/s,更重要的一点是,该控制器还集成了完整性和数据加密(IDE)引擎,可以实现数据在不同PCIe设备的PCIe通路之间的安全传输。

Rambus PCIe 6.0控制器在功耗、面积以及延迟上都特别进行了相应的优化,特别在降低能耗方面,以帮助确保PCIe6.0成为数据中心解决方案的一块关键基石,进而推动环保型数据中心的建设,并减少对散热管理的需求,降低拥有成本。

同时,Rambus的PCIe 6.0控制器非常灵活,可以适用于PCIe端点、根端口、双模式和交换机端口配置。

与客户合作推进系统级芯片和PCIe6.0方案,助力“东数西算”工程

现在,Rambus 向中国市场正式发布Rambus PCIe 6.0控制器,同时以超过400个PCIe控制器的成功生产流片为基础,再次扩大了Rambus在PCI Express IP授权领域的领导地位。

Rambus高管表示,RambusPCIe6.0控制器目前已经可以量产,是以RTL的提供软性IP,然后将其合成到客户的设计中。因此它可以跨越许多工艺节点,并具有设计上的灵活性,能够处理跨许多代工厂解决方案和工艺节点的时序收敛和集成,不必局限于任何一个制造代工厂或工艺节点。我们已与领先的客户合作,使用我们的控制器产品开发系统级芯片和PCIe6.0解决方案。这些解决方案的开发和制造周期大概需要3年,也就是2025年左右进入市场。

去年,Rambus发布CXL内存互连计划,推出了一系列面向数据中心的新的解决方案,目标是让数据中心架构进入下一个更高效节能的新阶段。Rambus高管表示,未来,CXL会推出池化的概念,也将帮助下一代的数据中心变得更加高效化、节能化,以一种新的架构来迎合数据中心的未来需求,可以很好地满足“东数西算”的部分需求。因此,Rambus也正在和数据中心领域的一些合作伙伴紧密联系,看如何用以Rambus的产品赋能其数据中心建设。

紧跟PCIe技术迭代,不断强化数据中心业务

PCIe从PCIe 5.0到6.0的迭代,以及从NRZ到PAM4的变化,是PCIe规范在物理实现方面的一个重大变化。Rambus高管认为,从NRZ到PAM4的巨大变化一定程度上为PCIe技术未来的发展留下了足够的空间和期待。比如说下一代PCIe标准,暂时称呼为PCIe 7.0,基于历史期望,数据速率还需要继续翻倍,因此PCIe 6.0的PAM4可能会升级为“PAM6/PAM8”,以在未来获得更高的数据传输速率。

当然,毕竟现在PCIe 6.0还刚刚发布,处于正在走向成熟的阶段,对PCIe 7.0还没有完整的定义和规划。等到PCIe7.0真的到来,相信我们会对它的数据传输速率等都会有更加全面的了解。

着眼于现在,PCIe 6.0控制器将成为ASIC供应商的重要基石,帮助他们为AI/ML加速器建立起一个更加完善的PCI生态系统,并支持不断发展的数据中心中PCIe 6.0级数据传输的基础设施。

-

IP

+关注

关注

5文章

1701浏览量

149497 -

Rambus

+关注

关注

0文章

60浏览量

18803

发布评论请先 登录

相关推荐

华为与中国能建打造“东数西算”标杆数据中心

IaaS+on+DPU(IoD)+下一代高性能算力底座技术白皮书

华为云华东(芜湖)数据中心正式开服

东盟能源和华为主编的《东盟下一代数据中心建设白皮书》正式发布

港灯打造了面向未来的下一代电力数据中心网络

莫仕QSFP-DD BiPass 冷却配置提供下一代数据中心解决方案-赫联电子

芯原推出面向下一代数据中心的全新VC9800系列IP

AI加持下的数据中心,需要怎样的高速接口技术?

助力“东数西算”,Rambus PCIe 6.0控制器IP,抢先布局下一代数据中心

助力“东数西算”,Rambus PCIe 6.0控制器IP,抢先布局下一代数据中心

评论