在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义IP,然后在之后的设计中继续使用此IP。因此本次详细介绍使用VIvado来封装自己的IP,并使用IP创建工程。

一、IP的创建

首先新建工程。

如前面部分介绍的工程创建,完成代码的设计、输入,并在功能仿真或时序仿真完全正确的情况下。

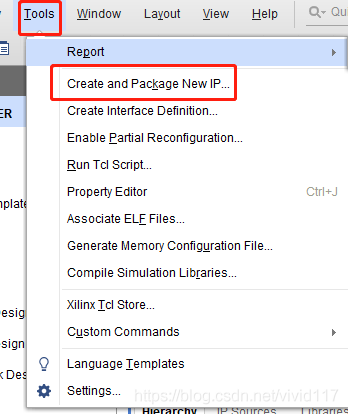

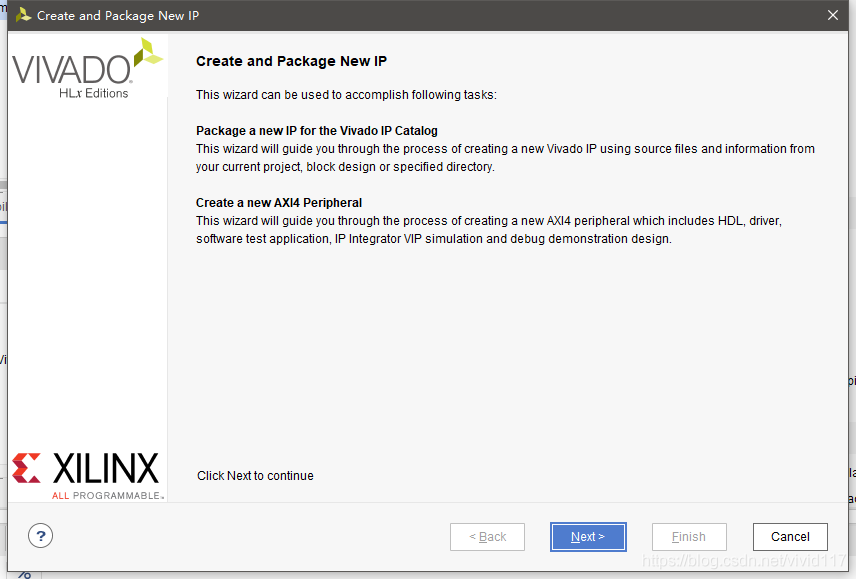

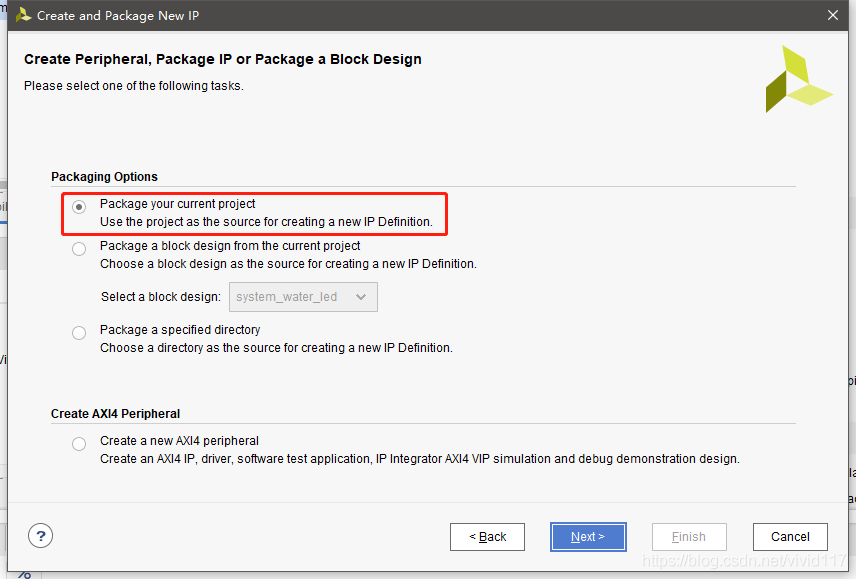

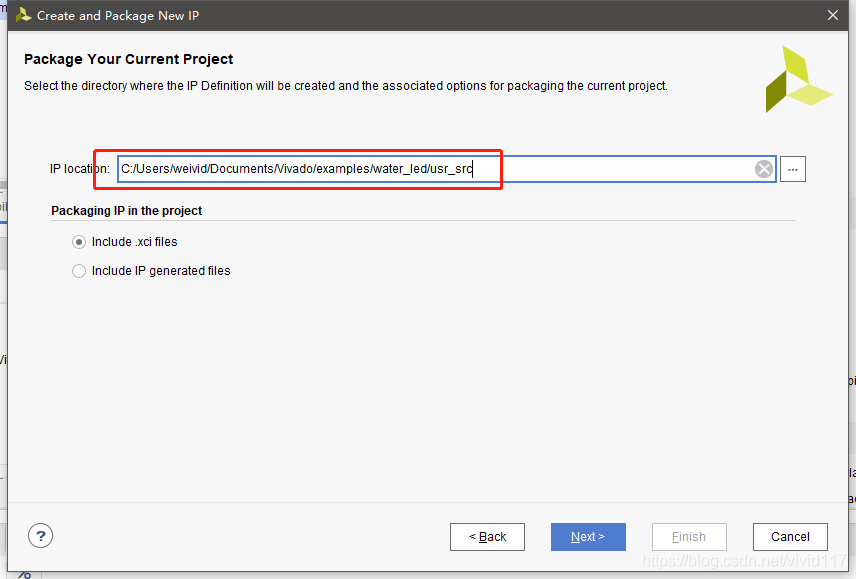

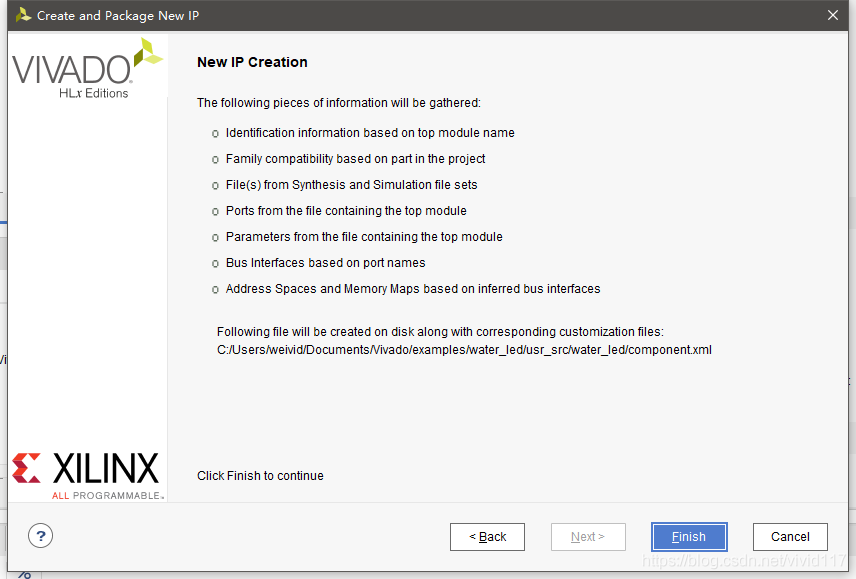

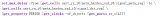

按如下步骤执行:

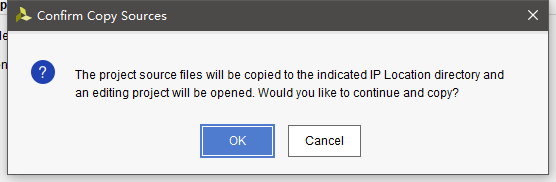

选择要存放的位置,这一步很重要,可以存放在以后专门自定义的IP文件夹内,方便以后添加和管理查看。

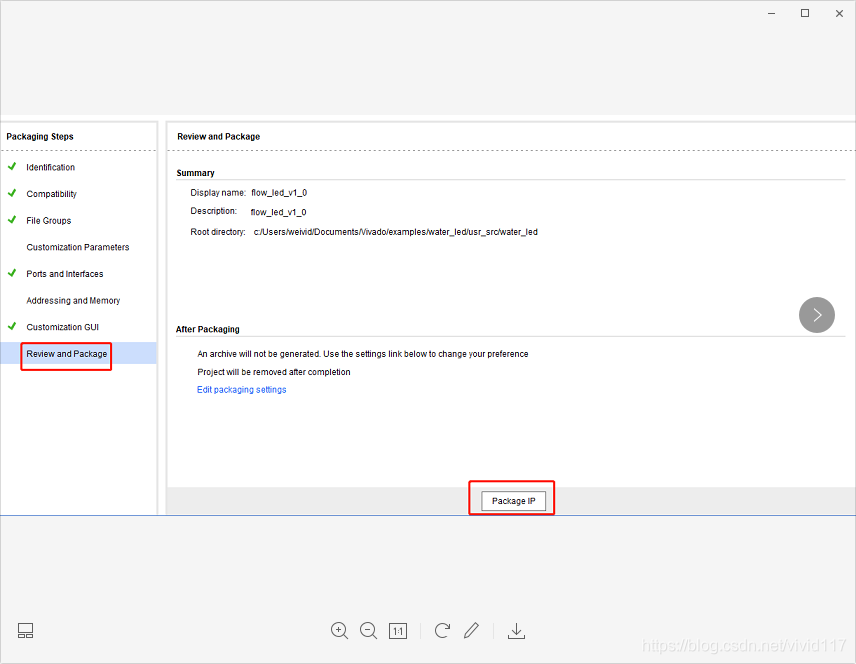

然后会弹出如下封装IP的界面,按如下执行Package IP

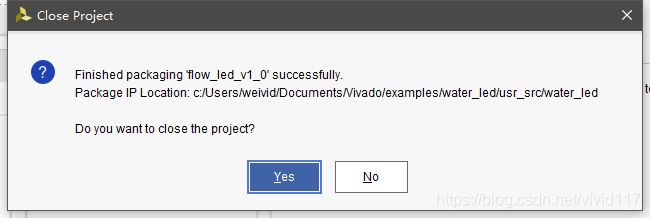

至此,我们IP就封装好了。可以打开我们IP的文件夹,包括三个文件,src是源代码文件。

二、IP的使用

本次设计采用block design来使用自定义的IP。

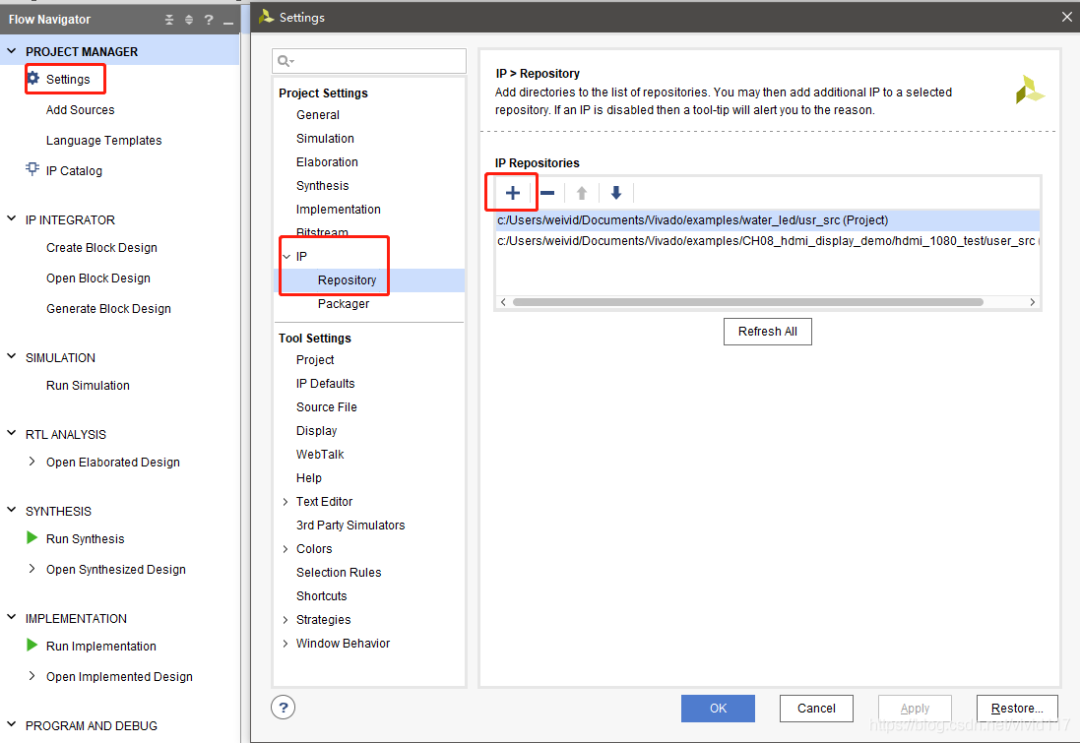

IP的添加。

1.新建一个vivado工程。

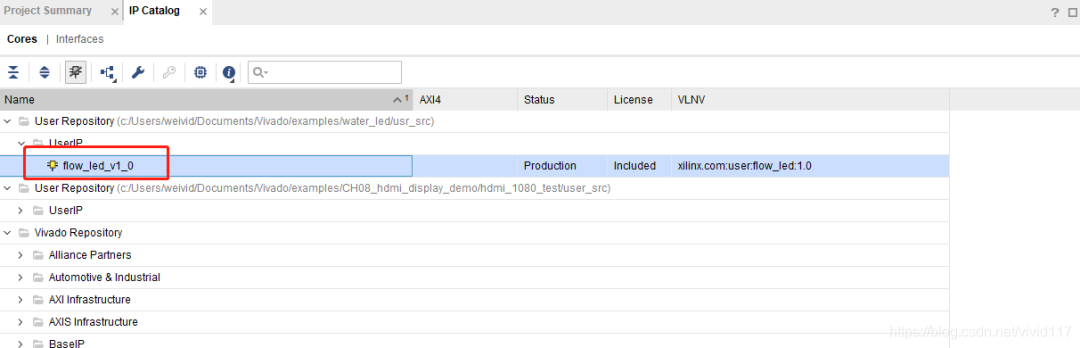

按照上面的步骤添加自定义的IP。

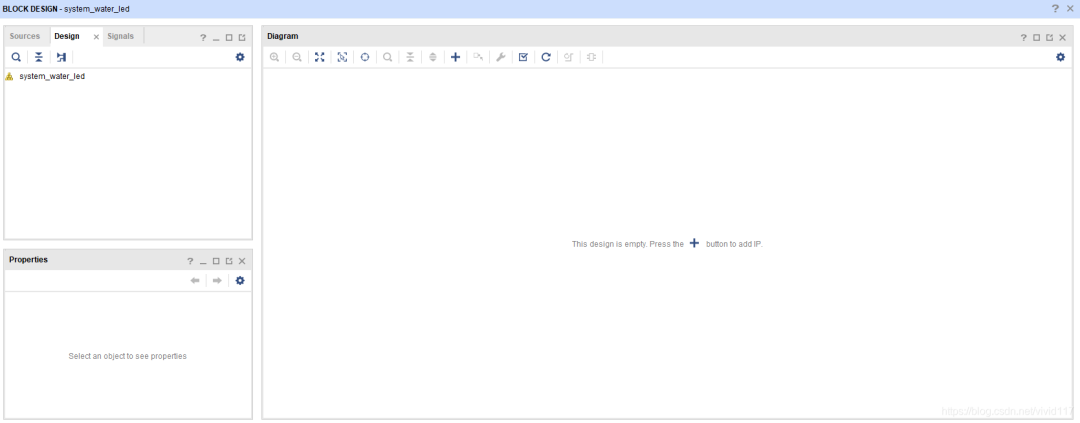

创建一个BD文件

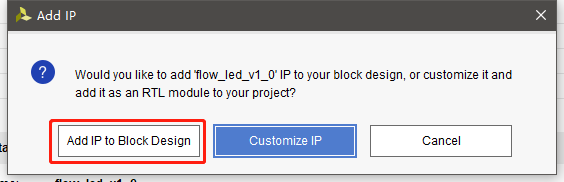

使用自定义的IP

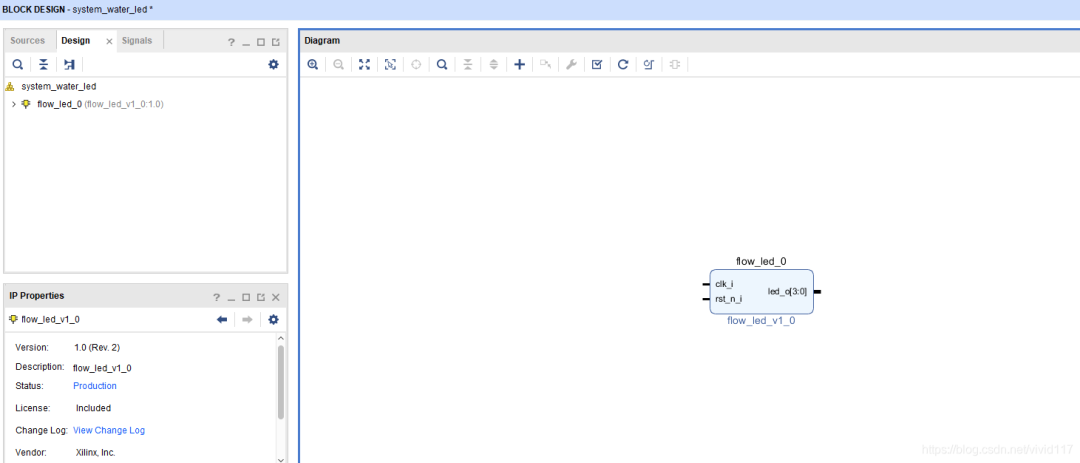

添加完之后如下:

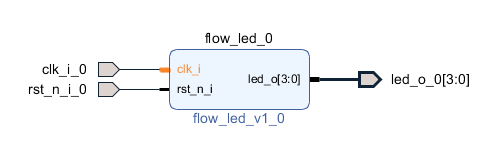

将引脚引出并重新命名,具体操作选中相应的管脚,右键选择make external

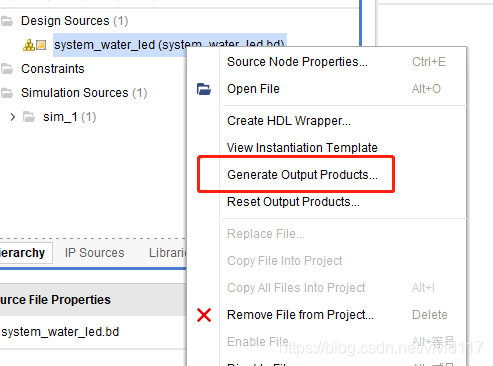

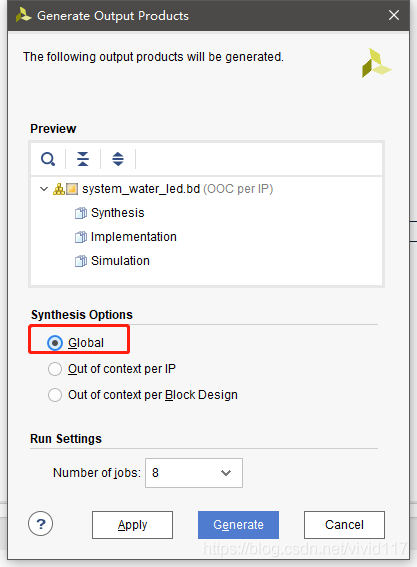

然后右键选择general output product

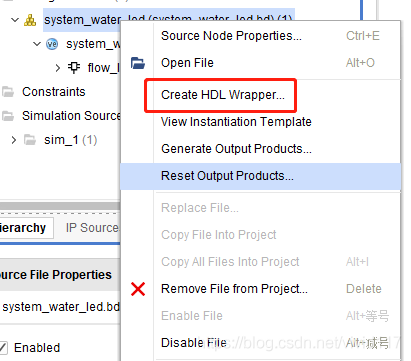

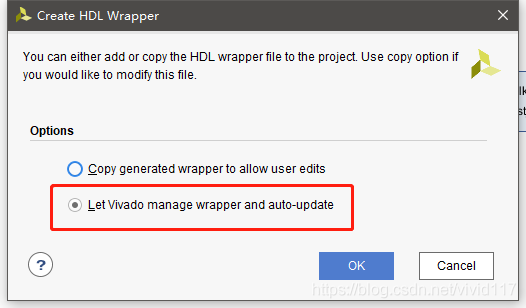

然后右键选择 create HDL wrapper。

最后添加约束文件并进行综合编译产生bit流,然后上班调试。

原文标题:FPGA学习-Vivado封装自定义IP及调用

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

FPGA

+关注

关注

1628文章

21728浏览量

602949 -

封装

+关注

关注

126文章

7872浏览量

142888 -

Vivado

+关注

关注

19文章

812浏览量

66470

原文标题:FPGA学习-Vivado封装自定义IP及调用

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PYNQ设计案例:基于HDL语言+Vivado的自定义IP核创建

vivado带ip核的工程封装

基于 FPGA vivado 2017.2 的74系列IP封装

xilinx vivado 怎么封装包含一个ip核的自定义ip?

怎么在vivado HLS中创建一个IP

Xilinx Vivado的使用详细介绍(3):使用IP核

Vivado Design Suite用户指南:创建和打包自定义IP

使用VIvado封装自定IP并使用IP创建工程

使用VIvado封装自定IP并使用IP创建工程

评论