DDS原理及FPGA实现

一个按一定速度沿x轴行进,同时半径按一定频率在圆周上滑动的圆,最后留下的痕迹就是一个正余弦波。

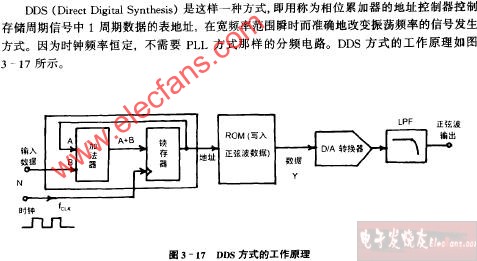

DDS全称直接数字频率合成(Direct Digital Synthesis),简单来讲,分以下几步:

1.抽样

但一般来讲,为了波形的完整,我们一个周期中最少保留的点还会多一些。如果假设一个周期最小4个点,采样频率为为100MSPS,那我们可以还原的源信号的频率最大为25M

我们通常对一个周期采样的点数为2^N个,在这里,我采样为2的8次方,即256个。

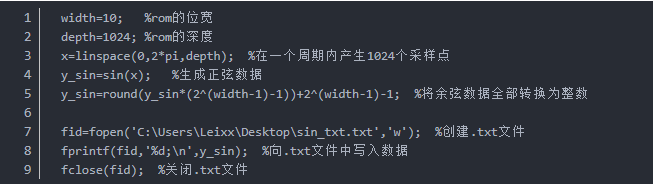

采样的过程可以通过matlab进行模拟,设置好采样的位宽和深度便可以生成采样数据。

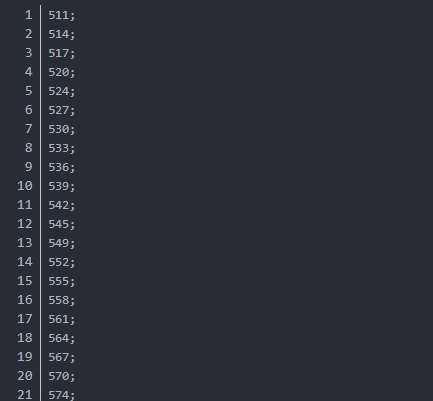

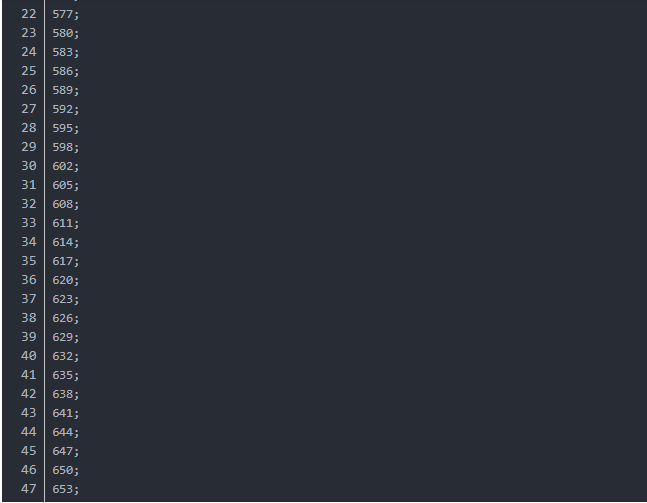

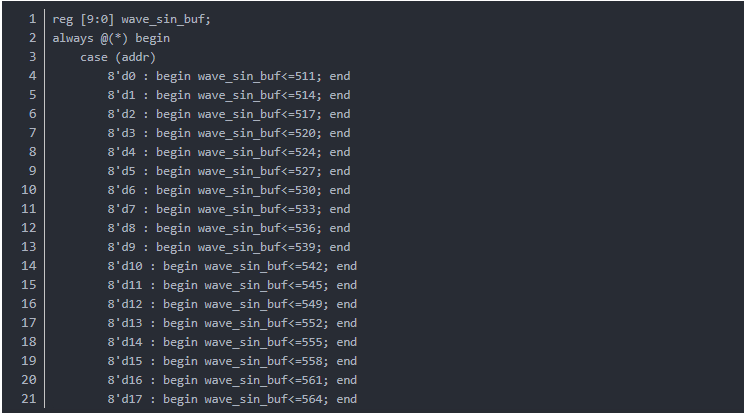

得到的部分采样数据如下

2.合成

DDS技术的核心,简单来说就是将我们的抽样数据还原成模拟信号。还原的方式和文章讲到的一样:以一定的频率将抽样数据依次输出,就可以还原波形。

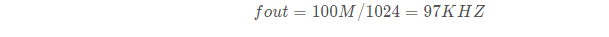

假设,以100M的频率输出我们的1024个抽样数据,则将会得到一个频率为

的正弦波。这就达到了最初的信号输出。

那如何调频呢?

调频的方案有两种:一种是改变我们的时钟频率,将我们读取抽样数据的速度变快或者变慢,这样就可以改变频率。这种方法对于当下很多开发板固定的晶振频率来说比较难以实现。

另一种方案就是减少我们输出的抽样数据,输出的抽样数据越少,按照上面的公式,频率便会越高。

比如说,我们最开始查数据是按照依次加一的方式,那我们改成依次加二,显然,这样做之后,输出频率便会提高。但也会带来一个问题,我们输出的点数少了,那么点与点之间不再平滑,输出的波形会变得阶梯化。

显然加一会得到一个频率,加二会得到另一个频率,但这两个频率都不是我想要的怎么办?

如何精准调频?

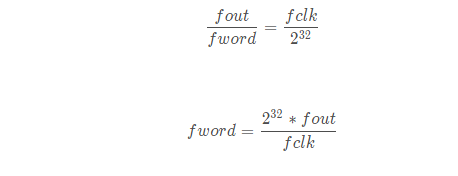

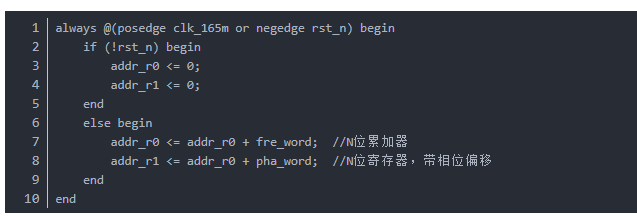

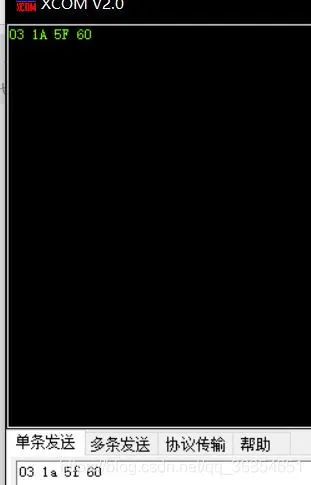

假设我们需要得到一个频率很低的信号,1KHZ,而我们的时钟频率为100M,我们在一个周期内输出1024个点也达不到这样的频率。因此我们就需要在输出的每个数据之间进行等待,可以通过设置计数器来解决这个问题。为了使输出的信号尽可能的低,我们设置一个32位的累加器。将高10位作为查表的地址。对于1KHZ,有

所以,累加值f w o r d fwordfword为4295。

其余频率对应的累加值均可以按此公式计算。

如何解决阶梯化?

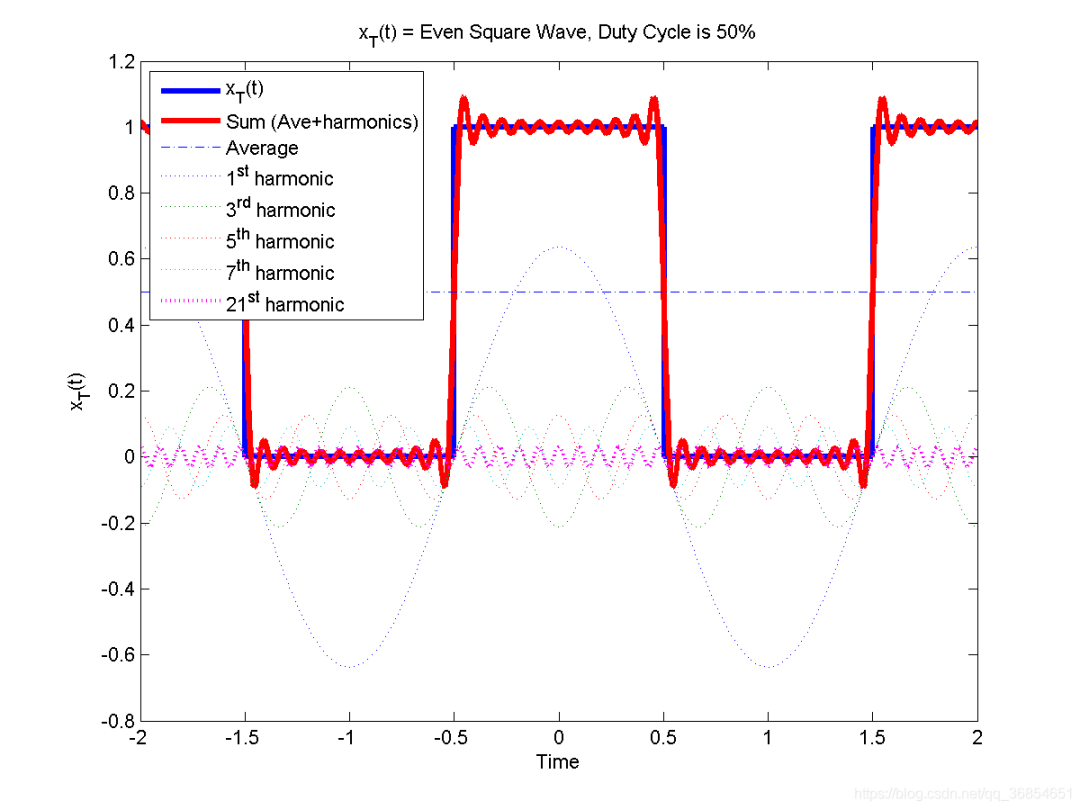

从数字上来看,波形变得阶梯化是因为我们输出的抽样数据减少,点与点之间不再平滑。但是从另一个角度理解,波形变得阶梯化的原因是因为叠加了其他杂波

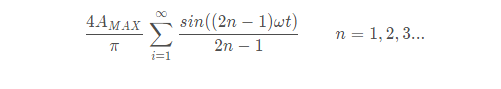

我们简单地波形变得阶梯化理解为趋近于方波。下图是方波的合成。

由方波的傅里叶级展开式

可以得出,方波是由无数个奇次谐波叠加起来的,频率为2n-1倍,幅度为

因此,若我们的波形也是叠加了高频的谐波导致波形阶梯化,那么就通过低通滤波器来滤除高频谐波,得到平滑的波形。

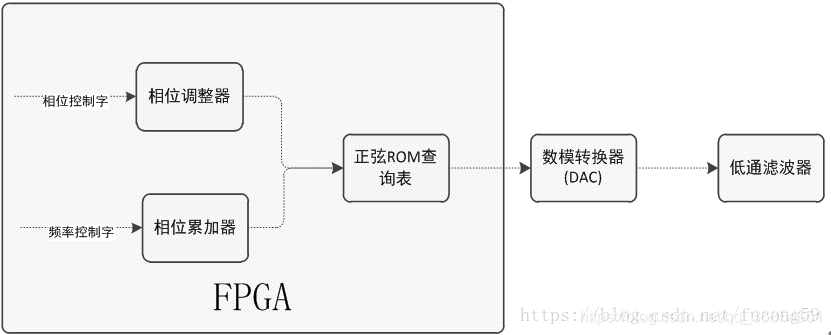

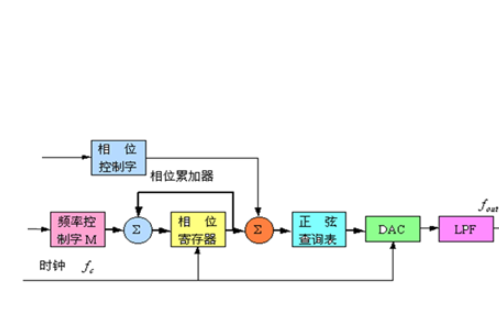

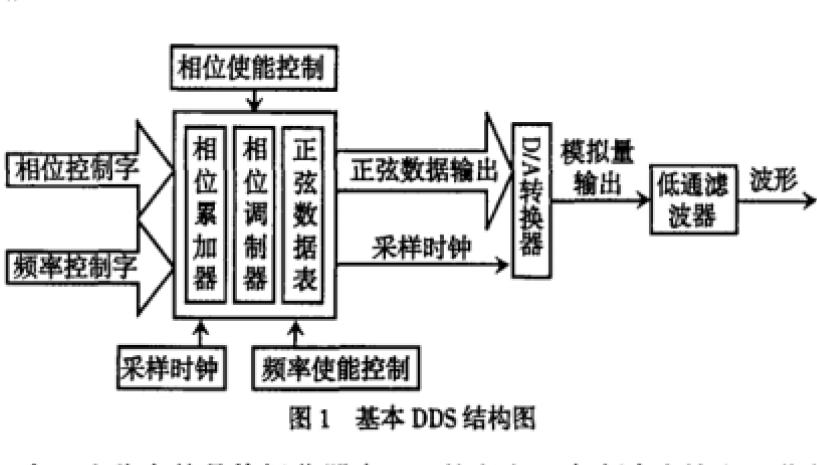

DDS的原理图如下:

3.实现

基于FPGA的DDS,就是按照上面的原理来实现的。

我这里只储存了256个数据,至于原因,后面会讲到。

(2)累加

设置一个32位相位控制字和频率控制字,进行累加。

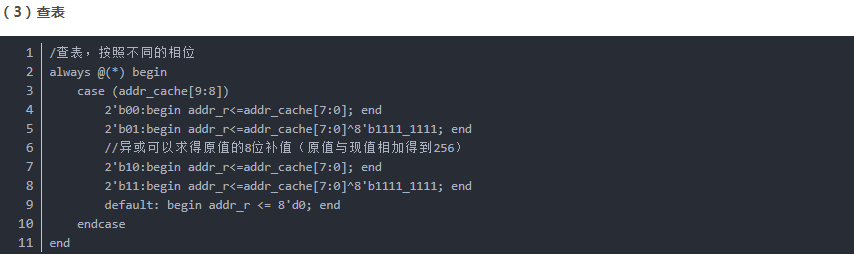

这里我只储存了2^8个波形数据,是为了节省寄存器资源。因为一个周期的正弦波的四个相位实际上数据是有关联的,知道第一相位的数据,便可推导出另外三个相位的数据。

代码中,00表示第一相位,此时按照正常的查表顺序即可。

01表示第二相位,此时,查表的顺序应当是2^8-地址值。但实际上这个减法的操作就是异或的操作。

相减后,地址值8位中原本的“1”变为0,原本的“0”变为1,正好和异或的原理相同。这里为了方便,就直接写了异或。实际上写256-addr_cache[7:0]也是一个效果。

其余两个相位,查表的方式类似。

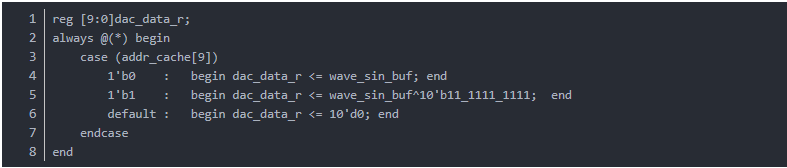

(4)转换

因为我这里的256个数据是第一相位的,而第三第四相位的数据是等于2^10减去第一相位的值,因此这里需要将输出的数据转换一下。

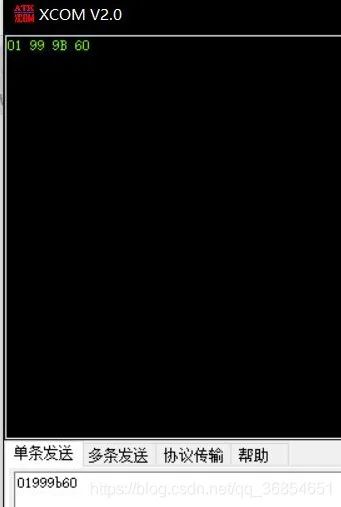

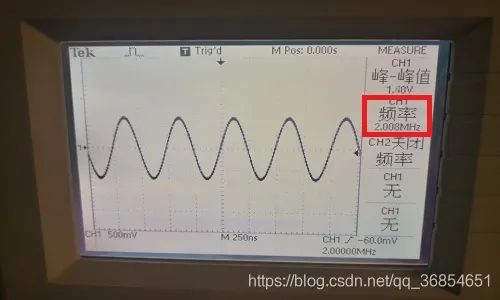

(5)测试

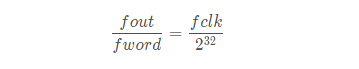

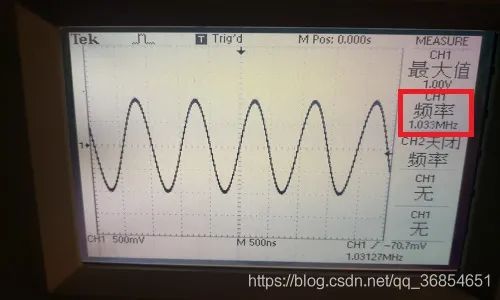

通过串口分别发送01999b60和031a5f60,由上面公式

可以算出分别是1M和2M的频率控制字

以上便是DDS的FPGA实现。

原文标题:FPGA学习-DDS原理及FPGA实现

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

DDS

+关注

关注

21文章

633浏览量

152630

原文标题:FPGA学习-DDS原理及FPGA实现

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化...

如何利用现场可编程逻辑门阵列FPGA实现实现DDS技术?

基于FPGA的DDS调频信号的研究与实现

基于FPGA的DDS杂散分析及抑制方法

基于FPGA的DDS设计

DDS的基本结构和工作原理及Matlab在DDS系统仿真中的应用说明

如何使用FPGA实现DDS数字移相信号发生器的原理

DDS的工作原理及基于FPGA的实现方法

DDS的工作原理及基于FPGA的实现方法

评论