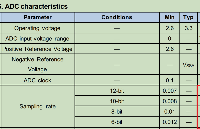

在我们之前关于模数转换器 (ADC) 重要性的文章中,我们重点介绍了工业物联网常用的各种架构。特别是,我们研究了哪种架构最适合低延迟、低功耗和高精度应用,每种选择都有各种优点和缺点。当我们查看需要低延迟和低功耗的应用时,与闪存、delta-sigma 和流水线等其他架构相比,逐次逼近寄存器 (SAR) ADC 提供了最佳的整体解决方案。

对于越来越多需要更快采样率以满足机器对机器 (M2M) 连接不断增长的需求的应用,ADC 的选择略有不同。在最近的一篇文章中,我们讨论了这些连接如何随着物联网的发展而急剧增加,而位于vwin 前端 (AFE) 中的 ADC 是这些连接的核心。那么,对于需要快速采样率的应用,需要考虑哪些权衡以及哪种架构优于其他架构?

再次考虑 SAR ADC。在这种架构中,模拟输入信号被采样,然后通过一个工作在高于采样率的频率的比较器与连续的参考电压进行比较。

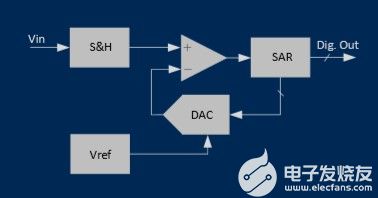

图 1:SAR ADC 框图

在一个采样周期内,比较器至少需要做出与转换器分辨率一样多的决定。更高的分辨率会降低最大采样率,这取决于比较器做出决定的速度以及 SAR 逻辑的运行速度。在开关电容实现中,ADC 输入网络等效电路,如图 2 所示,基本上包括一个采样电容和一个采样开关。

图 2:SAR ADC 输入网络

采样和保持 (S&H) 操作嵌入在 DAC 电路中,采样电容器的大小可满足噪声要求。通过这种配置和正确的采样电容大小,SAR ADC 可以转换非常高频的信号(数十 MHz),而不会导致高功耗。

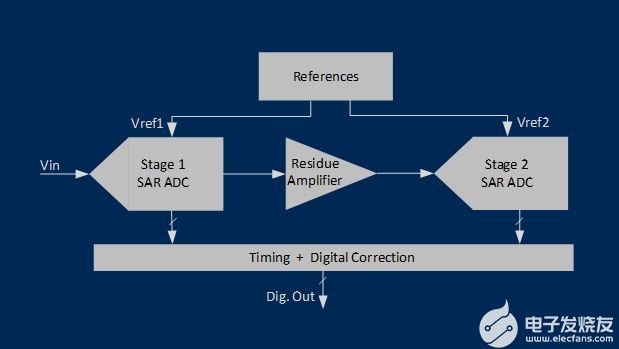

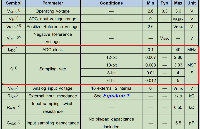

第二种需要考虑的架构是 SAR 辅助流水线 ADC,如图 3 所示。该 ADC IP 可以通过两个较低分辨率的 SAR ADC 级和一个剩余放大器来实现。第一阶段解析数字输出字的最高有效位。残留物被第二阶段放大和取样。由于每个阶段都使用较低的分辨率,因此可以实现每个阶段的快速转换时间。两个阶段同时工作;在第二阶段转换残留放大信号时,第一阶段已经在采样并转换下一个样本。与单个 SAR 架构相比,这种流水线可以显着提高最大采样率。

图 3:SAR 辅助流水线 ADC 框图

Adesto 的所有 ADC IP 内核都提供的另一个考虑因素是参考电压生成。在 ADC 内核附近生成参考电压很重要,因为它可以防止性能下降。优化和高效的参考电压生成和缓冲对于稳健、节能和高精度的转换器至关重要。

Adesto拥有经过硅验证的大型 SAR 和流水线辅助 SAR ADC IP 块产品组合,可用于许可,包含满足应用程序的采样率、功率和延迟要求所需的所有元素。

审核编辑:郭婷

-

转换器

+关注

关注

27文章

8694浏览量

147085 -

SAR

+关注

关注

3文章

416浏览量

45949 -

adc

+关注

关注

98文章

6495浏览量

544461

发布评论请先 登录

相关推荐

用于高采样率应用的SAR ADC

用于高采样率应用的SAR ADC

评论