UltraScale和UltraScale+进一步增强了Clock root的概念,从芯片架构和Vivado支持方面都体现了这一点。为了理解这一概念,我们先看看UltraScale/UltraScale+的时钟资源。

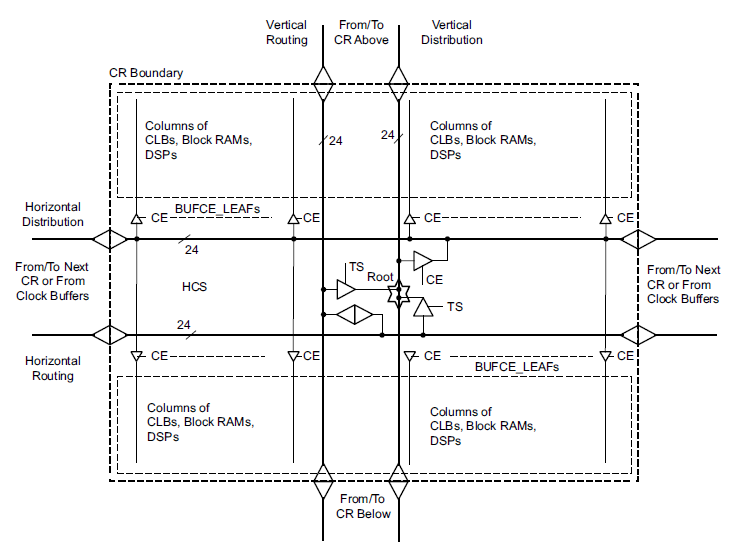

每个时钟区域有24个水平分发轨道(HorizontalDistribution)和水平布线轨道(HorizontalRouting),同时,垂直方向也有24个分发轨道(VerticalDistribution)和24个布线轨道(Vertical Routing),如下图所示。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时钟

+关注

关注

10文章

1733浏览量

131445 -

UltraScale

+关注

关注

0文章

117浏览量

31461

原文标题:设计中的Clock root可以修改吗?

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

时序约束一主时钟与生成时钟

的输出,对于Ultrascale和Ultrascale+系列的器件,定时器会自动地接入到GT的输出。 1.2 约束设置格式 主时钟约束使用命令create_clock进行创建,进入Timing

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件可快速启动汽车、工业、视频和通信应用设计。AMD/Xilinx MPSoC ZCU102 评估套件采用

为Xilinx® Zynq®UltraScale™系列多处理器中的VCCINT_VCU轨供电

德赢Vwin官网

网站提供《为Xilinx® Zynq®UltraScale™系列多处理器中的VCCINT_VCU轨供电.pdf》资料免费下载

发表于 09-25 10:54

•0次下载

使用TPS65086x PMIC为Xilinx Zynq UltraScale MPSoC供电

德赢Vwin官网

网站提供《使用TPS65086x PMIC为Xilinx Zynq UltraScale MPSoC供电.pdf》资料免费下载

发表于 09-21 11:11

•0次下载

一个更适合工程师和研究僧的FPGA提升课程

设计;

● UltraFast 设计方法;

● 使用UltraScale和UltraScale+架构进行设计;

● FPGA 功耗最优化;

● 使用 Vivado Design Suite 4

发表于 06-05 10:09

基于FPGA设计的BRAM内部结构

再看末级触发器对BRAM时序性能的影响,下图依次展示了7系列FPGA、UltraScale+和Versal芯片在未使用和使用末级触发器两种情形下时钟到输出的延迟。

发表于 04-25 10:42

•414次阅读

中高端FPGA如何选择

为了使数据传输更加高效,Achronix FPGA上的Memory资源也是非常给力,不管是片上Ram还是DDR接口,都比Virtex Ultrascale+有很大优势。

在Speedster7t

发表于 04-24 15:09

AMD推出全新Spartan UltraScale+ FPGA系列

AMD 已经拥有 Zynq UltraScale+ 和 Artix UltraScale+ 系列,而 Spartan UltraScale+ FPGA 系列的推出使其不断现代化。

发表于 03-18 10:40

•376次阅读

AMD 扩展市场领先的 FPGA 产品组合,推出专为成本敏感型边缘应用打造的AMD Spartan UltraScale+ 系列

股票代码:AMD)今日宣布推出 AMD Spartan™ UltraScale+™ FPGA 系列,这是广泛的 AMD 成本优化型 FPGA 和自适应 SoC 产品组合的最新成员。Spartan

发表于 03-07 15:17

•498次阅读

AMD推出Spartan UltraScale+ FPGA系列产品

AMD公司,全球知名的芯片巨头,近日宣布推出全新的AMD Spartan UltraScale+ FPGA系列产品组合。这一新系列作为AMD成本优化型FPGA、自适应SoC产品家族的最新成员,特别针对成本敏感型边缘应用进行了优化,旨在提供更高的成本效益和能效性能。

为嵌入式应用选择AMD Spartan UltraScale+FPGA

全新 AMD Spartan UltraScale+ FPGA 系列在价格、功耗、功能和尺寸之间取得了良好的平衡。了解该系列器件如何帮助设计人员以低成本推动 I/O 密集型应用产品快速上市。

AMD 扩展市场领先的 FPGA 产品组合,推出专为成本敏感型边缘应用打造的AMD Spartan UltraScale+ 系列

股票代码:AMD)今日宣布推出 AMD Spartan™ UltraScale+™ FPGA 系列,这是广泛的 AMD 成本优化型 FPGA 和自适应 SoC 产品组合的最新成员。Spartan

发表于 03-06 11:17

•369次阅读

AMD推出全新Spartan UltraScale+ FPGA系列

AMD日前正式推出了全新的Spartan UltraScale+ FPGA系列,该系列作为AMD广泛的成本优化型FPGA和自适应SoC产品组合的最新成员,专为边缘端各种I/O密集型应用设计。

1.25G突发时钟数据恢复/ UltraScale中的2.5G PON应用设备总结

德赢Vwin官网

网站提供《1.25G突发时钟数据恢复/ UltraScale中的2.5G PON应用设备总结.pdf》资料免费下载

发表于 01-14 09:56

•0次下载

UltraScale/UltraScale+的时钟资源

UltraScale/UltraScale+的时钟资源

评论