本文讲述了我们华林科纳研究了M111N蚀刻速率最小值的高度,以及决定它的蚀刻机制,在涉及掩模的情况下,M111N最小值的高度可以受到硅/掩模结处的成核的影响,以这种方式影响蚀刻或生长速率的结可以被认为是一个速度源,这是我们提出的一个数学概念,也适用于位错和晶界,速度源的活动取决于相关的M111N平面与掩模之间的夹角,因此在微观机械结构中蚀刻的薄壁相对的M111N侧可以有不同的值。

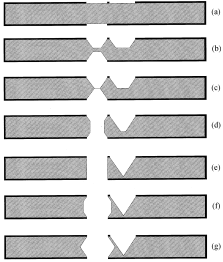

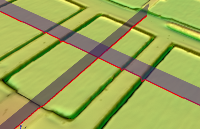

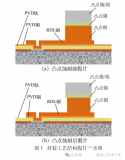

在图1a中,示出了S 100T单晶硅炉和部分覆盖它的惰性掩模的横截面,将这种图案化的晶片暴露于各向异性蚀刻剂将导致衬底蚀刻,如随后的截面图所示(图1 b-g),结果是在晶片的开口(左侧)和V形槽(右侧)之间有一个非常薄的板,这种薄板可用作微流体处理中的被动阀。使用与以前相同的技术,在双面抛光的S100单晶硅片上蚀刻M 111N板,衬底背面的掩模开口向右变宽(图1),测量了作为时间函数的板两侧的欠蚀刻,使用光学显微镜确定欠蚀刻。

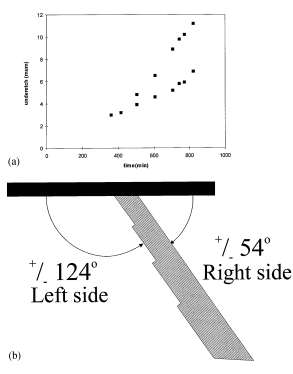

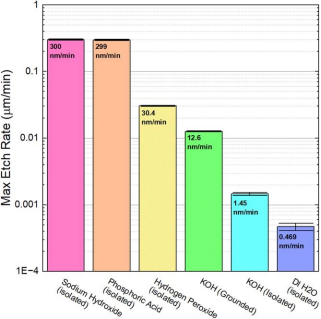

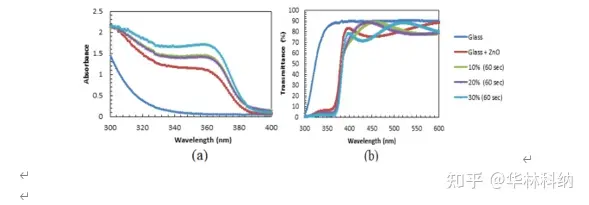

在上图a中,这种测量的结果显示在图表中,蚀刻阶段c(图1)在大约360分钟时达到,从那时起,观察到板左侧的RUE显著增加(图b),根据该图中的斜率,我们确定上部线的RUE为24nm/min,下部线的RUE为7.5 nm/min,这导致RUE的两个值相差约3倍。

对RUE出现两个不同值这一事实的解释,可以在111N面的腐蚀机理中找到,用光学显微镜和微分干涉对比技术(DICM)检查了板的两面,发现两侧的表面结构明显不同,在右侧,发现在整个表面上出现轻微的六边形偏心蚀坑,在左侧,发现圆形的、成束的、阶梯状的结构起源于上边缘,即掩模与板连接的同一边缘。

从这些观察中,得出结论:欠蚀刻速率的差异是由掩模和M 111N硅表面之间的角度差异引起的,并且与该角度差异相关,不可能用一个简单的几何因子把它们中的一个与RM 111 N联系起来,因此,我们倾向于将各向异性系数定义为RM 100 N /RUE。在现今存在的运动波理论中,这种不同RUE的影响无法解释,因为严格地说,运动波理论只能应用于自由浮动的完美单晶,对于三个或三个以上交界面相交成一条线或交界面与位错之间的情况,必须在边界位置考虑某些边界条件,这在Shaw基于运动波理论的众所周知的几何构造中是没有认识到的,这些边界条件在微观或宏观上影响界面的形状,在这种情况下,它们的影响是宏观的:真实的差异。

第一个条件是遮罩定义了表面的末端——这是微不足道的,但它不会影响移动表面的方向;第二个边界条件确定了方位;第二个边界条件由机械平衡条件或成核统计给出(特别是对于刻面表面,蚀刻速率取决于梯级的成核速率)。忽略第二个边界条件意味着RUE值不变,RUE的常数值在几何上与RM 111 N相关,这是从凹面球体蚀刻实验中发现的,其中没有增加成核速率的结论,在我们的情况下,相关的第二个边界条件是提到的“成核边界条件”,它指出,一定的刻蚀速率是由结附近的台阶形核所决定的,这是因为结上的原子比平面上的原子更容易被蚀刻去除,因为总键能较低,因为差值取决于m111平面和掩模之间的角度,所以测得的RUE也将取决于这个角度,当然,由于成核的梯级链,方向也会与S 111T略有不同。

可以注意到,速度源行为同样可以由更微小的效应引起,例如不规则前进的微裂纹或硅和掩模之间的晶界,甚至掩模下面的脏表面,速度源概念适用于所有情况,只有机制的性质和规模不同,速度源的概念可能会影响对m111最小值的解释。

在我们的例子中,硅/掩模结的影响可能取决于边缘角度、掩模材料和温度,验证这种行为的实验目前正在进行中。已经用DICM光学显微镜证明,硅中M 111N平面的腐蚀机理不仅取决于引言中提到的参数,而且还取决于它们相对于掩模的取向,这会影响RUE,因为RUE是由硅/掩模结引起的台阶形核过程决定的,所以RUE现在不能通过几何因子与RM 111 N相关,我们把这种效应称为速度源,因此倾向于使用RM 100n/rue作为各向异性系数。

审核编辑:符乾江

-

蚀刻

+关注

关注

9文章

413浏览量

15368 -

有机物

+关注

关注

0文章

14浏览量

1671

发布评论请先 登录

相关推荐

湿法蚀刻的发展

VCSEL激光在蚀刻和光刻中的应用与前景

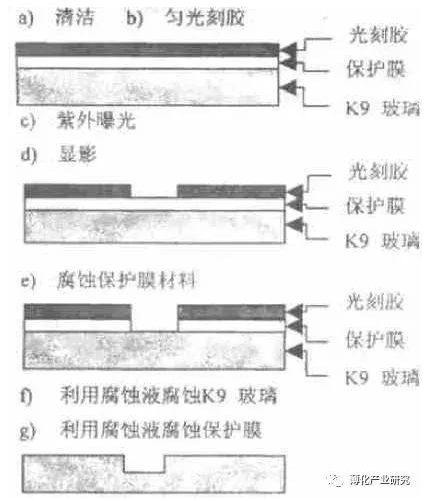

玻璃基电路板的蚀刻和侧蚀技术

玻璃电路板表面微蚀刻工艺

基于光谱共焦技术的PCB蚀刻检测

SK海力士寻求东电低温蚀刻设备,或降低NAND闪存堆栈层数

通信——通过表面电荷操纵控制锗的蚀刻

蚀刻机远程监控与智能运维物联网解决方案

电偶腐蚀对先进封装铜蚀刻工艺的影响

东京电子新型蚀刻机研发挑战泛林集团市场领导地位

半导体资料丨氧化锌、晶体硅/钙钛矿、表面化学蚀刻的 MOCVD GaN

M111N蚀刻速率,在碱性溶液中蚀刻硅

M111N蚀刻速率,在碱性溶液中蚀刻硅

评论