前言

硅通孔(Through Silicon Via,TSV)技术是一项高密度封装技术,它正在逐渐取代目前工艺比较成熟的引线键合技术,被认为是第四代封装技术。在2.5D/3D IC中TSV被大规模应用于芯片和封装基板的互连,以及芯片和芯片的互连。TSV技术通过铜、钨、多晶硅等填充,实现垂直电气互连。硅通孔技术可以通过垂直互连减小互联长度,降低信号延迟,降低寄生电容/电感,实现芯片间的低功耗、高速、宽带通信和实现器件集成的小型化。

在结构上,TSV的仿真模型一般可以简化为导电柱、种子层和隔离氧化层。TSV互连填充主要依靠电镀铜的方式进行。一般来说,在电镀前,孔内和表面需要导电的种子层覆盖,一般会以钛和铜为种子层,超高深径比或特殊结构可能需要采用金种子层。种子层是电镀的基本保障,在确保电镀顺利的同时提供导电特性。

本文介绍了采用芯和半导体ViaExpert软件进行TSV阵列的建模和仿真分析流程。TSV结构复杂,存在建模繁琐、分析不便等问题。对经常从事TSV仿真的工程师来说,如何利用工具模板快速对TSV阵列进行建模并仿真显得特别重要。

TSV阵列建模流程

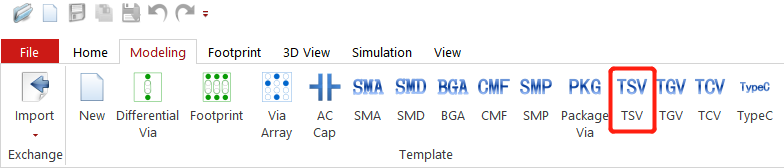

1. 调用TSV模板

首先我们打开ViaExpert工具,选择菜单栏ModelingTemplateTSV图标;

图1:TSV模板选择

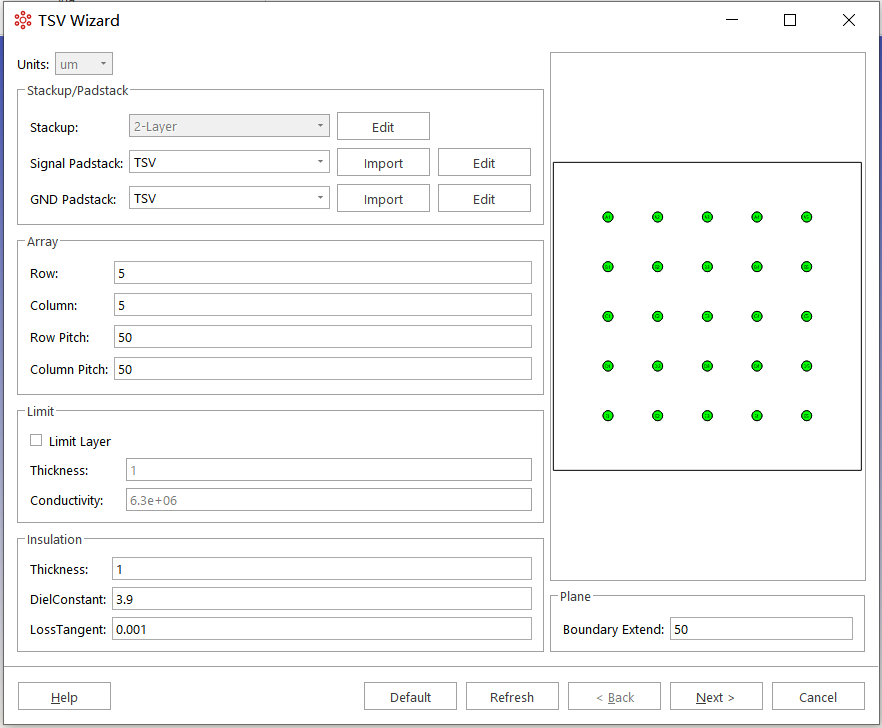

点击TSV图标后,可进入TSV建模向导界面;

图2:TSV向导窗口

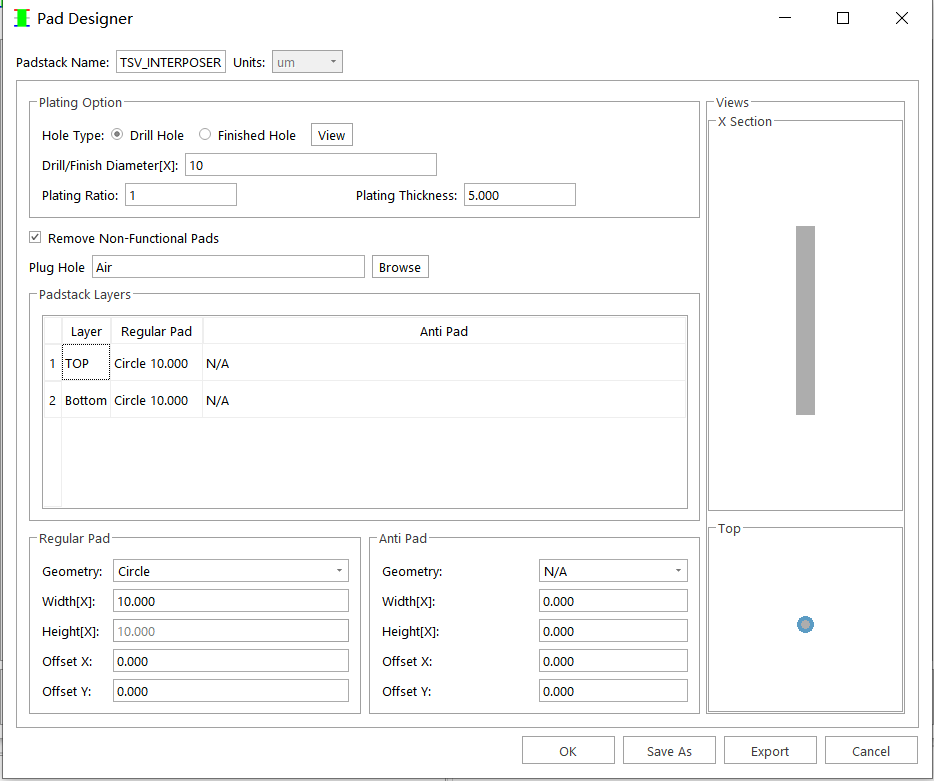

接下来点击TSV Wizard中的Padstack/ Edit或者在Home 菜单下进入“Padstack”,根据TSV的信息设置Padstack的尺寸;

图3:Home菜单

在Pad Designer中Regular Pad为TSV的直径,Hole的尺寸可以根据TSV的结构进行设置,如果是100%的导电柱结构,则设置为和Regular Pad一样的Drill 尺寸。详细的俯视图和侧视图可以在窗口的右边进行Preview。

图4:Pad Designer

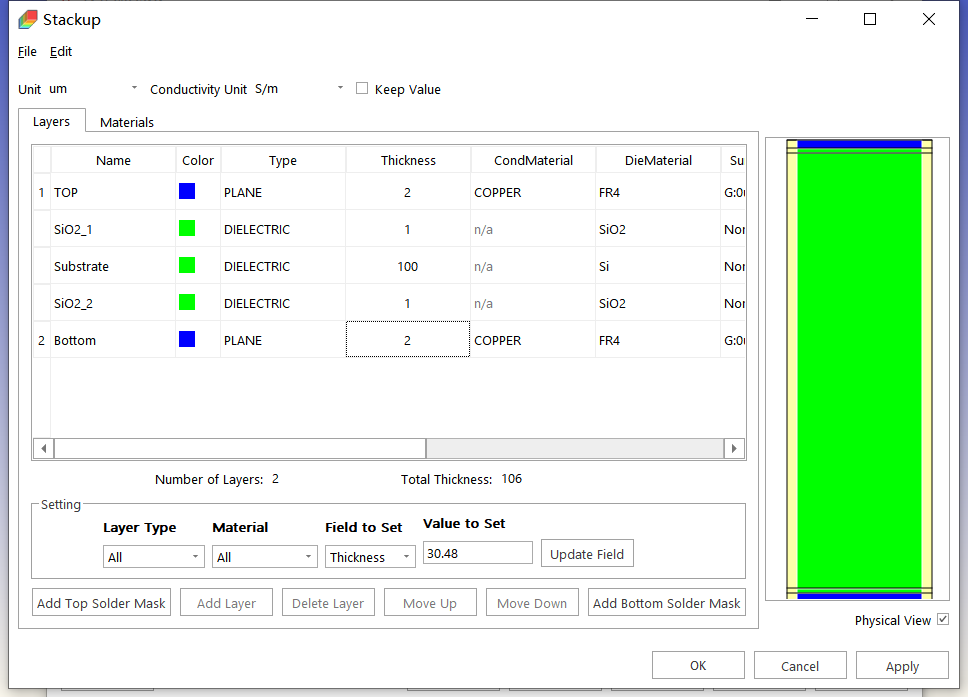

3. Stackup和Materials 设置

点击TSV Wizard中的Stackup/ Edit进入Stackup编辑界面,在该界面下用户可以根据硅材料的厚度来进行TSV高度的设置,通常在Si interposer中TSV厚度为50至100um不等。需要注意的是,在Materials编辑窗口中用户必须指定Si和SiO2的材料属性,尤其是Si作为半导体既需要定义Conductivity也需要定义Dk和Df值,这样确保仿真结果能够vwin 真实材料特性对TSV所造成的影响。

图5:Stackup编辑窗口

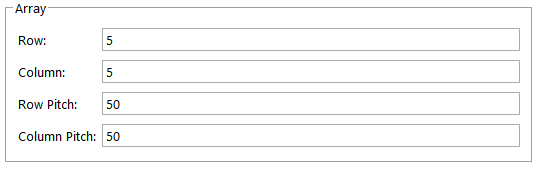

4. TSV Array 设置

在TSV Wizard中的Array编辑区域,用户可以指定TSV阵列的数量和间距,在此案例中我们按照下列参数进行设置:

图6:TSV Array编辑

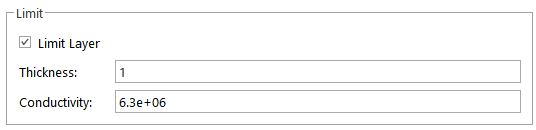

5. Limit Layer 设置

在TSV Wizard中的Limit Layer编辑区域;用户可以指定TSV种子层的金属厚度和电导率参数,因为其对结果影响微乎其微,一般在简化模型中也可不考虑此结构的影响。

图7:Limit Layer编辑

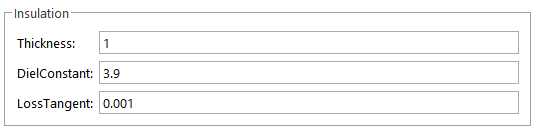

6. Insulation Layer 设置

在TSV Wizard中的Insulation编辑区域,用户可以指定TSV隔离氧化层的厚度和氧化物的Dk、Df值。在TSV的特性中,隔离氧化层对电性能影响较大,尤其在氧化层厚度较小时,导电柱和Silicon之间形成较大寄生电容,让信号的损耗随着频率上升急剧增加。

图8:Insulation Layer编辑

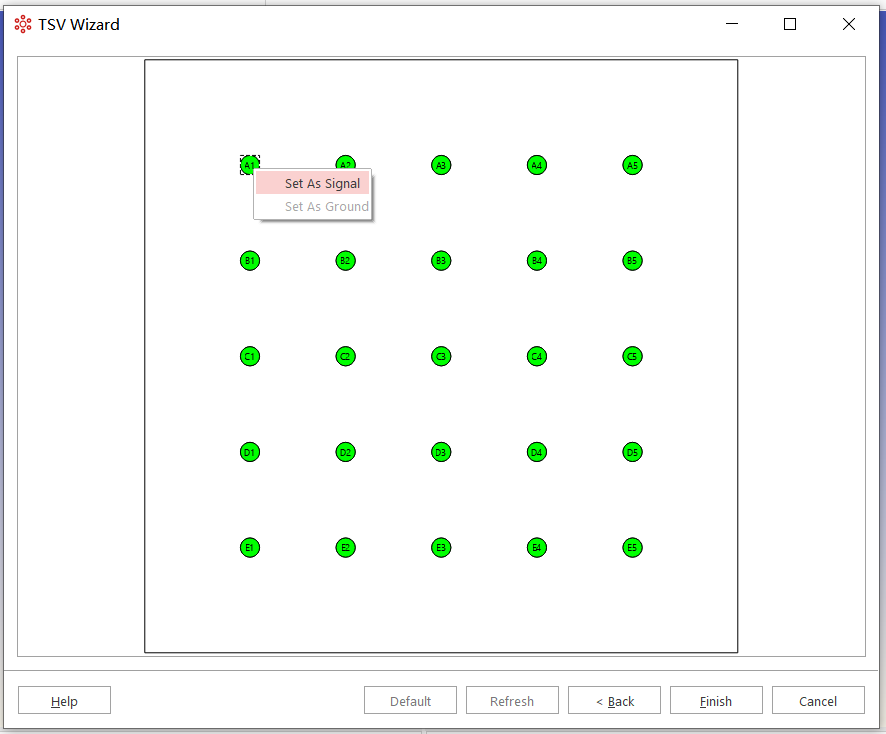

7. TSV Type 设置

在设置好以上参数以及模型的Boundary尺寸以后,点击Next,进入TSV种类的选择,用户可以根据设计需要将TSV阵列中TSV修改为Signal或者Ground类型。

图9:TSV类型编辑

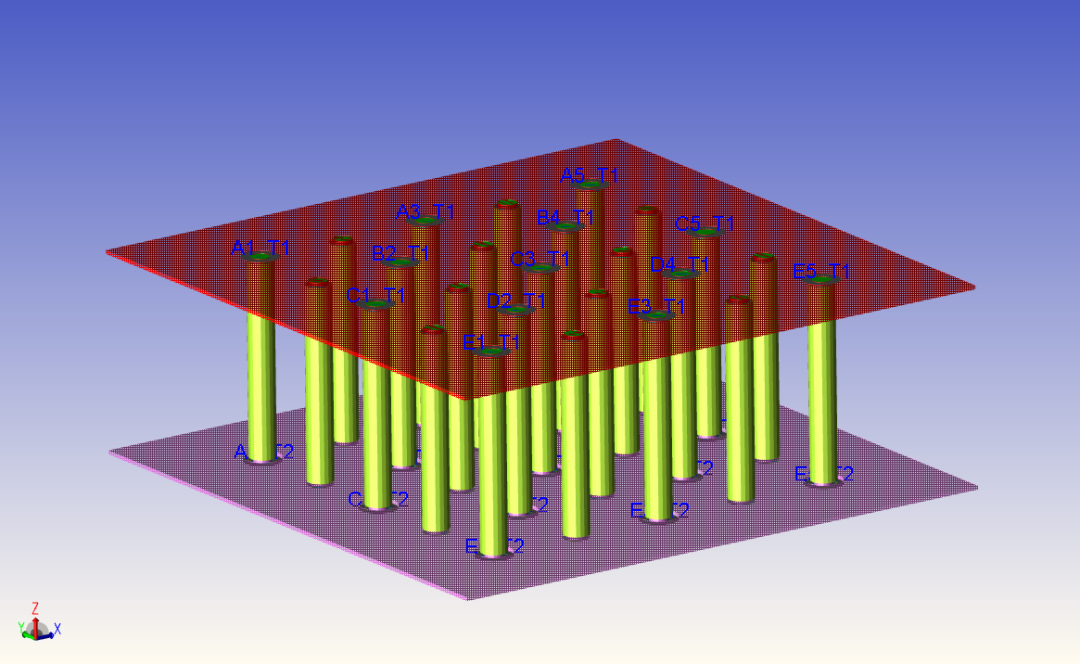

点击Finish,即可完成TSV阵列的建模,仿真模型的Port会自动进行添加。

图10:TSV阵列3D视图

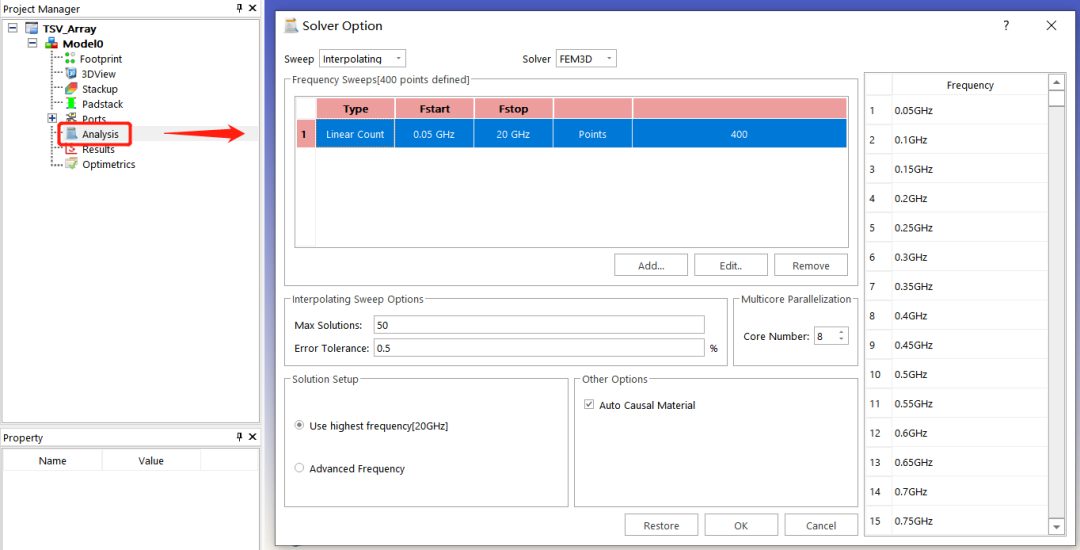

8. 求解器设置和启动

在Project Manager中右键Analysis进入Solver Option界面,用户可以根据要求选择S参数扫频范围、收敛条件以及Core Number等设置。

图11:求解器设置界面

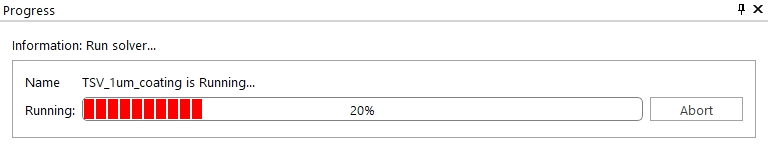

在Project Manager中右键Analysis,选择Run Solver,求解器将开始对整个TSV阵列的结构进行S参数求解。在Progress的状态栏里可以查看仿真的进度。

图12:仿真进度窗口

9. 仿真结果查看

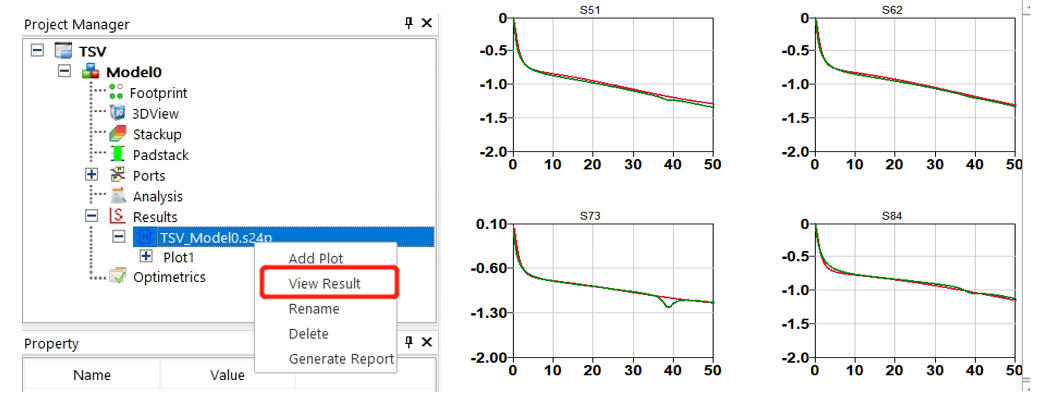

仿真完成以后,在Project Manager中Results下方会生成相应S参数结果,右键选择View Result可在SnpExpert中对仿真结果进行查看和分析。

图13:S参数分析窗口

总结本文介绍了采用芯和半导体ViaExpert软件进行TSV阵列建模与仿真分析的完整流程,步骤包括:Padstack编辑、Stackup和Materials编辑、阵列编辑、隔离层设置、TSV类型选择等。通过预制模板的方式建立TSV阵列,用户可以有效地提高TSV建模和仿真效率,加快芯片的设计和迭代。

原文标题:【应用案例】如何进行“TSV阵列的建模和仿真”?

文章出处:【微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

-

建模

+关注

关注

1文章

304浏览量

60765 -

TSV

+关注

关注

4文章

111浏览量

81463 -

viaexpert

+关注

关注

0文章

3浏览量

1902 -

芯和半导体

+关注

关注

0文章

103浏览量

31415

原文标题:【应用案例】如何进行“TSV阵列的建模和仿真”?

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何使用串口工具连接OneNET上报数据AT命令流程的代码详细说明

FPGA设计的全部流程详细说明

LTE簇优化流程和案例介绍详细说明

TSV阵列建模流程详细说明

TSV阵列建模流程详细说明

评论