嵌入式 FPGA (eFPGA) 技术并不是一个新概念。事实上,它已经以各种形式实施了几十年。那么,为什么它会突然受到如此多的关注呢?答案在于半导体行业内两个基本经济趋势的交汇处。

首先,每一代新工艺的开发成本都在急剧上升。这些是由抽象设计本身以及这些设计在实际 SoC 设备中的物理实现日益复杂的驱动,包括软件工具、工程时间和掩模成本等项目。

其次(反之亦然),这些设备中每单位功能的成本一直在下降。例如,二十或三十年前,FPGA 门相对昂贵,因此 FPGA 设备倾向于用于原型设计和预生产,而不是大批量生产应用。尝试将 FPGA 门添加到 ASIC 通常会增加整体裸片尺寸和复杂性,以至于新的混合设备变得过于昂贵而无法实用。现在这不再是真的了。

相反,SoC 设计中涉及的高成本增加了与没有完全正确的产品来满足特定市场需求相关的风险,而 FPGA 门的成本相对较低意味着嵌入 FPGA 技术可以获得一定程度的设计灵活性(从而降低市场风险)具有经济意义。

eFPGA 技术的优势

然而,除了解决这两个主要经济趋势带来的挑战之外,基于 eFPGA 的设计方法还提供了许多其他潜在的好处。例如,通过将 eFPGA IP 放置在与 SoC 中的其他功能块相同的硅片上,它可以与设计的其余部分具有低功耗、低延迟、非常高的带宽连接。结果是,与 ASIC 加分立 FPGA 解决方案相比,具有嵌入式 FPGA 块的 ASIC 可以具有更低的功耗、更高的性能、更低的成本和更少的电路板空间,同时仍保持设计灵活性。

eFPGA 的另一个优势是 FPGA 的可重新编程特性使设计团队能够轻松地调整他们的 SoC 以适应新的、快速变化的或在制造后略有不同的市场需求,从而延长产品的上市时间并增加收入、毛利率、和整体盈利能力。SoC-with-eFPGA 特别有效的例子包括快速支持新的或不断发展的接口标准,添加新功能以快速应对新兴的竞争威胁,或以具有成本效益的方式为高度分散的市场(如互联网)创建多种产品变体物联网 (IoT)。

最后,将 eFPGA 技术添加到 SoC 设计中可以提高整体设计性能,同时降低总功耗。某些功能在 FPGA 逻辑中实现的性能或功率效率更高,特别是如果它们需要像当今大多数 SoC 设计中那样具有片上处理器的灵活性时。此外,通过采用大多数嵌入式 FPGA 技术的可重新编程方面,设计工程师可以创建基于硬件的解决方案,这些解决方案可以重新配置以适应手头的特定问题,从而进一步提高设计性能并降低功耗。

实施注意事项

为了最有效地获得嵌入 FPGA IP 的好处,设计团队必须考虑其 eFPGA 实施的各个方面。首先要考虑的是综合工具与设计流程其余部分之间的集成质量。综合工具应明确支持 eFPGA 架构,并应能够生成优化设计网表以实现高效设计。例如,QuickLogic 与 Mentor 合作为其 eFPGA 技术提供设计和开发环境——特别是 Mentor 的 Precision Synthesis 软件,该软件经过优化以支持公司 eFPGA IP 中使用的 QuickLogic ArcticPro 架构。

综合在设计过程中起着关键作用,因为它对设计的结果质量 (QoR) 影响最大。QoR 指标是多维的——它可能是频率、面积和功率的函数,具体取决于用户的设计要求。对于综合工具而言,当前支持诸如 Verilog、SystemVerilog (SV2009) 和 VHDL (VHDL-2008) 等行业标准 HDL 语言以实现设计输入的灵活性非常重要。而且,为了获得最佳 QoR,综合工具必须深入了解目标架构,以最佳地映射到架构中可用的资源。

设计流程中的第二个考虑因素是 eFPGA 实现本身的软件质量,因为它将最终决定 SoC 器件的效率、性能和成本。FPGA 架构及其相关的开发工具往往会共同发展,因为其中一个的变化可能会对另一个产生巨大的影响。因此,已出货数百万个 FPGA 并拥有数十年开发用于为数千个实际应用中的这些设备提供设计支持的软件经验的公司更有可能提供良好的 eFPGA IP/软件解决方案。

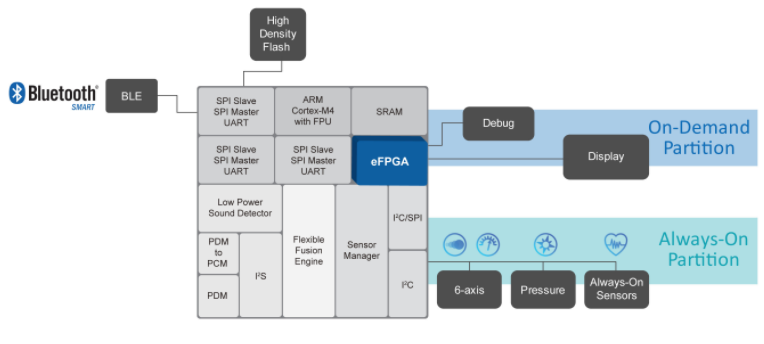

在某些情况下,经验丰富的 FPGA 供应商还学会了如何将 eFPGA 技术有效地集成到他们自己的 SoC 设备中,这使他们能够通过充当自己的技术客户来进一步完善他们的 eFPGA IP 产品。例如,QuickLogic 为可听、可穿戴和物联网应用开发了传感器处理 SoC(图 1)。该设备包括 eFPGA 技术,因为该公司了解到,拥有可编程逻辑块可以让他们的客户快速实施新的传感器处理算法和接口标准。

【图1 | EOS S3传感器处理平台框图]

作为 eFPGA 工具本身的用户,QuickLogic 工程师很快了解了他们需要哪些工具以及如何最好地优化 eFPGA 实现设计流程。在此过程中,他们遇到了各种问题并加以解决,最终创建了成功的 eFPGA IP 集成所需的全套工具和设计文件。

这些工具生成的一些文件包括设备包装文件、反向注释文件和布局数据。设备封装文件是一个网表,它定义了 eFPGA“黑盒”端口以及它们如何连接到 SoC 设计的其余部分。背面注释文件提供对设计验证过程至关重要的库和时序信息。布局数据包括设计团队可用于实例化物理设计块的物理布局信息。

eFPGA 在人工智能、物联网、安全和其他应用中的用途

SoC 显然用于广泛的应用,添加嵌入式 FPGA 技术只会扩展潜在的用例集。但是,在一些应用示例中,采用 eFPGA 的 SoC 解决方案提供了优于传统 SoC 的显着优势。

我们已经回顾了传感器处理,其中 EOS S3 SoC 的嵌入式 FPGA 部分可以实现快速传感器算法和接口更新,而无需流片新版本的设备。与基于云的人工智能相关的语音处理是人机交互的下一个重要步骤,它能够为支持“智能扬声器”产品(如亚马逊的 Alexa)的生态系统快速轻松地添加新的触发词。

高度分散的物联网市场是 eFPGA 技术可以提供实质性好处的另一个很好的例子。整体市场是巨大的,但很少有个别应用程序本身会有大量的市场需求。因此,对于 SoC 设计人员来说,采用基于平台的方法是有意义的,他们的“基础”设备可以实现每个应用程序共有的所有功能。然后,eFPGA 技术可用于快速且经济高效地创建多种产品变体,以满足特定应用的需求。也可以解决突然出现的新应用,而无需花费与重新设计 ASIC 相关的时间和成本。

包括大数据和深度学习在内的几乎所有机器学习应用程序都可以利用大多数 eFPGA 解决方案提供的可重构特性。eFPGA 模块中的硬件可以根据需要进行配置,然后重新配置,以经济高效地解决当今计算机解决的一些最复杂的问题。

另一个很好的例子,也是现在特别相关的一个例子,是需要不断更新基于硬件的安全算法。随着新的安全漏洞或漏洞被发现,提供更新的防御性解决方案变得至关重要——非常适合 SoC 中的 eFPGA 硬件。

eFPGA 技术的未来

鉴于开发和单位成本趋势将使嵌入式 FPGA 技术对 SoC 设计团队更具吸引力,eFPGA IP 的未来非常光明。然而,与每一项复杂的技术一样,也存在一些挑战。其中之一是,一种尺寸并不适合所有情况,eFPGA IP 架构、尺寸和技术以及跨不同代工厂和工艺节点的 SoC 实现有很多很多可能的组合。还存在与需要不同数量的金属层、管理时钟域边界以及协调不同的电源管理方案相关的潜在集成问题。

尽管 eFPGA 技术已经以各种形式出现已经有一段时间了,但市场才刚刚从早期采用阶段进入主流阶段。这种趋势只会在短期内加速。示例应用程序和最终产品变得越来越容易找到,范围从移动设备、可听设备、可穿戴设备和物联网到大数据和通信中心,再到可重新配置的计算平台,再到基于云的人工智能。

然而,只有将可编程逻辑有效地集成到 SoC 中,eFPGA 技术才会成功。这需要技术、架构和软件工具的正确组合,以便开发团队拥有完整且有效的设计流程,使他们能够无缝地从概念到工作芯片,再到制造后的市场调整和准备发货的产品。

审核编辑:郭婷

-

传感器

+关注

关注

2550文章

51035浏览量

753048 -

嵌入式

+关注

关注

5082文章

19104浏览量

304771 -

soc

+关注

关注

38文章

4161浏览量

218152

发布评论请先 登录

相关推荐

TMS系统的实施步骤与注意事项

FPGA的高速接口应用注意事项

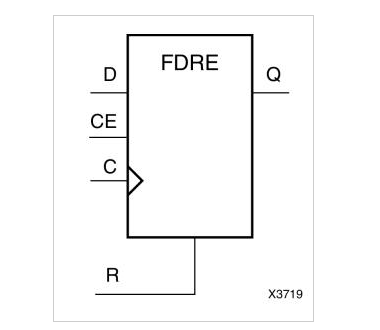

向FPGA设计添加复位功能的注意事项

eFPGA技术的应用优势和实施注意事项

eFPGA技术的应用优势和实施注意事项

评论