1. 块语句有两种,一种是 begin-end 语句, 通常用来标志()执行的语句;一种是 fork-join 语句,通常用来标志()执行的语句。

答案:顺序,并行

解析:

(1)begin_end顺序块,用于将多条语句组成顺序块,语句按顺序一条一条执行(除了带有内嵌延迟控制的非阻塞赋值语句),每条语句的延迟时间是相对于由上一条语句的仿真时间而言;

(2)fork-join并行块,块内语句同时执行。

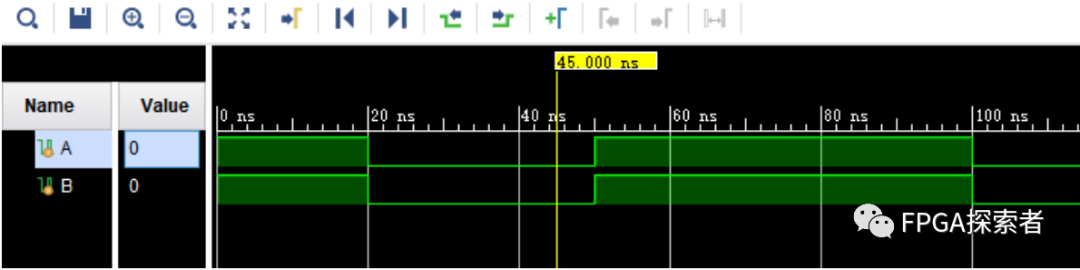

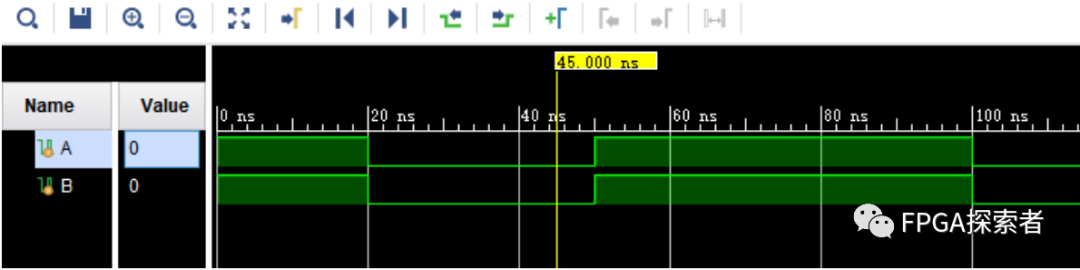

2. 块语句,下面这段语句中,第 40 时刻上,A、B 的值各是多少?

reg A;reg B;initial begin fork begin A = 1; #20 A = 0; #30A=1; #50 A = 0; end begin B = 1; #20 B = 0; #30 B = 1; #50 B = 0; end joinend

答案:A = 0,B = 0

解析:

块语句有两种,begin...end 和 fork...join,其中 fork...join 是并行块,begin...end 是顺序执行块,可以相互嵌套。

上面,两个 begin...end 之间是并行的,而各自 begin...end 内部是顺序执行,A 和 B 的赋值逻辑是一样的,所以要么都是 1,要么都是 0。

按照顺序执行,A 前 20 个时间单位是 1,然后持续 30 个时间单位的 0,所以 40 时刻是 0,同理 B 也是 0。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:Verilog 的块语句 fork...join 和 begin...end

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

相关推荐

本文继续介绍Verilog HDL基础知识,重点介绍赋值语句、阻塞与非阻塞、循环语句、同步与异步、函数与任务语法知识。

![的头像]() 发表于

发表于 10-24 15:00

•337次阅读

MX_GPIO_Init初始换函数结尾没有begin end用户编辑区域,但是在其他初始化函数后有编辑区域,并且在main.c文件每个初始化后方也没有用户编辑界面,如果想要在初始化结尾做一些事情,在

发表于 09-26 06:08

;

hit_ID <= 3\'d0;

end

else begin

case (state)

state_4: begin//第四列判断

if(sync_valid[3]) beg

发表于 09-22 20:56

... default ... endcase

7、连续赋值:assign, 问号表达式(?:)

8、always模块:敏感表可以是电平、边沿信号

9、begin...end(代码块?)

10、任务定义

发表于 06-23 14:58

,因为always语句块是并行执行的,会产生冲突。

always@(敏感信号)begin

语句;

end

②、assign和always

发表于 05-31 18:31

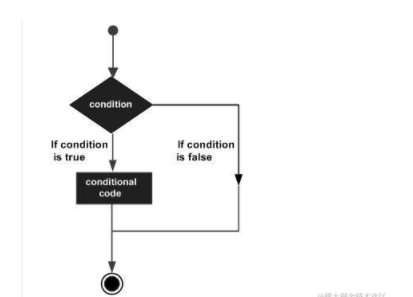

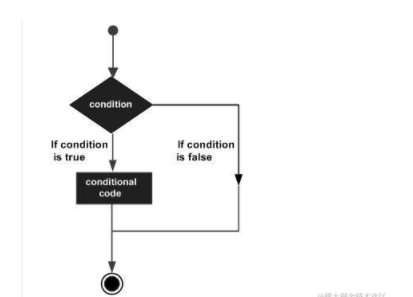

条件语句用于基于不同的条件来执行不同的动作。

TypeScript 条件语句是通过一条或多条语句的执行结果(True 或 False)来决定执行的代码块。

![的头像]() 发表于

发表于 04-01 13:51

•751次阅读

state_next = START;

data_out[9:8] = 2\'b10; // K28.5

end

end

START: begin

state_next = DATA;

data_out[2:0

发表于 03-26 07:55

else begin

data_a_reg <= data_in_a;

data_b_reg <= data_in_b;

end

end

// 执行卷积运算

always

发表于 03-26 07:51

;lt;= 0;

end else begin

if (sec_cnt == MAX_SECONDS) begin

sec_cnt <= 0;

if (min_cnt

发表于 03-26 07:48

, mantissa} = a; // 将a中的符号位、指数部分和尾数部分提取到对应变量中

end

always @(posedge clk) begin

if (reset == 1\'b1) begin

sum

发表于 03-25 21:49

Verilog中的模块端口对应方式,并提供示例代码和详细解释,以帮助读者更好地理解和应用。 首先,我们来了解一下Verilog中的模块和模块端口。一个Verilog模块被定义为包含一组声明和语

![的头像]() 发表于

发表于 02-23 10:20

•1745次阅读

在Verilog中,repeat语句不需要使用begin和end块。repeat语句是一种循环控

![的头像]() 发表于

发表于 02-23 10:14

•1187次阅读

Assign语句和Always语句是在硬件描述语言(HDL)中常用的两种语句,用于对数字电路建模和设计。Assign语句用于连续赋值,而Always

![的头像]() 发表于

发表于 02-22 16:24

•2530次阅读

Verilog是一种硬件描述语言(HDL),用于设计和模拟数字电路。在Verilog中,关键字initial和always都是用于描述电路行为的特殊语句。它们被用来生成仿真模型,并控制模拟器的启动

![的头像]() 发表于

发表于 02-22 16:09

•2826次阅读

单片机中的if语句是一种条件语句,用于根据不同的条件执行不同的代码块。在程序执行过程中,条件语句用来决定是否执行特定的代码段。在单片机编程中,if语

![的头像]() 发表于

发表于 01-05 14:04

•1756次阅读

Verilog的块语句fork...join 和 begin...end

Verilog的块语句fork...join 和 begin...end

评论