更小硅几何尺寸的不断进步使嵌入式设备(尤其是微处理器)的工作电压更低。处理器内核的工作电压现在低至 1.2 V,并迅速升至 0.8 V,这对设计人员如何有效地为这些设备供电提出了挑战。与使用线性稳压器为低压设备供电的传统方法相反,在这些应用中使用开关稳压器可以帮助解决这个问题。根据系统要求,设计人员可以使用各种架构来最大限度地提高开关稳压器的效率。

典型的低功耗嵌入式处理器消耗 300-600 mA。在内核电压为 3.3 V 的老一代处理器中使用开关稳压器几乎没有什么好处。然而,降低核心电压为提高效率提供了重要机会,尤其是在由锂离子电池 (4.2 V) 或 5 V 轨供电时。例如,4.2 V 系统中的线性稳压器在调节到 1.2 V 时会浪费 1.8 W [(4.2-1.2 V) x 600 mA]。相比之下,开关稳压器在相同电压下的效率最高可达 95%条件,这会给系统增加大量的运行时间。

开关稳压器产生的潜在噪声、轻负载时的低效率以及对更复杂控制的需求传统上阻碍了设计人员将此类稳压器用于嵌入式处理器。此外,线性稳压器的占地面积更大,使线性稳压成为首选方法。尽管如此,设计人员仍可以采用多种技术来大大提高开关电源的效率,并使开关稳压器在不同类型的设计中可行。具有集成控制器、传输器件和补偿组件的单个 IC 使开关稳压器的设计密集度降低,实施起来更具成本效益。

标准降压拓扑

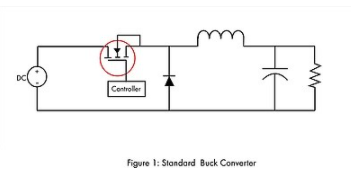

一个简单的降压开关包括场效应晶体管 (FET)、二极管、电感器、电容器和控制器,如图 1 所示。在此拓扑中调节输出电压涉及改变 FET 栅极上的占空比以增加或减少通过电感器的电流,一种称为脉冲宽度调制 (PWM) 的方法。PWM 开关稳压器在满载运行时的效率可高达 95% 以上。然而,当在轻负载下运行时,开关稳压器的效率会显着下降,这对于在不断变化的负载条件下运行或需要低电流或睡眠模式的系统来说是不可取的。

图1

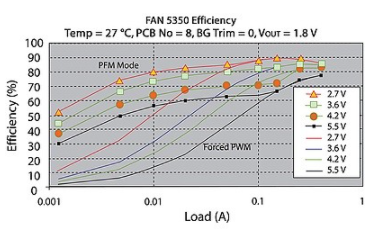

为了克服开关稳压器在轻负载条件下效率低下的问题,设计人员可以将稳压器置于脉冲跳跃或脉冲频率调制 (PFM) 模式。在 PFM 模式下,开关稳压器中的 FET 仅在输出电压低于下限时工作。这减少了脉冲数量,进而减少了通过 FET、电感器和二极管的开关损耗,从而提高了轻负载条件下的效率。对于图 2 所示的器件,稳压器以大约 100 mA 的电流从 PFM 转换为 PWM,从而在整个输出电流范围内最大限度地提高效率。

图 2

在使用 PFM 稳压器进行设计时,设计人员必须考虑使用它的应用。由于切换器的频率随输出负载而变化,因此切换频率可能会降至音频频段,这可能会产生不良噪声问题。幸运的是,当今市场上可用的某些工具可以确保频率永远不会进入音频频带。尽管这些工具可能会导致轻负载下的效率略有下降,但它们可以为设计人员节省无数时间来消除噪声问题。

同步拓扑

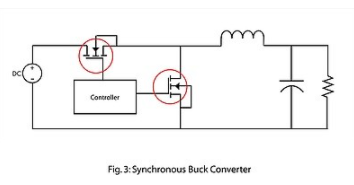

设计人员可以使用同步拓扑进一步提高开关的效率,如图 3 所示。这种拓扑可以通过用低 R ds(on) FET 替换二极管来降低开关损耗和二极管的反向恢复损耗。

图 3

在此拓扑中,同步切换的时序至关重要。如果两个 FET 都导通,则每个周期都会损失功率,效率会受到影响。此外,设计人员必须考虑选择哪些器件。例如,FET 的栅极电容是一个重要的变量,因为它可以在控制器关闭 FET 后保持低侧 FET 导通。在栅极保持充电的短时间内,输入电源直接分流到地。R ds(on)和 FET 的栅极电容将对这种拓扑的效率影响最大;因此,优化两者很重要。

在上述拓扑中,当电路板空间非常有限时,使用更高的开关频率可能是有利的。更高的开关频率允许设计人员使用更小的无源元件,例如电感器和输出电容器,这可以降低设计成本和整体占位面积。然而,这是以降低效率为代价的。当频率增加时,FET 开关的次数增加,这反过来又增加了损耗。此外,较小的电感器和电容器可能会在输出电压上产生较高的纹波。

多相拓扑

为了克服当今严格的纹波要求,同时保持嵌入式设计的效率,设计人员可以使用多相 DC-DC 开关。这种拓扑结构可以降低开关损耗,同时有效提高稳压器的开关频率。

例如,考虑连接到负载 I load的单相 DC-DC 同步开关。通过每个 FET 的开关损耗为 I 2 R 或 I load 2 * R ds(on)。在多相设计中,每个 FET 的开关损耗相同。但是,每相中的电流除以相数。因此,可以通过以下方式降低两相设计中的开关损耗:

此外,多相设计改善了稳压器的纹波电流和瞬态响应时间。这会增加成本和占位面积,因为必须为每相添加一个电感器和两个 FET,并且控制器变得更大、更复杂。

缩小选项

电源效率是满足便携式产品延长电池寿命需求的关键。处理器制造商通过降低工作电压来帮助这项工作,但电源必须适应以最大限度地提高效率。在决定最高效的电源时,检查变量以确保电源满足处理器要求非常重要。电源成本也必须是决策的一部分。

标准降压开关在 PWM 模式下运行时可提供效率,并且比同步降压更简单,因此是一种更便宜的选择。但是,二极管会产生电压降,从而浪费一些功率。同步降压使用 FET 代替二极管来降低此电压降,从而提高效率但成本更高。

当处理器处于睡眠模式时,多模式稳压器通过从 PWM 切换到 PFM 来提高整个负载范围内的效率。这会增加一些输出纹波电压,但只要它保持在处理器的功率规格范围内,就会显着提高电池寿命。多相稳压器在保持效率的同时消除了大部分输出纹波电压,但成本也更高。

设计人员在为嵌入式处理器设计电源时可以遵循这些指南。所有设计都需要权衡取舍,电源也不例外。考虑到任何设计的预算限制、电源要求和效率目标,这些策略将有助于缩小选择范围,以确定提供三者最佳折衷的电源。

作者:Brian Law,Greg Ferrell

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19259浏览量

229647 -

嵌入式

+关注

关注

5082文章

19104浏览量

304779 -

稳压器

+关注

关注

24文章

4223浏览量

93759

发布评论请先 登录

相关推荐

英特尔发布至强6处理器产品

充电也要算法?储能充电芯片中的算法处理器

浪潮信息分布式存储AS13000完成英特尔至强6能效核处理器适配

采用144核,能效提升66%!英特尔至强6处理器震撼上市,加速数据中心升级

差分可编程振荡器,频点50MHz,LVDS输出,应用于音视频处理器

英特尔发布至强6能效核处理器

英特尔首发数据中心能效核处理器,144核高密度,机架密度提升3倍

重磅!英特尔发布intel3制程至强6能效核处理器,赋能数据中心能效升级

英特尔®至强®6能效核处理器:Intel 3开山力作,每瓦性能提升2.6倍

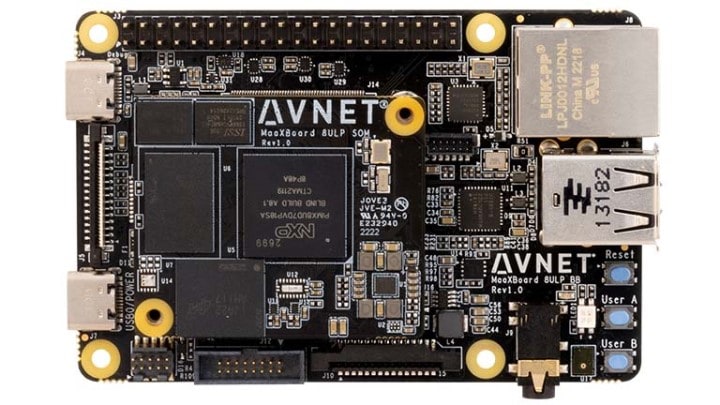

构建强大、高能效的i.MX 8ULP应用处理器合作生态体系

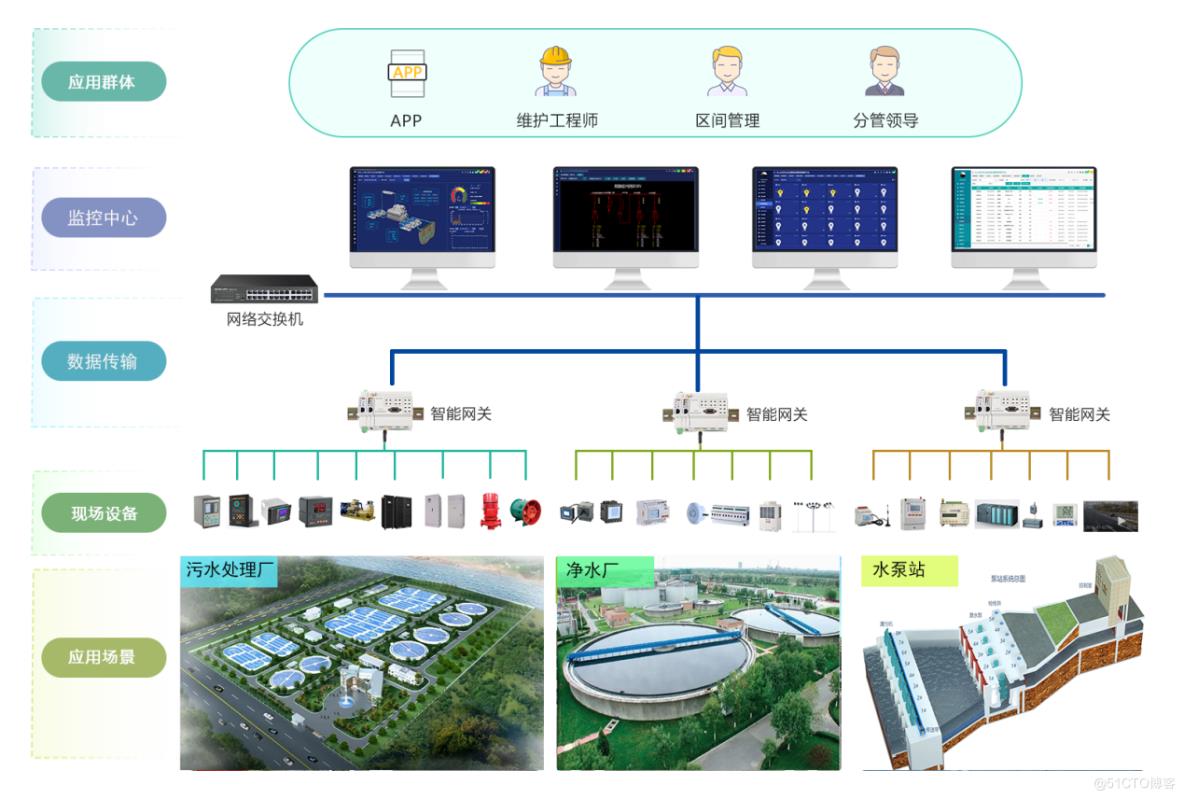

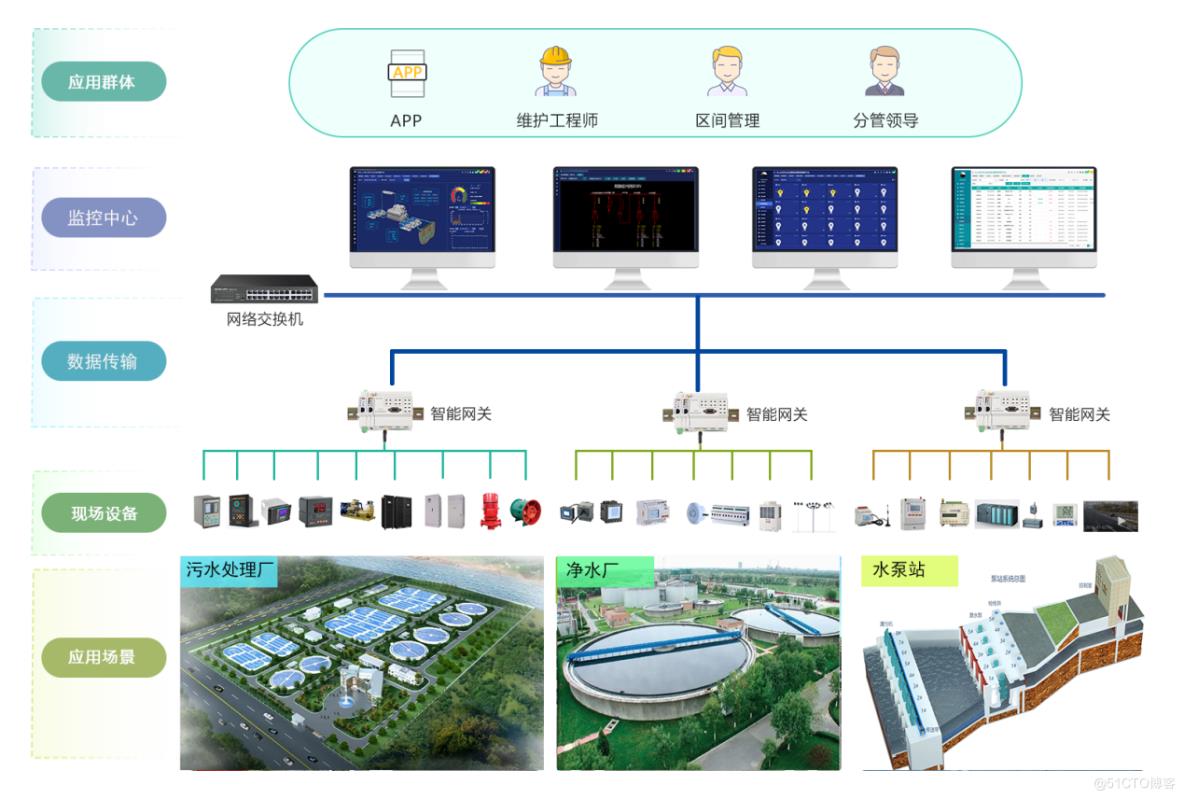

智慧水务能效管理平台-为污水处理的能效管理提供科学、精细的解决方案

AMD EPYC 8004系列处理器优势介绍

提高处理器能效的切换策略

提高处理器能效的切换策略

评论