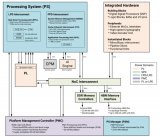

Versal 自适应计算加速平台( ACAP )将标量引擎( Scalar Engine )、自适应引擎( Adaptable Engine )和智能引擎( Intelligent Engine )与领先的存储器和交互技术有机结合,从而为任何应用提供强大的异构加速功能。最重要的是,Versal ACAP 硬件和软件是专为数据科学家和软硬件开发者开展编程和优化工作而提供的。Versal ACAP 受到诸多工 具、软件、资源库、IP、中间件和框架的广泛支持,适用于所有业界标准的设计流程。

本文档涵盖了以下设计进程:系统和解决方案规划,即确认系统级别的组件、性能、I/O 和数据传输要求,包括解决方案到 PS、PL 和 AI 引擎的应用映射。同时,本指南旨在提供 Versal ACAP 的高层次综述,如下所示:

·第 2 章:系统架构:提供 Versal ACAP 概述,包含每个高层次集成块的摘要,其中包括每个块的用途以及彼此之间的关联。

·第 3 章:系统规划:描述每个 Versal 器件系列与不同系统设计类型和设计流程之间的关联。

·第 4 章:设计流程:描述赛灵思设计工具和支持用于 Versal ACAP 的设计流程。

·第 5 章:系统移植:为以 Versal ACAP 为目标的设计提供高层次系统移植建议以及每个块的移植信息。

由于篇幅有限,本文仅节选了部分关于系统规划的内容。如果您希望查阅完本设计指南的其他内容,请至文末点击链接下载完整版。

系统规划

要正确规划系统,您必须根据自己的目标应用或系统设计类型明确系统要求。其中包括识别具有正确特性(例如, DDRMC IP 数量、AI 引擎等)的相应 Versal 器件。

系统设计类型

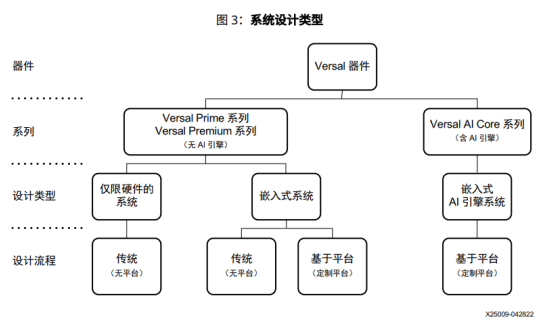

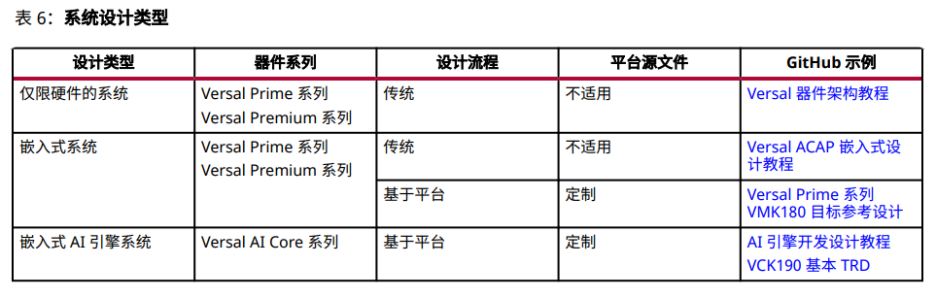

Versal ACAP 属于异构计算平台,具有多个计算引擎。在 Versal ACAP 上可映射各种应用,包括对无线系统、机器学习推断和视频处理算法进行信号处理。除了多个计算引擎外,Versal ACAP 还可使用高速串行 I/O、片上网络( NoC )、DDR4/LPDDR4 存储器控制器和多重速率以太网媒体访问控制器( MRMAC )来提供超高系统带宽。Versal 器件分类为 Versal Prime 系列、Premium 系列和 AI Core 系列。下图显示了每种 Versal 器件系列所支持的不同系统设计类型和设计流程。

下表显示了每种 Versal 器件系列所支持的系统设计类型和设计流程。如该表中所示,大部分设计流程都以构建平台为基础。

点击对应图片查看详细内容

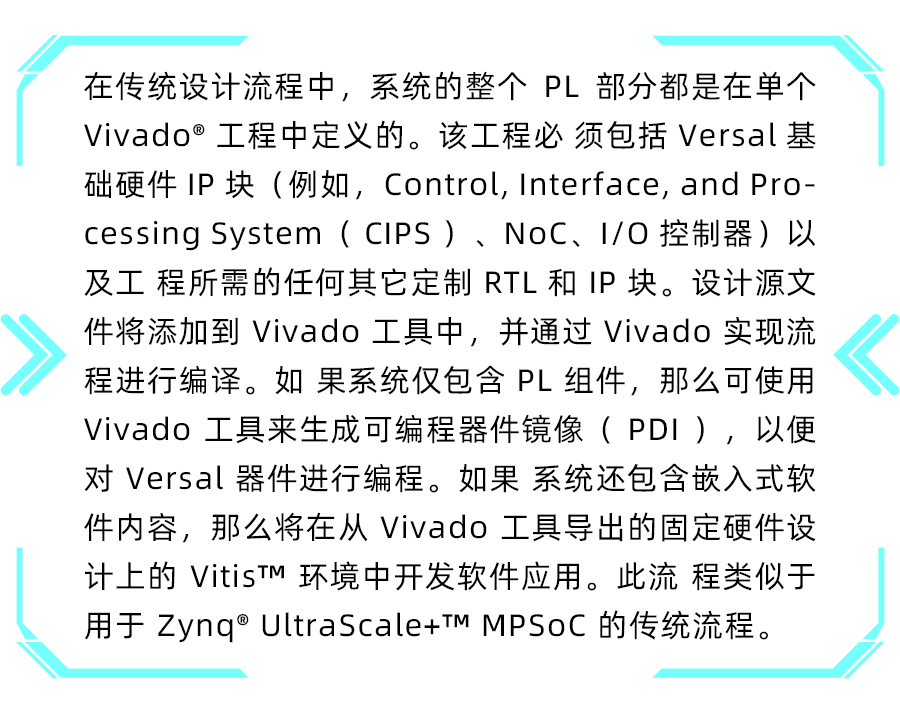

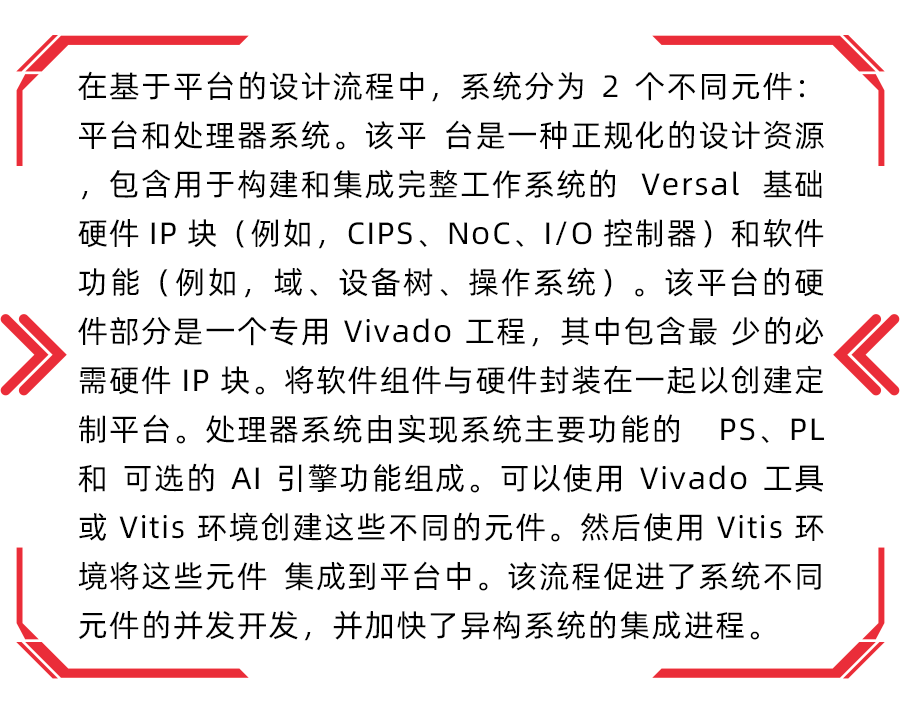

在设计流程中使用 Vitis 环境

Vitis 环境由工具、库和 IP 组成,支持您对 Versal ACAP 应用的不同要素进行编程、运行和调试,包括AI 引擎内核与图、可编程逻辑( PL )函数以及处理器系统( PS )上运行的软件应用。Vitis 工具使用基于平台的方法,其中系统按概念分为以下要素,这些要素可并行开发和测试:

平台

自适应子系统

软件应用

Vitis 环境设计方法论

要求:开始开发前,您必须选择最适合您的应用的 Versal 器件,然后根据应用要求按功能目标(PS、AI 引擎和 PL)对设计进行分区。在此情况下,您必须了解:

系统设计注意事项,例如吞吐量和时延

域功能以及域间功能,包括计算和带宽

整个系统和各子系统中的数据流和控制流程

此外,您必须注意平台的目标类型。您必须规划并设计开发板上的外设和接口以及定制开发板上可用的存储器资源。

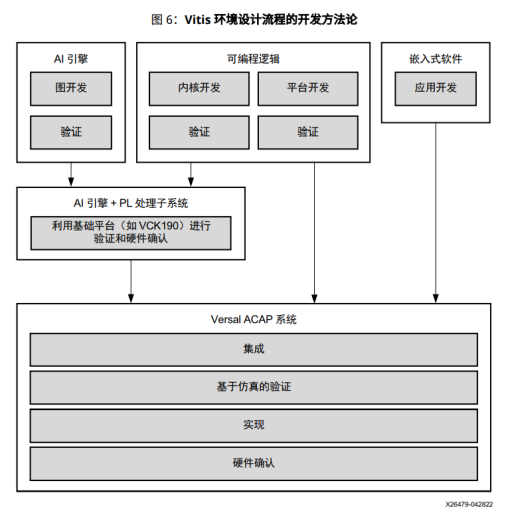

方法论概述:下图显示了基于 Vitis 环境设计流程的开发方法论的高层次表示法。

Vitis 环境开发方法论反应了 Versal ACAP 系统的异构性质,此类系统通常是由 PS、PL 和 AI 引擎功能组成的。您可使用 Vitis 工具来独立开发并验证这些组件,并逐渐将其加以集成以构成最终系统。

Vitis 环境设计流程是迭代性流程,可能多次循环执行每个步骤,并通过后续迭代来向自适应系统添加更多层级或元件。各团队可以快速迭代早期步骤,将更多时间用于后续步骤,以便提供更详细的性能数据。

最佳实践:Vitis 环境设计方法论的基础是迭代方法和并行开发。因此,强烈建议您采用如下最佳实践:

并行开发自适应子系统和定制平台。

对系统进行精确分区,即上述两个要素可各自单独开发和验证,从而节省时间和精力。

单独调试并验证 AI 引擎图和每个 PL 内核,然后再进行集成。

采用此方法可以尽可能提升在集成阶段快速融合的可能性。已知所有组件都正确无误的前提下,集成问题的调试难度大大降低。

使用标准AMD赛灵思平台(例如,VCK190)来集成并验证由 AI 引擎图和 PL 内核组成的自适应子系统,然后再将目标瞄准定制平台。

AMD 赛灵思平台都经过预验证,可立即部署到硬件上。通过使用标准 AMD 赛灵思平台,AI 引擎图和 PL 内核的开发者即可使 用仿真或硬件开发板来验证自适应子系统,同时可以避免定制平台的不确定性和复杂性。

确保在流程每个阶段都能满足性能目标。

在硬件中运行完整系统与在隔离环境中对个别组件进行仿真相比,性能结果并无明显改善。因此,有必要在流程中尽早对任何性能问题进行完整检查和调试。在组件级别确保满足性能目标难度远低于在包含所有组件间交互的复杂系统环境内满足性能目标。

审核编辑 :李倩

-

Versal

+关注

关注

1文章

158浏览量

7656 -

ACAP

+关注

关注

1文章

54浏览量

8162

原文标题:Versal ACAP 设计指南

文章出处:【微信号:赛灵思,微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

使用 AMD Versal AI 引擎释放 DSP 计算的潜力

使用AMD Versal AI引擎加速高性能DSP应用

ALINX VERSAL SOM产品介绍

一个更适合工程师和研究僧的FPGA提升课程

各类常用混频器的高层次设计和优缺点

赣江新区党工委专职副书记罗进走访慰问我司高层次人才骆建辉!

AMD发布第二代Versal自适应SoC,AI嵌入式领域再提速

在Vivado中构建AMD Versal可扩展嵌入式平台示例设计流程

AMD Versal AI Edge自适应计算加速平台之PL LED实验(3)

AMD Versal AI Edge自适应计算加速平台PL LED实验(3)

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

AMD Versal AI Edge自适应计算加速平台之Versal介绍(2)

Versal ACAP的高层次综述

Versal ACAP的高层次综述

评论