本发明涉及一种在集成电路制造中减少漏电流的方法,更具体地说,涉及一种在集成电路制造中通过新的预氧化清洗顺序减少超薄栅氧化物漏电流的方法。

根据本发明的目的,实现了一种预氧化清洗衬底表面的新方法。我们华林科纳使用多步清洗工艺清洗晶片的半导体衬底表面,其中清洗工艺的最后一步包括用HMSO和HCO的溶液清洗,由此在晶片表面上形成化学氧化物初始层。此后,晶片的表面被氧化以形成热氧化层,其中在集成电路的制造中,化学氧化层和热氧化层一起形成栅氧化层。

优选实施例的描述

现在更具体地参考图1,示出了部分完成的集成电路的一部分电路。示出了优选由单晶硅构成的半导体衬底10。集成电路器件的每个有源区将与其他有源区隔离。例如,硅的局部氧化(LOCOS)可以用于形成场氧化区,或者可以形成诸如12的浅沟槽隔离(STI)区。

对于深亚微米CMOS技术,栅极氧化层必须超薄,可能在15到20埃的数量级。为了减少漏电流,在形成超薄栅氧化层之前,半导体衬底的表面必须非常干净。

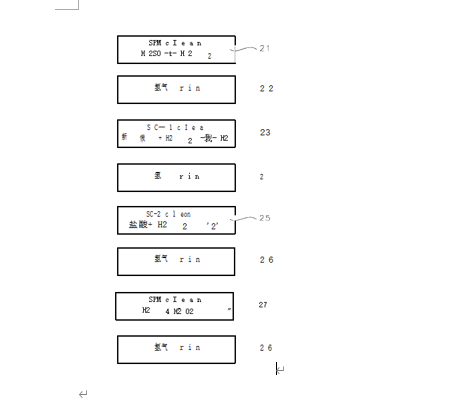

例如,图2是说明本发明优选实施例中的清洁步骤的流程图。首先,执行SPM清洁(21)。使用HMSO 4+HCO的溶液清洗晶片。然后用水冲洗晶片,通常是去离子水。该第一清洗步骤去除重金属离子和有机材料,例如抗蚀剂。

传统上,SPM清洁剂用于去除光刻胶或重金属离子。此时添加最终的SPM步骤并不明显,因为这些材料已经被去除。然而,发明人已经发现-

当使用本发明的新型预氧化工艺时,在漏电流方面获得了惊人的显著改善。

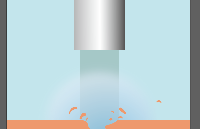

现在参考图3,初始化学氧化物层14显示在衬底的表面上。栅极氧化是50,以形成栅氧化层16。栅极氧化物层14和16具有约15至30埃的组合厚度。应当注意,附图不是按比例绘制的。氧化物层14/16非常薄。

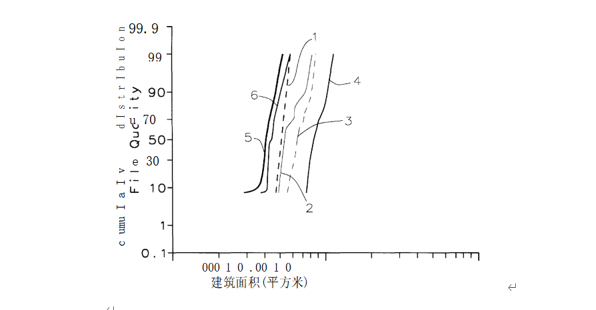

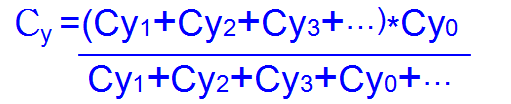

采用新型预氧化清洗工艺本发明的过程已经被实施和测试。测试中采用了各种预氧化清洗方法。泄漏电流密度60(埃/厘米')的厚度清洁过程。图5示出了NMOS的结果,图6示出了PMOS的结果。在这两个图中,fi1m质量的累积分布沿纵轴显示。横轴表示漏电流65密度。

本发明的方法(晶片号5)具有

NMOS和PMOS的最低漏电流密度值。

如本领域中常规的那样继续处理。可以在栅极氧化物层14/16上的有源区中制造半导体器件结构。例如,图4示出了具有侧壁隔离物24、源区和漏区26、通过绝缘层28和钝化层32接触源区和漏区之一的导电层30的栅电极20。

本发明的方法提供了简单的30

和降低漏电流有效方法,特别是对于超薄栅氧化层。本发明的新型氧化前清洗工艺执行SPM清洗作为最后的清洗步骤,从而形成初始化学物质

用盐酸+HCO+HCO清洗;和

在每个清洗步骤之后进行HCO漂洗,其中最后的清洗步骤包括用含有HMSO和HCO的溶液进行清洗。

5.根据权利要求1的方法,其中所述化学氧化物初始层的厚度约为10-12埃。

6.根据权利要求1所述的方法,其中所述热氧化层由包含快速热处理和炉处理的组中的一种形成。

7.根据权利要求1的方法,其中所述热氧化层的厚度在大约15和30埃之间。

8.根据权利要求1的方法,其中所述化学氧化物初始层和所述热氧化物层一起具有约15至30埃的厚度。

9.一种在晶片上集成电路的制造中形成栅氧化层的方法,包括:

用多步清洗工艺清洗所述晶片的半导体衬底表面,包括:用HMSO+HCO溶液清洗;

用NH,O,+HCO,+HCO清洗;用盐酸+HCO+HCO清洗;和

在每个清洗步骤之后进行HCO清洗,其中所述多步清洗工艺的最后一步包括用包含HMSO和HCO的溶液进行清洗,由此在所述晶片的所述表面上形成化学氧化物初始层;和

此后氧化所述晶片的所述表面以形成热氧化物层,其中在所述集成电路的制造中,所述化学氧化物层和所述热氧化物层一起形成所述栅极氧化物层。

10.根据权利要求9的方法,其中所述化学氧化物初始层的厚度在大约10和12埃之间。

11.根据权利要求9的方法,其中所述热

形成热栅极氧化物之前的氧化物层。化学氧化物层充当缓冲层,以防止热氧化期间硅表面粗糙化。

虽然已经参照本发明的优选实施例具体示出和描述了本发明,但是本领域技术人员将理解,在不脱离本发明的精神和范围的情况下,可以进行形式和细节上的各种改变。

审核编辑:符乾江

-

芯片

+关注

关注

455文章

50714浏览量

423113 -

集成电路

+关注

关注

5387文章

11530浏览量

361615 -

半导体

+关注

关注

334文章

27286浏览量

218043

发布评论请先 登录

相关推荐

MOS管泄漏电流的类型和产生原因

直流输电系统氧化锌ZnO电阻设计方案

电容器漏电流的产生原因和降低方法

金属氧化物压敏电阻的冲击破坏机理&高能压敏电阻分析

金属氧化物压敏电阻 (MOV) 概述:工作和应用

MOS管中漏电流产生的主要六大原因

氧化诱导期如何检测?

降低超薄栅氧化层漏电流的预氧化清洗方法

降低超薄栅氧化层漏电流的预氧化清洗方法

评论