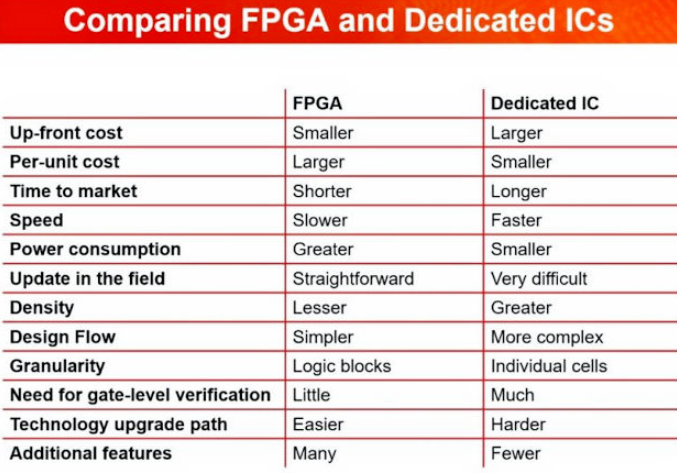

土耳其伊斯坦布尔 ElectraIC 总经理兼管理合伙人 Ates Berna 曾经在 LinkedIn 上发布了一份总结比较图表,展示了 FPGA 和 ASIC 之间的差异。

虽然这不是一个详细的图表,但我认为它是一个很好的破冰船,当你需要一个相当复杂的高性能、非标准 IC 来解决设计挑战时,它会导致关于你在 FPGA 和 ASIC 之间做出的选择。

我经常收到 FPGA 与 ASIC 的问题,我认为讨论 Berna 发布的图表很有价值。因此,这里对图表中的项目进行了更详细的逐行讨论:

这是我对这张图表的逐行讨论:

预付费:ASIC 的前期成本很高。首先,ASIC 开发工具的成本。您需要一个相当大的工具链来开发 ASIC,您必须租用或购买,并且您需要知道如何使用这些工具。如果您的设计团队没有这些知识,您需要将培训团队的成本包括在您的前期成本清单中。此外,您将产生相当大的 NRE(非经常性工程)费用,大约为数十万或数百万美元,您将支付给硅代工厂以构建您的 ASIC。NRE 费用用于支付掩模制造和检查,在代工厂繁忙的制造计划中预留一个位置来制造您的 ASIC、芯片测试和分拣、封装和最终测试。相比之下,FPGA 是现成的部件,因此没有代工 NRE 费用,FPGA 工具比 ASIC 设计工具便宜得多,大概低三个数量级。根据 FPGA 的不同,您甚至可以通过分销方式购买零件并在第二天获得。

单位成本:这就是 ASIC 大放异彩的地方。因为您通常设计 ASIC 以满足您的确切设计要求,所以您只购买您真正想要的硅片。很少或没有浪费。因此,假设您有预计的产品销量来证明创建 ASIC 的合理性,那么 ASIC 的单位成本应该低于 FPGA。这是因为 FPGA 的芯片开销很大。首先,您的设计可能无法 100% 使用任何给定的 FPGA。如果幸运的话,您可能会获得 90% 的利用率。通常,您可能无法使用多达 10% 或更多的 FPGA 资源来满足可布线性和时序目标,因为布线拥塞太大,并且如果您尝试使用整个 FPGA,信号会变得太长和太慢。此外,FPGA 上的信号路由矩阵非常丰富,以确保您可以在 FPGA 上路由您的设计。

上市时间:到目前为止,FPGA 是上市时间的领先者。如果您已准备好制造 pcb,则可以在 FPGA 设计完成的同一天发货。您需要做的就是将最终配置闪存到板上的 EEPROM 中,对其进行测试、封装并发货。相反,当您完成 ASIC 设计时,您会将设计运送到硅代工厂并举行流片派对。然后,您等待几个月,而代工厂会接受您的设计、检查、制造芯片、测试芯片、封装芯片,然后将封装好的 ASIC 寄回给您。当您收到完成的 ASIC 盒时,您可以构建和测试您的电路板。同时,来自竞争对手的类似产品,但基于 FPGA,在您等待从代工厂取回 ASIC 的那几个月里,将一直在您的市场上销售。如果上市时间对您来说至关重要,那么 FPGA 可能是您的最佳选择。

速度:假设您的设计人员知道他们在做什么,ASIC 从任何给定的 IC 工艺节点中提取最高性能。由于 FPGA 的大型(电容式)可编程路由矩阵,相对于 ASIC 的性能,任何给定的 IC 工艺节点的性能都会损失大约一个数量级。

能量消耗:这并不明显,但 FPGA 在单位成本和速度方面的硅效率低下也增加了 FPGA 相对于 ASIC 的功耗。FPGA 上的所有这些额外的路由矩阵晶体管都会泄漏,从而导致更高的静态功耗。由于有序 FPGA 中所需的曼哈顿布线,FPGA 中固有的较长布线会为每条布线增加电容,从而导致更高的动态功耗。但是,FPGA 供应商可以反击其 FPGA 中的额外功耗。

例如,莱迪思半导体为其 Nexus FPGA 选择了 28nm FDSOI 工艺技术,以降低静态功耗。有很多这样的设计技巧可以降低功耗,但是 FPGA 有大芯片,大芯片有很多电容,

现场更新:这是一个容易理解的。基于 SRAM 的 FPGA 很容易在现场重新编程。更改存储在闪存中的配置并更新您的设计。在 FPGA 设计的早期,您必须从其 IC 插座中拔出旧配置的 EPROM 或 EEPROM,然后插入一个新配置来执行现场更新。如今,您很可能通过 USB 或 JTAG 端口进行可重编程设计。一些最终产品设计允许无线更新,尽管允许无线硬件更新存在许多安全问题。

相反,更新 ASIC 通常需要换板(在无线行业中称为上门服务)。一些 ASIC 设计结合了来自 eFPGA 供应商(如 Achronix、Flex Logix、Menta 或 QuickLogic)的嵌入式 FPGA (eFPGA) 结构,以实现有限数量的现场更新而无需上门服务。如果您想采用这种方法,您甚至可以获得名为 OpenFPGA 的开源 FPGA 结构生成器和工具集。但是,如果您在 ASIC 中嵌入 FPGA 架构,那么 ASIC 就变成了 FPGA,不是吗?

密度:因为器件密度与单位成本密切相关,所以同样适用 FPGA 与 ASIC 的论点,只是增加了一点。在任何给定的工艺技术中,由于 FPGA 的路由开销和资源利用限制,您总是可以设计一个更大的设备,一个具有更多资源的 ASIC,如上所述。

设计流程:与 ASIC 不同,FPGA 的物理设计在您看到设备之前已经为您完成并由 FPGA 供应商验证,尽管有勘误表。您通常会使用一个供应商的工具链来设计 FPGA 配置,尽管一些富有的设计公司使用来自三大 EDA 供应商之一的 ASIC 级布局布线工具:Cadence、Siemens/Mentor 和 Synopsys。对于 ASIC 设计,您通常会采用混合搭配的方法,从三大 EDA 公司购买 EDA 工具,也许还从尚未被三大 EDA 公司之一吸收的新 EDA 初创公司购买一些额外的设计工具。

粒度:ASIC 的数字粒度是一个门,或者在某些情况下是一个晶体管。FPGA 必须具有更粗的粒度,大约为一个逻辑单元。否则,FPGA 的布线开销将变得完全不切实际。ASIC 和 FPGA 之间的这种粒度差异导致 FPGA 更高的单位成本和相对缺乏密度。

需要门级验证:FPGA 和 ASIC 一样需要设计级验证。但是,FPGA 在门级不是细粒度的,因此它们不需要门级验证。您将每个门都放置在 ASIC 设计中,因此您需要验证每个门。

技术升级路径:理论上,在一个 FPGA 供应商的产品线中从一个 FPGA 系列升级到下一个系列会更容易。例如,通过三个 Xilinx 7 系列器件迁移设计相对容易:Artix、Kintex 和 Virtex。然而,迁移到其他供应商的 FPGA 也意味着迁移到其他 FPGA 供应商的设计工具,这并不是特别容易,尽管它并不像某些人可能认为的那么困难。工程师们已经设法掌握了不止一个 FPGA 供应商的工具链。他们只是在进行更改时抱怨很多。ASIC 没有技术升级路径。要升级 ASIC,您需要设计、验证和制造新的 ASIC。

附加功能:在这里,我必须与上面的图表不同。尽管 FPGA 供应商长期以来一直在寻找附加功能块以添加到他们的 FPGA 中,但 FPGA 上可用的几乎任何东西都可以作为 IP 设计或购买并放置在 ASIC 上。这可能并不容易,但通常是可能的。关于 ASIC IP 的声明包括嵌入式 FPGA IP。也许该图表旨在表明更容易利用 FPGA 供应商塞进其部件中的许多其他前沿特性。例如,FPGA 供应商在过去 20 年一直引领着高速 SerDes 设计。如果您想要一个快速的 SerDes,您可能会在 FPGA 供应商的最新设备上找到最快的,尤其是 Achronix、Intel 和 Xilinx。

当然还有很多其他的设计考虑没有出现在上面的图表中。例如,在 FPGA 和 ASIC 之间有一个中间步骤——结构化 ASIC——与 ASIC 相比,它以更低的 NRE 成本提供了 ASIC 的许多(但不是全部)优势。十五年前,许多公司提供结构化 ASIC,并建议它们是下一代门阵列。由于许多商业原因,仅剩下一家商业结构化 ASIC 供应商——英特尔——它在 2018 年收购了最后一家结构化 ASIC 供应商 eASIC。

尽管触发本文的图表并不全面,但它确实为在 FPGA 和 ASIC 之间做出决定提供了一个很好的起点。到目前为止,这篇文章应该已经戳到了某人的痛处,所以请随时发表评论,让我们知道您的想法。

-

FPGA

+关注

关注

1628文章

21728浏览量

602949 -

asic

+关注

关注

34文章

1199浏览量

120428

发布评论请先 登录

相关推荐

FPGA与ASIC的区别 FPGA性能优化技巧

ASIC集成电路与FPGA的区别

FPGA和ASIC在大模型推理加速中的应用

FPGA与ASIC的优缺点比较

FPGA做深度学习能走多远?

为低功耗FPGA、处理器和ASIC实施启用LVDS链路

FPGA技术的五大优势

到底什么是ASIC和FPGA?

fpga和asic的区别

FPGA与AISC的差异

到底什么是ASIC和FPGA?

FPGA、ASIC、GPU谁是最合适的AI芯片?

如何在FPGA和ASIC之间做选择

如何在FPGA和ASIC之间做选择

评论