无论是x86、

Arm还是新秀

RISC-V,大家谈及基于这些架构的

处理器时,除了对比性能、功耗以外,不免会说到造就当下处理器差异化的另一大因素,那就是制造工艺。台积电、中芯国际、

三星还有

英特尔,随着如今几乎所有代工厂都参与到

RISC-V的制造中来,我们不妨挑几个用上了先进工艺的RISC-V处理器看看。

台积电 5 nm +HBM3 的 RISC-V 处理器

去年,SiFive旗下的OpenFive,一个用差异化IP提供定制方案的业务部门宣布正式流片了基于台积电5nm工艺的RISC-V处理器,该处理器集成的IP方案主要面向高性能计算/ AI、 网络与存储应用。

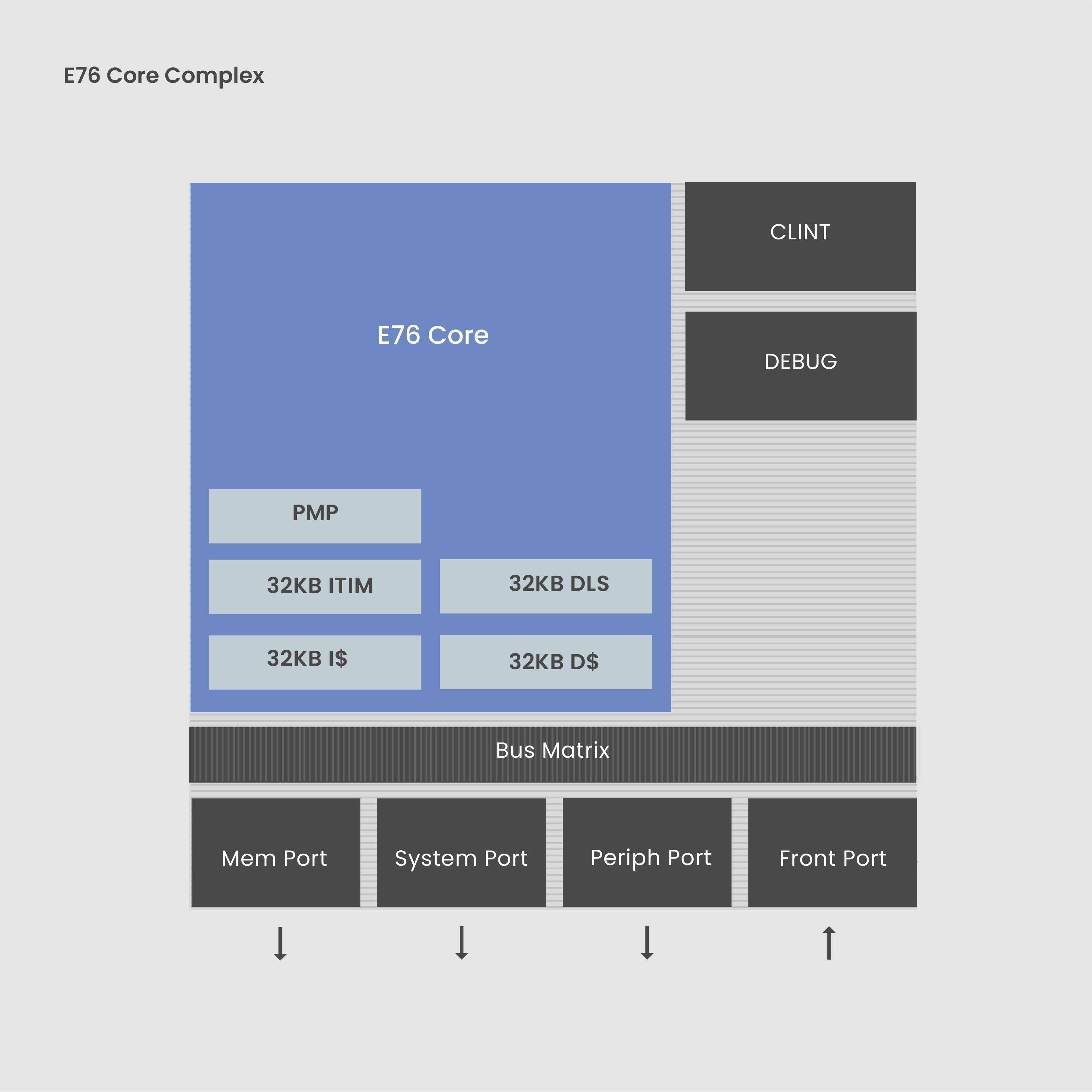

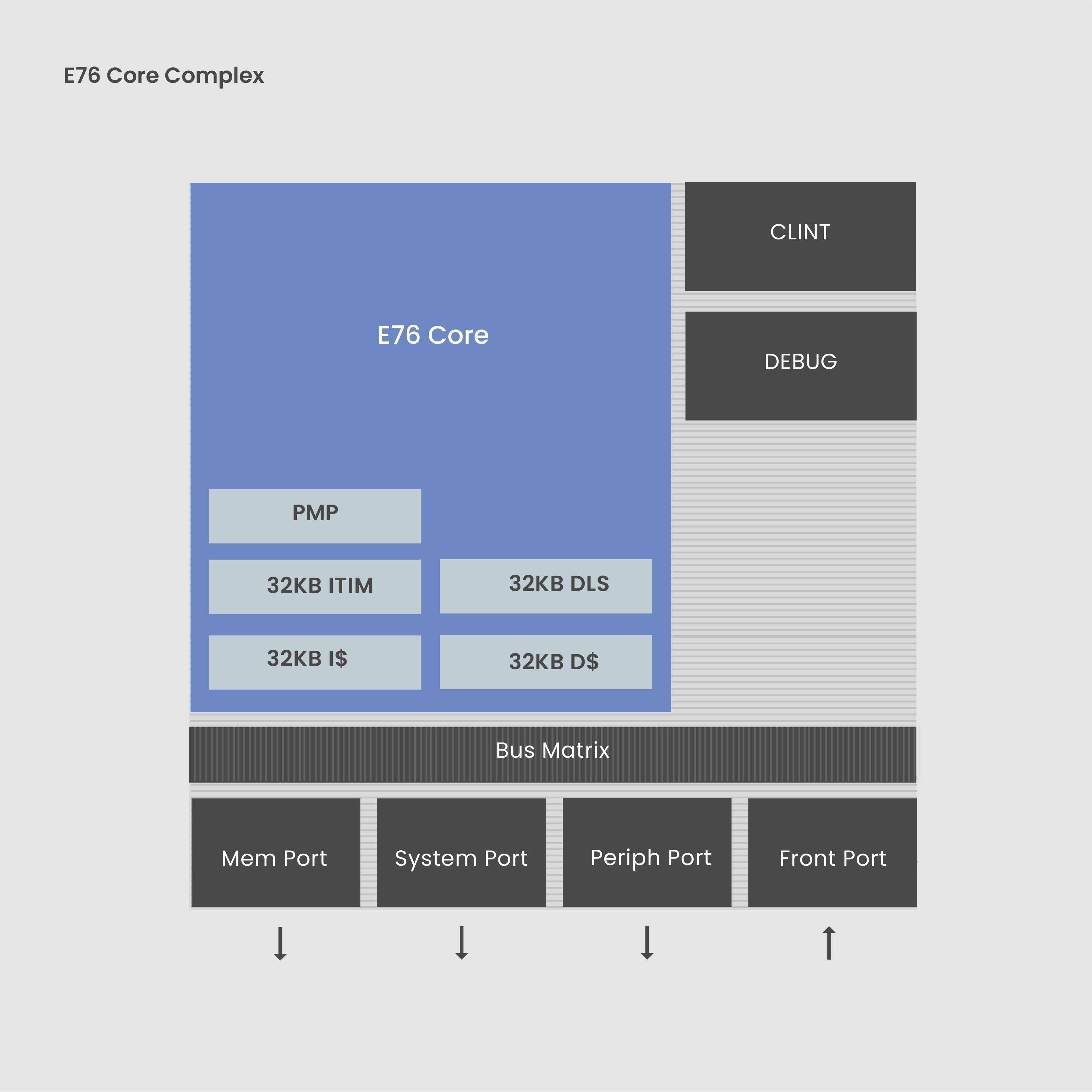

E76核心框图/ SiFive

这款SoC用到了OpenFive的HBM3 IP子系统和D2D I/O, CPU核心则选用了SiFive的E76,8级流水线的32位RISC-V核心。其HBM3 接口给到了7.2Gbps的速度,足以满足任何计算密集型应用特定领域加速器的带宽需求。在D2D 接口技术的支持下,该SoC可以通过2.5D封装实现更高的性能、更低的功耗与延迟。当然了,更重要的还是E76这个5.69CoreMark/Hz的RISC-V CPU核心。

不难看出,SiFive在高性能计算上有着自己的野心,哪怕目前Alphawave已经收购了SiFive的OpenFive业务部门。从SiFive和英特尔的关系来看,双方未来也会和继续合作,借助英特尔的IFS代 工业务,为RISC-V处理器提供更先进的制造工艺,正如下面我们要提到的这款RISC-V处理器一样。

以 I ntel 4 打造的近缓存计算 RISC-V 处理器

在我们已经看到的不少RISC-V处理器中,除了低功耗的以外,也有不少高性能的处理器,尤其是与AI/ML相关的。 深度学习激发了一批数据并行的工作负载,而传统的 SIMD处理器虽然解决了更多通用算力的问题,但其内存带宽还是无法这类应用的要求,这也是为何 GPU和一众加速器在AI/ML上更受欢迎的原因。

在今年的 VLSI22上,英特尔的研究 工程师们带来了一个新的演示分享,一个全新的8核64位RISC-V处理器,代号Vela。该 芯片完全基于Intel4的CMOS工艺打造。在这一先进工艺的助力下,这个频率为1.1 5GHz的处理器仅仅占用了1.92mm2的面积,同时集成了512kB的共享LLC,每个核心分配了64kB S RAM。最关键的是Vela应用了近缓存计算(CNC)技术,使得该处理器在深度学习负载上展现了极佳的性能。

CNC不仅实现了高带宽的访问,也实现了在大容量片上SRAM中直接进行本地计算。而Vela将虚拟寻址,连贯性和一致性一并扩张到了CNC上,实现了可允许在 Linux下的多核操作。与此同时,这个倒转 芯片封装设计的处理器与一个 FPGA相连,作为一个用于访问 DRAM和IO的芯片组。

英特尔在分享中展示了CNC LLC的数据路径、CNC ISA规范以及 编程模型,实际工作负载演示则为DNN提供了视觉化输入与输出。与将数据从LLC移动到核心内不同,CNC将成绩累加运算搬到了LLC上,就地处理数据。如此一来避免了片上网络的带宽瓶颈,同时减少全局数据的移动,增加了吞吐量提高了能效。英特尔的研究员也给出了具体提升数据,与标量处理相比,其吞吐量提升了46倍;通过减少数据移动,其整体功耗降低了11%,推理功耗降低至52分之一;在MLPe rf的异常 检测测试中,Vela将延迟降低了4.25倍,低至40μs。

不少人猜测这会不会是SiFive与英特尔打造的Ho rseCreek平台,毕竟该平台用到的也是英特尔的7nm工艺(Intel4)。不过在英特尔和SiFive双方去年的声明中,都提到了HorseCreek将使用SiFive的P550核心,一个13级流水线三发射的高性能RISC-V核心。但从其1.15GHz的频率和1.92mm2的面积来看,很可能不是,至少不会是完整的HorseCreek。

结语

其实要说现在RISC-V处理器所用的工艺,还是7nm和之前的成熟工艺居多,毕竟RISC-V现在软 硬件生态都还在高速发展中,并没有选择与Arm或x86在通用CPU和 手机SoC上硬碰硬。也许RISC-V不像Arm的公版核心一样,有那么清晰的定位,但可以预见RISC-V未来覆盖的市场很快就会与Arm重合,所用工艺的差距也将缩小,届时观察各大半导体 厂商的选择才更有趣。

台积电 5 nm +HBM3 的 RISC-V 处理器

去年,SiFive旗下的OpenFive,一个用差异化IP提供定制方案的业务部门宣布正式流片了基于台积电5nm工艺的RISC-V处理器,该处理器集成的IP方案主要面向高性能计算/ AI、 网络与存储应用。

E76核心框图/ SiFive

这款SoC用到了OpenFive的HBM3 IP子系统和D2D I/O, CPU核心则选用了SiFive的E76,8级流水线的32位RISC-V核心。其HBM3 接口给到了7.2Gbps的速度,足以满足任何计算密集型应用特定领域加速器的带宽需求。在D2D 接口技术的支持下,该SoC可以通过2.5D封装实现更高的性能、更低的功耗与延迟。当然了,更重要的还是E76这个5.69CoreMark/Hz的RISC-V CPU核心。

不难看出,SiFive在高性能计算上有着自己的野心,哪怕目前Alphawave已经收购了SiFive的OpenFive业务部门。从SiFive和英特尔的关系来看,双方未来也会和继续合作,借助英特尔的IFS代 工业务,为RISC-V处理器提供更先进的制造工艺,正如下面我们要提到的这款RISC-V处理器一样。

以 I ntel 4 打造的近缓存计算 RISC-V 处理器

在我们已经看到的不少RISC-V处理器中,除了低功耗的以外,也有不少高性能的处理器,尤其是与AI/ML相关的。 深度学习激发了一批数据并行的工作负载,而传统的 SIMD处理器虽然解决了更多通用算力的问题,但其内存带宽还是无法这类应用的要求,这也是为何 GPU和一众加速器在AI/ML上更受欢迎的原因。

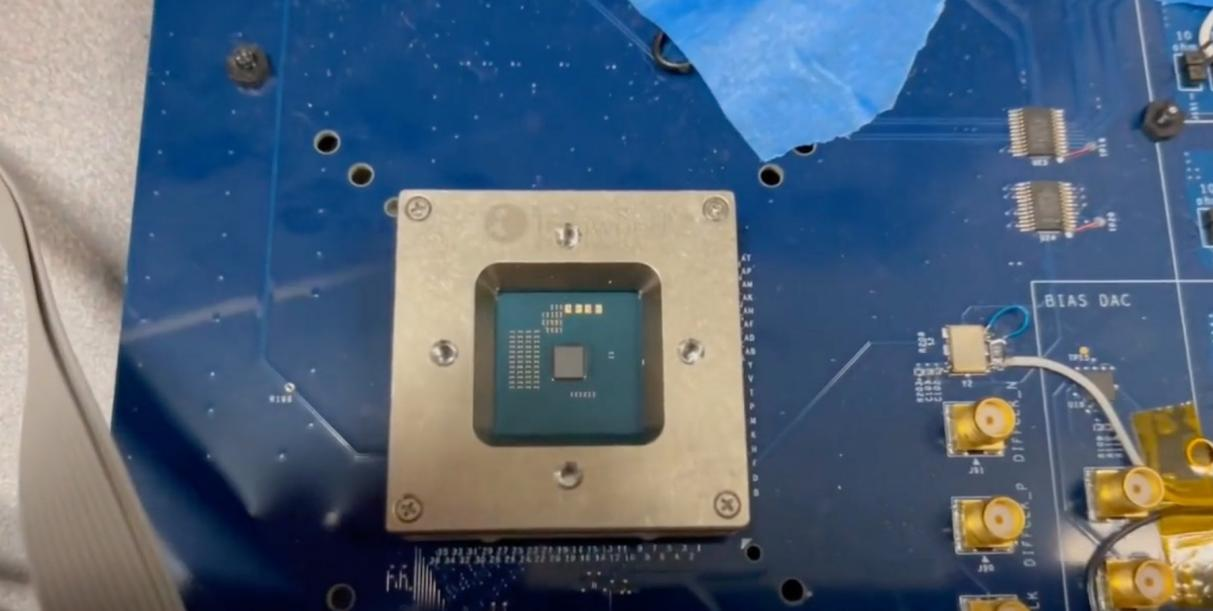

在今年的 VLSI22上,英特尔的研究 工程师们带来了一个新的演示分享,一个全新的8核64位RISC-V处理器,代号Vela。该 芯片完全基于Intel4的CMOS工艺打造。在这一先进工艺的助力下,这个频率为1.1 5GHz的处理器仅仅占用了1.92mm2的面积,同时集成了512kB的共享LLC,每个核心分配了64kB S RAM。最关键的是Vela应用了近缓存计算(CNC)技术,使得该处理器在深度学习负载上展现了极佳的性能。

CNC不仅实现了高带宽的访问,也实现了在大容量片上SRAM中直接进行本地计算。而Vela将虚拟寻址,连贯性和一致性一并扩张到了CNC上,实现了可允许在 Linux下的多核操作。与此同时,这个倒转 芯片封装设计的处理器与一个 FPGA相连,作为一个用于访问 DRAM和IO的芯片组。

英特尔在分享中展示了CNC LLC的数据路径、CNC ISA规范以及 编程模型,实际工作负载演示则为DNN提供了视觉化输入与输出。与将数据从LLC移动到核心内不同,CNC将成绩累加运算搬到了LLC上,就地处理数据。如此一来避免了片上网络的带宽瓶颈,同时减少全局数据的移动,增加了吞吐量提高了能效。英特尔的研究员也给出了具体提升数据,与标量处理相比,其吞吐量提升了46倍;通过减少数据移动,其整体功耗降低了11%,推理功耗降低至52分之一;在MLPe rf的异常 检测测试中,Vela将延迟降低了4.25倍,低至40μs。

不少人猜测这会不会是SiFive与英特尔打造的Ho rseCreek平台,毕竟该平台用到的也是英特尔的7nm工艺(Intel4)。不过在英特尔和SiFive双方去年的声明中,都提到了HorseCreek将使用SiFive的P550核心,一个13级流水线三发射的高性能RISC-V核心。但从其1.15GHz的频率和1.92mm2的面积来看,很可能不是,至少不会是完整的HorseCreek。

结语

其实要说现在RISC-V处理器所用的工艺,还是7nm和之前的成熟工艺居多,毕竟RISC-V现在软 硬件生态都还在高速发展中,并没有选择与Arm或x86在通用CPU和 手机SoC上硬碰硬。也许RISC-V不像Arm的公版核心一样,有那么清晰的定位,但可以预见RISC-V未来覆盖的市场很快就会与Arm重合,所用工艺的差距也将缩小,届时观察各大半导体 厂商的选择才更有趣。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网 网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 英特尔

+关注

关注

60文章

9694浏览量

170426 - 台积电

+关注

关注

43文章

5509浏览量

165576 - RISC-V

+关注

关注

44文章

2103浏览量

45612

发布评论请先登录

相关推荐

4nm!小米 SoC芯片曝光!

SoC芯片解决方案,据说该芯片的性能与高通骁龙8 Gen1相当,同时采用台积电

4nm“N

4P”

工艺。 爆料人士@heyitsyogesh 没有提供该定制芯片的名称,但他提到了小米内部SoC芯片的一些细节。例如,采用台积电的

消息称台积电3nm/5nm将涨价,终端产品或受影响

据业内手机晶片领域的资深人士透露,台积电计划在明年1月1日起对旗下的

先进

工艺制程进行价格调整,特别是针对3

nm和

5nm

工艺制程,而其他

请问ESP32s3 ULPRISC-V协处理器是否支持ADC的读取?

我在ULP

RISC-V协

处理器的例程中,没有发现有对ADC的操作,请问

RISC-V协

处理器目前还不支持吗?使用的IDF版本为4.4.2。 我想在ULP模式下,通过ADC来读取外部器件

发表于06-14 07:38

联发科将发布4nm工艺天玑9300+芯片

4nm

工艺打造,采用四颗超大核+四颗大核组合架构。天玑9300 Plus

处理器作为天玑9300的升级加强版,在配置和性能上均有了显著提升。采用了高性能的Cortex-X

4超大核设计,主

台积电升级4nmN4C工艺,优化能效与降低成本

在近日举办的 2024 年北美技术研讨会上,业务发展副总裁张凯文发表讲话称:“尽管我们的

5nm和

4nm

工艺尚未完全成熟,但从 N

5到 N

4

国产RISC-VMCU推荐

,CH583搭载32位青稞

RISC-V

处理器WCH

RISC-V4A,低功耗两级流水线,高性能,拥有多档系统主频,最低32KHz ,拥有特有高速的中断响应机制。 单片搞定Wi-Fi和蓝牙 许多网友也

发表于04-17 11:00

RISC-V基础学习:RISC-V基础介绍

缩写 [###] 用于标识

处理器位宽,取值[32, 64,128],也就是

处理器的寄存

器位宽 [abc...xyz] 标识该

处理器支持的指令模块集合 比如:RV64IMAC, 表示6

发表于03-12 10:25

芯来科技正式发布基于RISC-V处理器的HSM子系统解决方案

本土

RISC-VCPU IP领军企业——芯来科技正式发布基于

RISC-V

处理器的HSM子系统解决方案,提供专业有效的信息安全保护以及加解密功能。

开发出商用的RISC-V处理器还需要哪些开发工具和环境?

开发出商用的

RISC-V

处理器还需要哪些开发工具和环境?

处理器是软硬件的交汇点,所以必须有完善的编译

器、开发工具和软件开发环境(IDE),

处理器

发表于11-18 06:05

新思科技重磅发布全新RISC-V处理器系列扩大ARC IP组合

新思科技全新32位和64位ARC-

V

处理器IP建立在其数十年的

处理器开发经验之上,为设计者提供更广泛的

RISC-VIP选择空间

深入探索RISC-V处理器架构背景 思尔芯助力“香山”不断演进

近年来,基于

RISC-V架构的

处理器逐渐崭露头角,引起了业内的广泛关注。其中,由国人主导的“香山”

RISC-V

处理器备受关注。

思尔芯原型验证助力香山RISC-V处理器迭代加速

2023年10月19日,思尔芯(S2C)宣布北京开源芯片研究院(简称“开芯院”)在其历代“香山”

RISC-V

处理器开发中采用了思尔芯的芯神瞳VU19P原型验证系统,不仅加速了产品迭代,还助力多家企业

读《玄铁RISC-V处理器入门与实战》

是由美国伯克利大学的 Krest 教授及其研究团队提出的,当时提出的初衷是为了计算机/电子类方向的学生做课程实践服务的。由于这是伯克利大学研究并流片的第五代

RISC架构

处理器,因此就命名为

RISC-V

发表于09-28 11:58

4nm、5nm,那些用上先进工艺的RISC-V处理器

4nm、5nm,那些用上先进工艺的RISC-V处理器

评论