引言

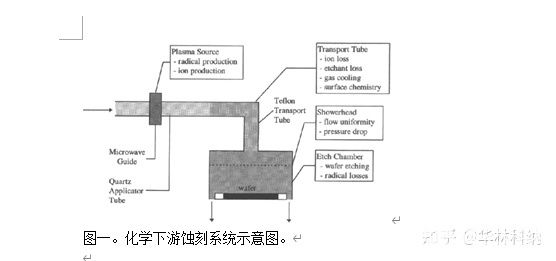

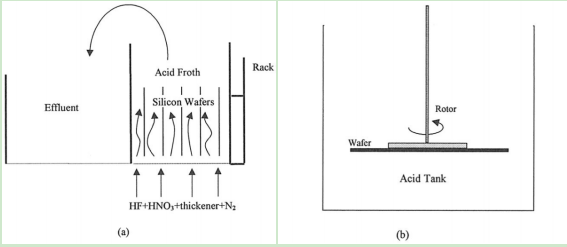

正在开发化学下游蚀刻(CDE)工具,作为用于半导体晶片处理的含水酸浴蚀刻的替代物。对CDE的要求包括在接近电中性的环境中获得高蚀刻速率的能力。高蚀刻率是由含NF”和0的混合物的等离子体放电分解产生的大量活性F原子造成的。,或参考“o”和n。因此,大浓度电中性蚀刻剂的生产提出了冲突的CDE设计要求。目前使用的设计选择是通过“传输管”将等离子体源与蚀刻室分开这种管,内衬化学惰性材料,如聚四氟乙烯,允许电荷中和,同时尽量减少中性粒子复合。

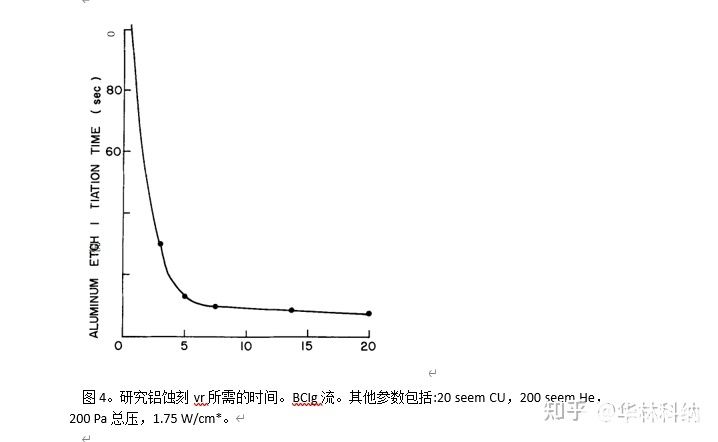

复杂的化学反应流动系统的模型最近已经发展到可以从第一原理预测CDE系统性能的程度。这项研究的目的是开发和应用一个数值模型来帮助CDE工具的设计和操作。为此,我们编制了第一个已知的NF等离子体动力学模型。,/O,气。该模型与化学反应流模型结合使用,以预测通过等离子体源、传输管、喷头和蚀刻室的条件。模型验证是通过与实验蚀刻速率数据的比较来实现的。此外,通过改变总流量、压力、等离子体功率、氧气流量和输送管直径,该模型被用于确定CDE系统的操作特性。蚀刻速率和不均匀性与各种输入和计算参数的相关性突出了系统压力、流速和原子氟浓度对系统性能的重要性。

CDE模型

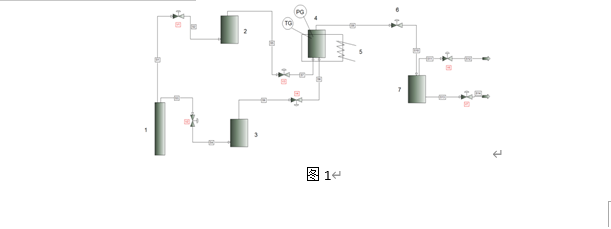

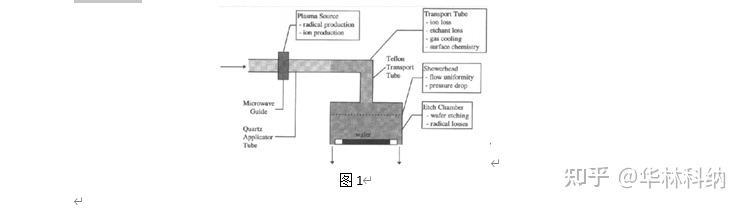

组装化学反应流模型以包括每个CDE部件(图1)中的重要化学和物理现象,即等离子体源、传输管、喷头和处理室。CDE模型从一个部件到下一个部件连续地跟随气体流动,每个部件模型的输出是下一个模型的输入。这些模型包含了每个组件中重要的物理和化学现象。一般来说,当流体从等离子体源流向处理室时,模型的化学复杂性降低(从数百个化学反应减少到四个),而物理维度增加(从等离子体源中的0D增加到蚀刻室中的2D)。CDE模型的输入是入口气体流速和温度、等离子体源功率和工艺压力,输出是晶片蚀刻速率和不均匀性以及对晶片上离子浓度的估计。中间结果包括等离子体源施加器腐蚀速率和通过输送管和处理室的气相浓度。

此处描述的CDE模型适用于矩阵集成系统公司目前正在开发的CDE工具。该系统包括一个带有石英涂敷管的微波等离子体源,能够以300至750 W输入功率,NF。,流量高达67 seem,0。高达100 sccm的流速,几十厘米长的输送管,以及能够处理200 mm晶片的蚀刻室。还分析了几种不同的淋浴头设计。考虑250至1000毫托的等离子体源压力。

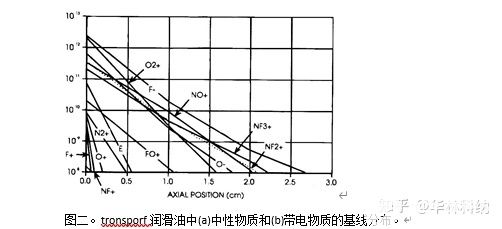

随着流动向下游进行,复合和中和反应在输送管中是重要的,并且晶片蚀刻反应在蚀刻室中是重要的。通过喷头和处理室的流动在化学上比通过等离子体源和输送管的流动简单。由于在输送管中发生了大量的中和反应,所以通过两个步骤的过程减少了反应时间。首先,带电粒子被消除。使用一维处理室模型预测蚀刻速率。系统地去除物质和反应,以给出具有几乎相同蚀刻速率的一组减少的物质和反应:在全部化学计算的3%以内。使用这种方法,描述源区域和传输管所需的大的反应组被简化为二维处理室模型可管理的组。

讨论

对各种操作条件和输送管直径进行了计算。结果分为两部分。第一个是两种操作条件和两种晶片类型的计算和测量之间的直接比较。第二项是参数研究,以确定工作条件和几何变化对CDE性能的影响。

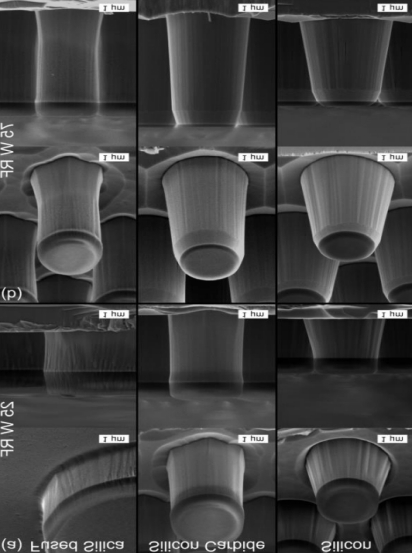

对比。—对蚀刻速率的计算和测量进行了比较,以确保CDE模型预测矩阵CDE工具的性能。对四种条件进行了计算和测量之间的直接比较:两种流动条件,每种条件具有两种不同的晶片类型。两个tlow条件是:(t)67 SCCM NF的基线情况100 sccm O,源功率320 W,蚀刻室压力335 mTorr,和(ii)67 SCCM NF的非基线情况0 sccm O,源功率320 W,蚀刻室压力250 mTorr。这两种晶片类型是覆盖多晶硅和二氧化硅晶片。蚀刻速率和不均匀性如表1所示。该模型对NF/O等离子体最为精确,在所有情况下,预测蚀刻速率在80 %以内。非均匀性的模型预测与测量结果不一致(在该比较中仅使用了一个晶片)。已经表明,改进的比较导致对更多晶片的更详细的测量。特别是,该模型已用于比较不同CDE下多晶硅蚀刻的蚀刻速率和不均匀性1,24,以及蚀刻速率和不均匀性在25 %以内的数值和趋势。

浓度在百万分之几的数量级,并且预期足够小,以至于几乎不会对晶片造成损害。由于传输管有几十厘米长,所以可以看出,按指数规律下降的离子浓度无关紧要。发现极小的离子含量是由这里给出的计算条件产生的,因此我们得出结论,传输管的设计预期消除离子的存在,同时仅轻微影响自由基浓度。

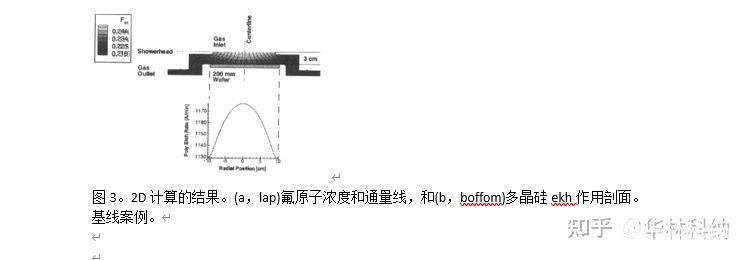

图3示出了二维蚀刻室计算的详细结果。除了晶片之外的所有表面上都发生氟原子再结合到Ft,在晶片中多晶硅被氟原子蚀刻以形成SiF。图3a显示了通过该室的氟原子浓度和氟原子通量线。在图3b中,示出了得到的多晶硅蚀刻速率曲线。如果蚀刻速率在整个晶片上是均匀的,通量线将均匀间隔地与晶片相交。通量线向晶片边缘的偏转是蚀刻室中对流和扩散的复杂相互作用的结果,导致中心快速蚀刻速率分布。

总结和结论

模型o1化学下游蚀刻已经预测了一系列操作条件下的蚀刻速率和不均匀性。预测和测量的晶片蚀刻速率之间的直接比较显示,对于一组基线操作条件,模型的精度在10%以内,对于非基线条件,模型的精度在30%以内。进行流速、源混合物的组成、压力、等离子体源功率和输送管直径的系统变化,并得到相关的蚀刻速率。蚀刻室和等离子体源压力O和NF、流速充分预测了计算的多晶和氧化物蚀刻速率和7%以内的均匀性。通过关联蚀刻室压力、蚀刻室入口流速和蚀刻室入口原子氟摩尔分数,实现了更好的关联,这依赖于更少的独立变量并实现了更低的rms误差(在1%以内)。

这项研究的结论是:

第一原理化学反应流动模型可用于预测NF/O化学下游蚀刻系统中多晶硅和二氧化硅水的蚀刻速率和均匀性。

蚀刻速率和不均匀性可以与操作参数相关联,这在工艺设计中应该证明是有用的。

使用蚀刻室条件获得了蚀刻速率和不均匀性的良好相关性。这应该允许基于组合的等离子体源、传输管和喷头部件的输出来预测CDE性能。

多晶硅蚀刻往往受对流限制,因此蚀刻速率取决于压力、质量流量和蚀刻剂摩尔分数,而氧化物蚀刻受表面反应速率限制,因此比多晶硅蚀刻更多地取决于压力,而更少地取决于流量。

在较低压力和较高流速下,蚀刻均匀性得到改善。

晶片上的离子浓度估计小于10'/cm ',以F*为主。

审核编辑:符乾江

-

半导体

+关注

关注

334文章

27286浏览量

218067 -

蚀刻

+关注

关注

9文章

413浏览量

15368

发布评论请先 登录

相关推荐

晶片边缘蚀刻机及其蚀刻方法

PCB印制电路中蚀刻液的选择

用于蚀刻冲洗和干燥MEMS晶片的最佳工艺条件实验报告

硅碱性蚀刻中的绝对蚀刻速率

二氧化硅薄膜蚀刻速率均匀性的比较

单晶硅片碱性溶液中的蚀刻速率

微细加工湿法蚀刻中不同蚀刻方法

操作参数对蚀刻速率和均匀性的影响

硅晶片的蚀刻预处理方法包括哪些

蚀刻速率的影响因素及解决方法

硅晶片的酸基蚀刻:传质和动力学效应

载体晶圆对蚀刻速率、选择性、形貌的影响

蚀刻系统操作条件对晶片蚀刻速率和均匀性的影响

蚀刻系统操作条件对晶片蚀刻速率和均匀性的影响

评论