工程师熟悉电磁干扰、并联和布局,但在从硅基芯片过渡到碳化硅或宽带隙器件时,需要多加注意。

据chip称,硅(Si)基半导体比宽带隙(WBG)半导体领先十年,主要是碳化硅(SiC)和氮化镓(GaN)仍占有约90%至98%的市场份额。供应商。尽管远非成熟的技术,WBG 半导体正在跨行业进军,这要归功于它们相对于硅的性能优势,包括更高的效率、更高的功率密度、更小的尺寸和更少的冷却。

使用基于 SiC 或 GaN 的功率半导体获得最佳设计需要更多的专业知识和在多个领域的仔细考虑,包括开关拓扑、电磁干扰 (EMI)、布局、并联和栅极驱动器的选择。

解决可靠性和成本问题也很重要。

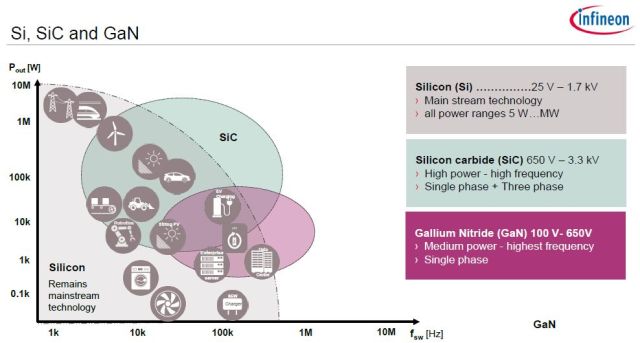

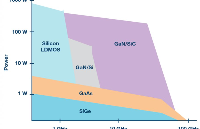

在可以使用 Si、SiC 和 GaN 的重叠应用中,选择归结为密度、效率和成本,一旦设计人员了解这三个参数,就会指导他们使用哪种开关技术。(图片:英飞凌科技)

为什么要搬到WBG?

这一切都始于根据设计目标决定从基于硅的功率器件转向基于碳化硅或氮化镓的功率器件。

Infineon Technologies AG 功率分立器件技术营销工程师 Bob Yee 表示,无论是使用硅还是改用 SiC 或 GaN,设计人员都必须检查成本、效率和密度这三个因素。据记载,英飞凌凭借 CoolSiC 和 CoolGaN 产品组合同时涉足 SiC 和 GaN 市场,还提供 Si MOSFETS 和 IGBT。

Yee 说,成本以每瓦特美元、功率输入/输出百分比的效率以及每立方英寸瓦特的密度来衡量。“一旦你确定了这些目标,这将决定技术的类型以及成本点在哪里。”

Yee 引用了一个小尺寸适配器设计的例子说,尺寸和重量对于理解你是使用硅还是 WBG 很重要,它可能会在 Si MOSFET 上使用 GaN 晶体管 (HEMT)。原因?GaN 的更高开关频率允许设计人员缩小磁性元件的尺寸,这在电源尺寸中占很大一部分。

“设计人员必须了解他们的密度需求是什么,这最终将决定效率,因为小尺寸的散热空间更小,”他补充道。“这意味着效率需要更高,促使设计人员使用 WBG。”

神奇的线

几十年来,基于硅的解决方案实现了更高的效率和更小的尺寸,但 WBG 半导体在某一点上提供了更好的效率。Yee 举了一个 100 W 电源的例子——100 W 输入和 94 W 输出,这意味着 6% 的损耗或 94% 的效率。“这是从硅分离到使用 WBG 技术的神奇线,”他说。“如果工程师的设计高达 94%,那么它就被硅覆盖了,没有理由去 WBG 支付更多费用。但是,如果您试图实现 96% 的效率,则除了使用 WBG 之外别无选择,这归结为除了拓扑之外,开关本身属性的寄生损耗。

“如果您想实现 96% 的效率,您需要一种利用 GaN 或 SiC 的新拓扑,”Yee 补充道。

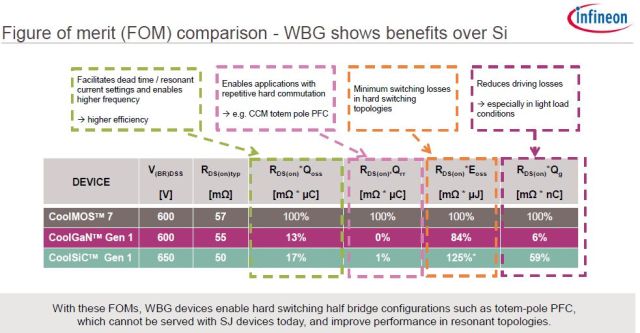

一个很好的例子是使用功率因数校正 (PFC) 拓扑。Yee 说,如果设计人员着眼于如何针对特定拓扑优化开关技术——例如,利用 WBG 的图腾柱 PFC——它会提高性能,“这就是为什么无桥图腾柱 PFC 真的是一个扣篮为世界银行集团。”

设计人员需要通过查看开关技术如何针对特定拓扑进行优化以实现最大的性能改进来评估 WBG 器件。(图片:英飞凌科技)

挑战

设计人员可以优化他们的设计以获得更高的频率、更高的功率密度和更高的效率。这就是一些 WBG 技术挑战出现的地方。当以更高频率进行开关时,设计人员需要注意 EMI 和更高的开关损耗。

WBG 的寄生效应小于硅等效物,这意味着 EMI 很容易升高,因为它是一种更快的开关。Yee 说,当您针对高频进行优化时,您需要注意 EMI,并且需要考虑额外的开关损耗。

SiC FET、SiC JFET 和 SiC 肖特基二极管制造商 UnitedSiC 工程副总裁 (VP) Anup Bhalla 表示同意。“EMI 问题会变得更加严重,尤其是当您试图获得更高功率密度的系统优势时,这实际上意味着一切都变得更小,而变得更小的唯一方法就是您的开关速度要快得多。这使您可以将变压器、电感器、散热器和其他东西做得更小。”

Bhalla 说,更快的开关也意味着您正在以高电压和电流变化率运行,这可能导致大的电压过冲和 EMI 问题,因此布局变得更具挑战性。

“电路电源端的这些快速电压变化很容易影响电路的信号端,因为它可以在你不知情的情况下在这里或那里发送一点电压尖峰,”他说。“它可能会在错误的时间触发栅极驱动器并炸毁所有东西,因此您必须在布局上更加小心。通常需要[客户]付出相当大的工程努力才能达到目标,而且他们中的很多人在过去的四五年里已经实现了这一飞跃。”

优化布局

布局可能是一个挑战;Yee说,最大的障碍是在司机和大门之间。“设计师需要注意三个终端。它是驱动器输出到栅极输入,无论是 iw56\s SiC 还是 GaN,以及驱动器源极到 WBG 器件源极的接地连接。”

Yee 说,他们需要最小化的第一件事是环路电感,因为 WBG 部件的开关速度要快得多。“如果他们不注意这一点,他们就会制造出会发出辐射的收音机。” 因此需要特别注意这些连接。为了缓解这一挑战,英飞凌建议使用具有开尔文源功能的 WBG 器件。

布局也会影响更高功率应用的并联。Bhalla 说,平行是相当简单的。“这是相同的一般物理学——你必须保持布局对称和平衡。我们必须保持零件之间的参数分布相对紧密,这样所有零件看起来都差不多,这样它们就很容易平行。

“设计人员喜欢采用这些快速部件并将它们并联起来,就像过去并联 IGBT 一样,”他补充道。“这很难,因为 IGBT 的速度要慢得多,因此它们更容易并联。当您尝试并行并同时将切换速度提高 10 倍时,您必须在布局方面做更多的工作。

“你必须小心,至少要做好一半的布局,这样并行设备之间的所有电流路径看起来都差不多。你不能让一个设备的电感只有另一个的五分之一,然后期望它们并联;这是行不通的。”

Bhalla 说,有时向工程师展示如何解决布局和并联方面的挑战的最简单方法是给他们一个演示板。“我们非常小心地确保当您并行使用这些设备时,用于驱动栅极的环路必须与路由所有功率/电流的环路保持分离。栅极驱动电路是一个小回路,然后有一个强大的大回路驱动所有的功率/电流,您希望最大限度地减少这两者之间的耦合。如果你这样做,你就会知道并行变得更好、更容易。”

使用 GaN 器件时也是如此。“工程师必须比过去更好地理解布局,因为 GAN 速度很快,”GaN Systems 销售和营销副总裁 (VP)、GaN HEMT/E-HEMT 设备专家 Larry Spaziani 说。“如果您没有正确的布局,那么您可能会遇到性能或 EMI 甚至故障模式的问题。

“GaN 不会改变布局规则,但一切都更小、更紧密、更紧凑,所以你必须确保你做得对,”他补充道。

碳化硅的小调整

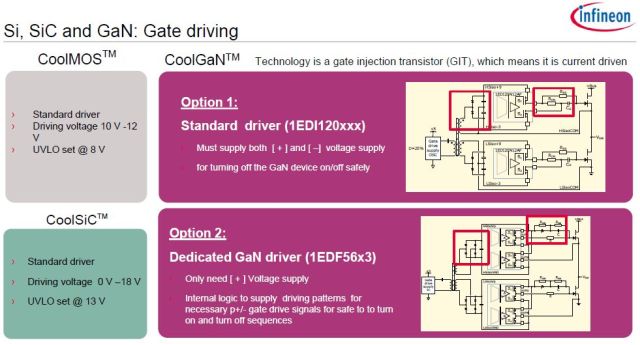

Yee 解释说,SiC 可以用作 Si IGBT 或 Si MOSFET 的性能替代品,部分原因是驱动结构非常相似——它是一个常关部件并使用标准驱动器,但存在细微差别。

使用 Si MOSFET,驱动电压为 10 V 至 12 V;但是,如果您使用 SiC,则为 0 V 至 18 V,并且欠压锁定 (UVLO) 从 Si 的 8 V 变为 SiC 的 13 V,因此设计人员在移动时需要做一些细微的调整Yee 解释说,从 Si 到 SiC。

但是,对于GaN,驱动结构完全不同;他补充说,它与 IGBT 或 MOSFET 不同。“您必须使用具有特定开启和关闭时间的特定驱动程序。因此,设计人员确实需要注意驱动方案,不仅要注意时序,而且如果要并行 GaN FET,则必须在驱动器和 GaN FET 之间具有完美的对称布局。”

需要注意的是,设计人员可以使用 GaN 的标准驱动器,只要它支持栅极驱动电压和 UVLO,但同样需要对设计进行调整。大多数供应商建议使用更新一代的栅极驱动器,以通过能够以最快的开关速度进行开关来获得最高性能。

与专用 GaN 驱动器相比,使用标准栅极驱动器驱动 GaN 器件需要添加负电压电源以安全地开启和关闭器件。(图片:英飞凌科技)

“如果您使用标准驱动器,则只有 GaN 才需要提供正电压和负电压,这就是我们更喜欢客户使用专用驱动器的原因,”Yee 说。他推荐英飞凌的 1EDF56x3 系列 GaN 栅极驱动器。

并非所有 SiC 器件都生而平等

大多数 WBG 器件不是 Si MOSFET 或 Si 晶体管的直接替代品。需要很少或不需要额外工程工作的共源共栅型设备除外。然而,设计人员失去了 WBG 半导体的一些优势。

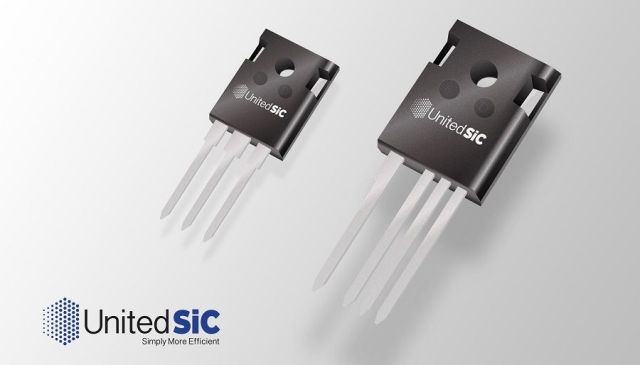

一个例子是 UnitedSiC 的 SiC 产品,它们都采用与硅兼容的封装。这意味着这些设备可以直接将它们放入以前使用 IGBT 或 Si 超结 MOSFET 的插座中。

Bhalla 表示,其产品的独特之处之一是它制造的基于共源共栅的设备,其工作方式类似于 MOSFET。这些 SiC FET 包括与共源共栅优化的 Si MOSFET 共同封装的 SiC 快速 JET,以提供采用标准通孔和表面贴装封装的标准栅极驱动 SiC 器件。“我们的共源共栅型器件是一个字面意义上的插入式器件,除了可能的栅极电阻变化之外没有任何变化,”他说。

此外,这些设备不需要特殊的驱动程序;Bhalla 表示,它们与市场上所有主要供应商提供的标准硅栅极驱动器 IC 兼容十年,包括与 SiC MOSFET 和“老派”IGBT 一起使用的旧款。

他补充说,在过去两年中,已经专门为 SiC 开发了许多优秀的栅极驱动器。“它们更贵,但人们已经开始使用它们,我们的设备也与那些更好的驱动程序兼容。”

但也有一些缺点,包括不能从 WBG 设备中获得最高性能。Bhalla 说:“我们正在销售采用这些封装的超高速器件,这些封装具有很大的电感。” “当你通过这些封装在电路中放置高压摆率 (di/dt) 时,它只会加剧快速开关的所有问题——更大的过冲、更多的振荡等。”

Bhalla 说,向更好的包装过渡是一项正在进行的工作。“这就是现实:人们在使用 SiC 的部分好处的同时,仍然从他们的终端系统中获得一些好处,这种方法既便宜又脏。

“世界上很大一部分仍然是硅,所以对于他们从硅转向碳化硅,我们提供了一个非常好的垫脚石,”他说。

Bhalla 认为,到明年,将会有很多顶部冷却的表面贴装封装,甚至是将整个半桥集成到一个封装中的表面贴装型模块。“必须这样做,因为没有它,用户就无法从中获得所有好处,也无法进入下一个层次,”他说。

例如,UnitedSiC 最近推出了一款采用 TO-247 封装的7mΩ R DS(ON)、650V器件。(低 R DS(ON)可以实现更高的效率。)该公司最接近的竞争对手的导通电阻高出 3 倍,但 UnitedSiC 遇到的一个问题是封装引线实际上比芯片更热。“所以我们采用了一个 200-A 的设备并将其降额到 120A,因为当我们在实践中使用这个设备时,我们看到引线变得比芯片本身更热,”Bhalla 说。

UnitedSiC通过在熟悉的 TO-247 封装中结合第三代 SiC JFET 和共源共栅优化的 Si MOSFET,推出了第一款 SiC FET,R DS(on) <10 mΩ,提高了效率并降低了损耗在与 Si IGBT 相同的栅极电压下。(图片:UnitedSiC)

氮化镓的好处

从消费电子产品到汽车等各个领域的 OEM 设计师都有几个共同的设计要求:他们想要更高的功率密度和更小的电子产品。

Spaziani 说,在更高的频率下,电源系统中的几乎所有组件(电容器、电感器、变压器等)都可以更小,而且由于 GaN 非常高效且产生的热量非常少,因此不需要任何散热器,因此设计人员只需移除散热器即可节省空间和成本。或者它们可能保持相同的频率以实现更高的效率。通常,即使效率提高 1%,也足以让服务器电源领域的客户从铂金级升级到钛级 [96% 的效率],他说。

Spaziani 说,这与工程师通常所做的没有什么不同。无论是使用硅还是其他技术,他们通常都必须优化他们的电路板,但在栅极驱动方面存在差异。对于 GaN 和 SiC,栅极驱动行为不同于硅 MOSFET 和硅 IGBT,因此工程师必须问的第一件事是:“我如何驱动栅极?”

过去30年,MOSFETS基本变成了0-12-V的栅极驱动电路,而GaN要么是–3-6V,要么是0-10V,要么是0-5V;他们都有点不同,Spaziani 说。“但好消息是 GaN Systems 现在已经走过了 6 年的历程,我们有大约 12 家主要的半导体公司已经创建了驱动 GaN 的驱动器,所以现在,这只是一个简单的应用决策。”

GaN Systems 还提供称为 EZDrive 的电路,无需分立驱动器。它将 12V MOSFET 驱动器转换为具有大约六个组件的 6V GaN 驱动器。“它真的很便宜,而且适配器设计者喜欢这个电路,”Spaziani 说。“它易于使用、不耗电、体积小,而且无需定制栅极驱动器。”

揭穿 GaN 神话

GaN 供应商认为,关于 GaN 技术仍然存在一些错误或半真半假的神话。问题包括 EMI、并联、雪崩能力、可靠性和成本。

GaN 器件的 EMI 更糟。GaN 提供出色的开关边缘,可实现更高的效率和更高的频率,但这并不意味着 EMI 更糟。事实上,供应商表示它通常比具有良好布局的硅更好,并且可以产生更小的 EMI 滤波器,从而降低成本。

并行是一个常见的问题。一种误解是 GaN 只擅长低功率和高频率。例如,GaN Systems 的客户以 20 kHz 至 20 MHz 的频率进行切换,并且在高功率下,它们是并联设备。GaN晶体管可以很好地并联;只需确保每个晶体管承载的电流量大致相同。例如,如果您将两个设备并联,并且一个晶体管承载 70% 的电流,则它会磨损得更快,电路也会更快地发生故障。警告:来自不同 SiC 和 GaN 供应商的设备的并行方式略有不同。

没有雪崩能力。MOSFET 进入雪崩模式以抑制电压尖峰以保护电路的其余部分免于故障。GaN 器件制造商解决这个问题的方法是在额定电压中设计大量余量。例如,GaN Systems 的 650V 额定设备在电压远远超过 1,000V 时才会出现故障。

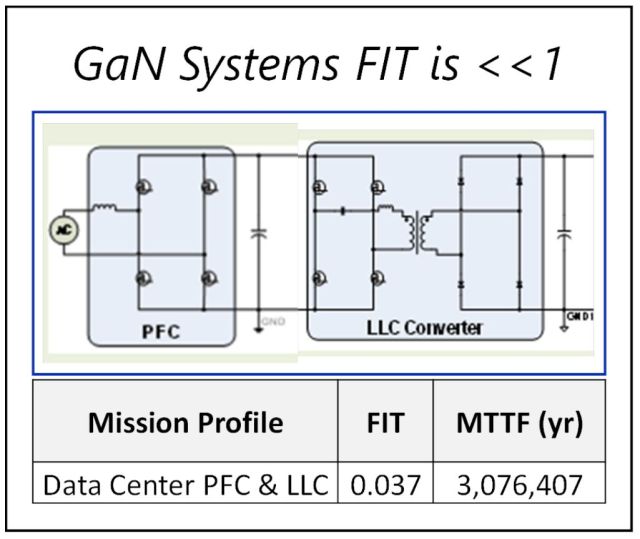

可靠性和成本不等于硅。可靠性是通过及时故障 (FIT) 来衡量的。硅已经存在了几十年,并且已被大多数供应商证明是可靠的。但 WBG 半导体并非如此。与任何新技术一样,可靠性风险增加且成本更高。WBG 器件和硅器件之间的比较很难,因为硅芯片的可靠性有据可查,而且多年来的大批量生产降低了成本。

但一些 WBG 供应商,如 GaN Systems,表示可靠性 [FIT] 与硅相当,价格差距在过去五年中显着缩小,从贵 3 倍到 5 倍下降到 1.5 倍到 2 倍。

GaN Systems 的器件显示 FIT 率 <0.1。(图片:GaN Systems)

审核编辑 黄昊宇

-

半导体

+关注

关注

334文章

27286浏览量

218023 -

设计

+关注

关注

4文章

818浏览量

69887 -

SiC

+关注

关注

29文章

2804浏览量

62601 -

GaN

+关注

关注

19文章

1933浏览量

73278

发布评论请先 登录

相关推荐

中国半导体的镜鉴之路

WBG 器件给栅极驱动器电源带来的挑战

Nexperia斥资2亿美元加速汉堡工厂宽带隙(WBG)半导体研发与生产

ATA-5420前置微小信号放大器如何进行半导体测试

安世半导体Nexperia将在汉堡投资2亿美元研发下一代宽禁带半导体产品(WBG)

宽带隙(WBG)半导体助力可持续电动汽车电源转换,顶部冷却(TSC)技术提升热性能

瑞萨电子收购Transphorm,加速GaN功率半导体市场布局

半导体IC设计是什么?IC设计和芯片设计区别

使用 WBG 半导体进行设计需要更多的奉献精神

使用 WBG 半导体进行设计需要更多的奉献精神

评论