Verilog代码编写完成后,可以Modelsim中进行编译。

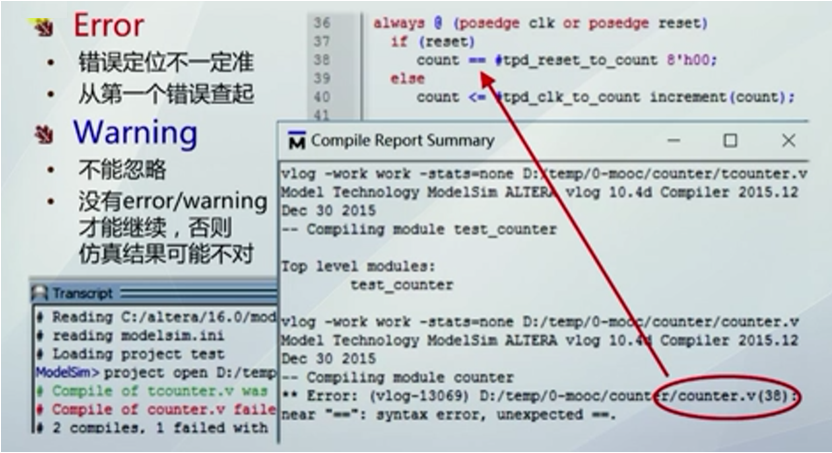

与其他编程软件相同,错误(error)的定位不一定准确,错误的发生位置可能与编译时提示的错误位置不同;检查error时,要从第一行开始检查,可能位置靠前的错误更正后,位置靠后的错误同时被更正。

与其他编程软件不同,警告(Warning)不能忽略,只有error/warning都消除才能进行仿真。否则,仿真结果可能不正确,可能导致真实芯片出现问题,造成百万元到千万元人民币的损失。

图片来源:学堂在线《IC设计与方法》

正确编译完成后,可以进行仿真。

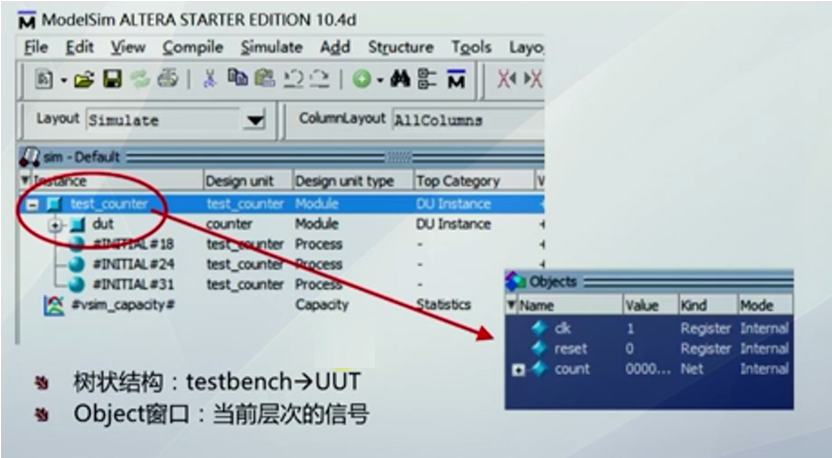

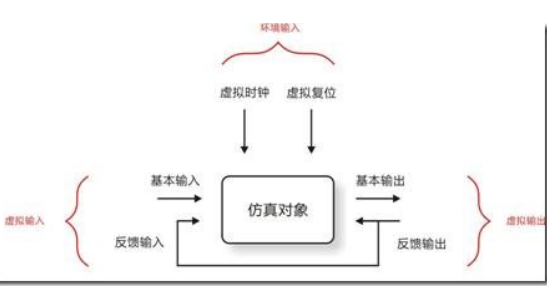

Modelsim仿真将设计以树状表示,设计中的每一个实体,每一个module、每一个进程(always块、initial块等)在Modelsim仿真中以对象的形式展现。

如下图所示树状结构,顶层是test_counter,即测试平台。平台下方是DUT(被测设计)和三个进程。三个进程是三个initial块,分别用来产生时钟信号、复位信号、其他动作。

图片来源:学堂在线《IC设计与方法》

上图右下角为Object窗口,显示当前有哪些信号可以观测,包括输入信号、输出信号、内部信号等,如在test_counter层次,可以观测时钟(clk)、复位(reset)、计数器(count)的信号。

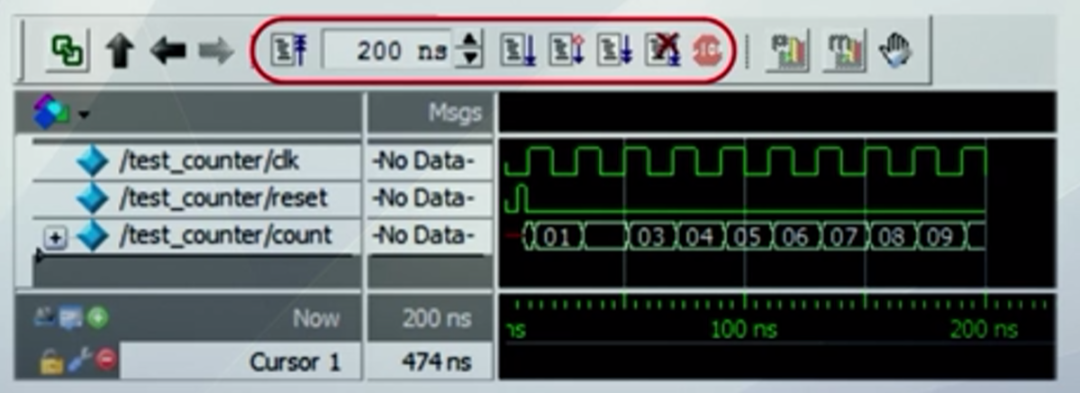

仿真过程有四类控制操作需要掌握。Restart、仿真时间指定、持续仿真、强制停止。

Restart主要运用于修改源代码或需要改变波形窗口显示时间的情况,在做出相应的修改后,运用Restart控制仿真重新开始。

仿真时间指定、持续仿真、强制停止主要用于永远执行的程序,永远执行的程序会造成CPU资源的浪费,也会使波形窗口显示时间过长,波形窗口显示时间过长可能会导致观测人员无法观测需要的波形。因此需要上述三类操作控制仿真时间。

图片来源:学堂在线《IC设计与方法》

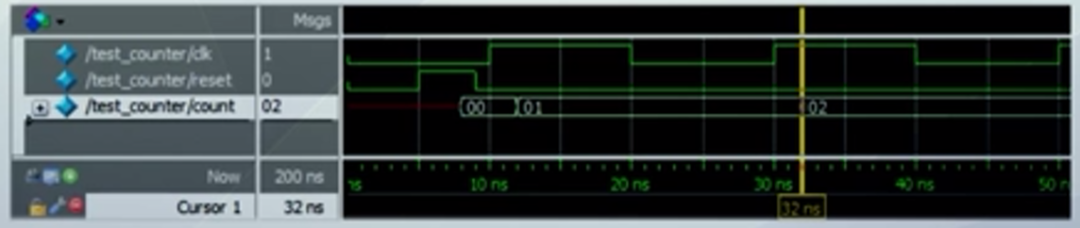

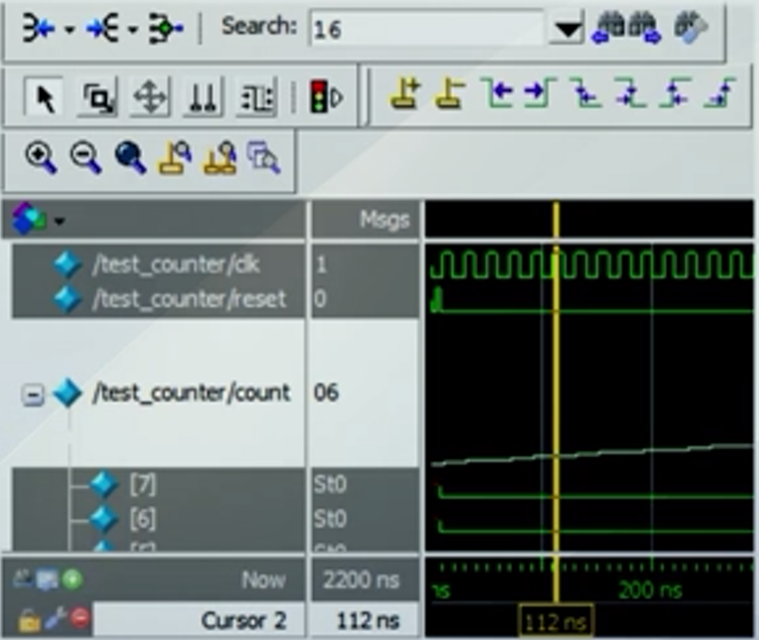

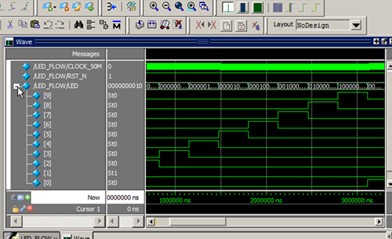

仿真工具执行仿真结束后,设计人员需要检查电路运行结果是否正确。最常见的方式是通过波形窗口观测电路输出信号的波形是否正确。主要观测的信号包括输入信号、内部信号、输出信号。

检测输入信号的目的是排除输入不正确造成输出不正确的情况,需观测输入信号包括时钟信号、复位信号、数据信号。设计人员需观测时钟信号的周期或频率、0时刻时钟信号的值、时钟信号高电平和低电平的值,需观测复位信号的有效脉冲(个人理解:能够导致输入信号变化的脉冲)是否符合期望、并确定复位信号的时钟沿(个人理解:脉冲发生的时间)不能与时钟信号重叠,需确定数据信号的时钟沿不能与时钟信号重叠。

观测电路的内部信号包括状态机(能够控制电路内部状态转移)、控制信号。

图片来源:学堂在线《IC设计与方法》

当出现无法观测波形情况时,可以通过波形窗口调整。波形窗口调整方式包括总线展开和收缩、改变数据显示方式、波形放大和缩小、光标操作、定位信号的事件、搜索特定信号值、增加驱动信号等。

图片来源:学堂在线《IC设计与方法》

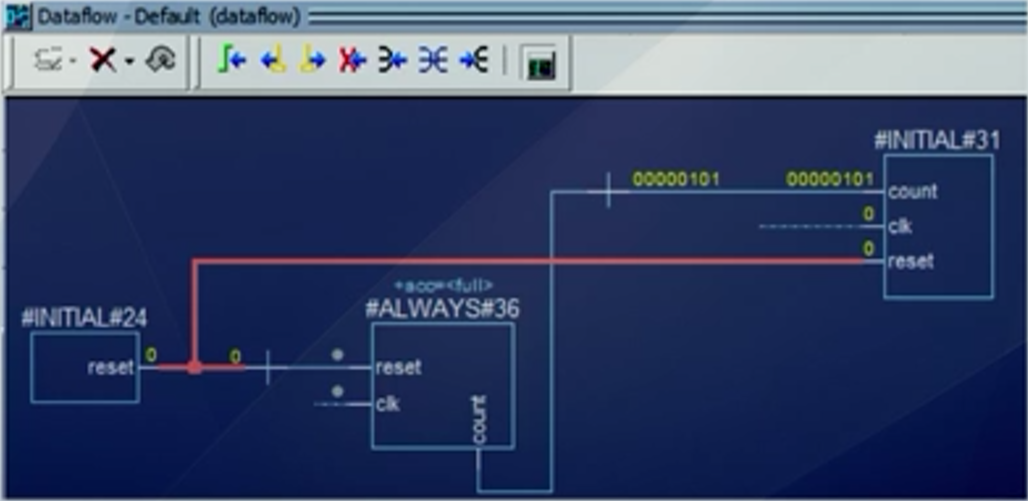

有时通过波形不容易寻找出芯片设计的问题,需要更高层次的方式,如数据流窗口调试,追踪信号来源。在数据流窗口中可以显示出设计的层次图,选择某一信号,仿真工具就将显示产生这一信号的数据流图(Dataflow),数据流图可以分析某一信号故障的根源。

图片来源:学堂在线《IC设计与方法》

数据流图、波形窗口、源代码可进行交叉定位,同时分析某一进程(如always块)的输入(数据流图观测)和行为(源代码观测),确定故障(波形窗口观测)源于其输入还是源于其行为,可以快速找出电路故障。

审核编辑 :李倩

-

ModelSim

+关注

关注

5文章

174浏览量

47162 -

编程软件

+关注

关注

3文章

143浏览量

23503 -

时钟信号

+关注

关注

4文章

448浏览量

28542

原文标题:芯片设计相关介绍(22)——Modelsim仿真工具

文章出处:【微信号:行业学习与研究,微信公众号:行业学习与研究】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Modelsim FLI接口的协同仿真技术

使用ModelSim进行设计仿真

使用 ModelSim 进行设计仿真

Altera ModelSim 6.5仿真入门教程

使用 ModelSim 进行设计仿真详解

modelsim仿真详细过程(功能仿真与时序仿真)

仿真软件ModelSim及其应用,ModelSim的仿真流程

Modelsim仿真教程Modelsim的基础入门基础教程免费下载

基于ModelSim使用二联合Quarus自动仿真教程

芯片设计之Modelsim仿真工具

芯片设计之Modelsim仿真工具

评论