本文主要来源为学堂在线《IC设计与方法》学习笔记

Quarus Ⅱ工具的整体编译过程包括逻辑综合、布局布线、时序分析、I/O分析(个人理解芯片引脚的分析)等编译子过程。

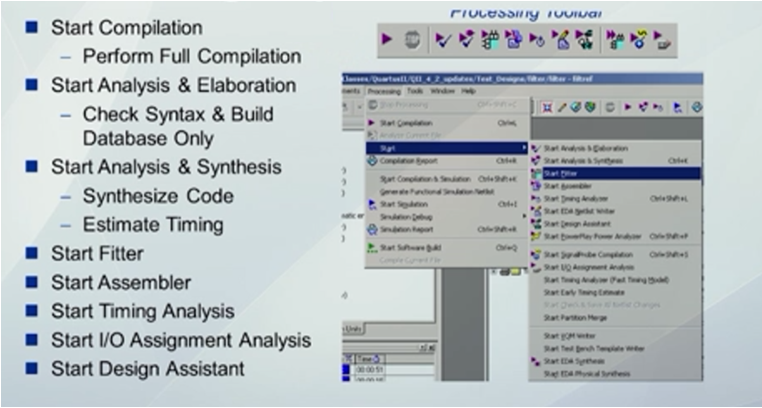

Quarus Ⅱ工具提供了如图一右上角的工具条,设计人员可以直接点击工具条第一个紫色的三角形按钮完成整体编译过程,也可通过点击其他带有紫色三角形的按钮完成某一子过程的编译。

对于简单的芯片设计,设计人员可以点击一个按钮完成整体编译过程。对于复杂的芯片设计,逻辑综合、布局布线、时序分析子过程可能需要花费数小时到数天的时间。如果每次编译都进行整体编译,会浪费时间,所以复杂的芯片设计通常分步完成每个子过程的编译。

图一,图片来源:学堂在线《IC设计与方法》

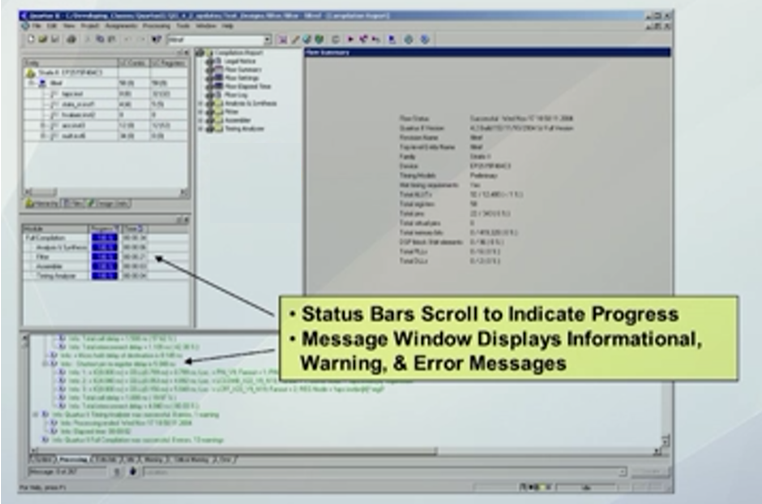

设计人员需要关注Quarus Ⅱ工具提供的报告。

图二左侧中间带有多个蓝色进度条的窗口会报告编译过程是否百分之百正确,如果编译有错误,Quarus Ⅱ工具可能会在错误处停滞。

图二最靠下写有绿色文字的窗口会报告编译过程的一些相关信息,设计人员需要仔细检查是否有error或warning,除非可以确认warning对芯片设计没有影响,否则设计人员需要排除所有的error或warning。

图二,图片来源:学堂在线《IC设计与方法》

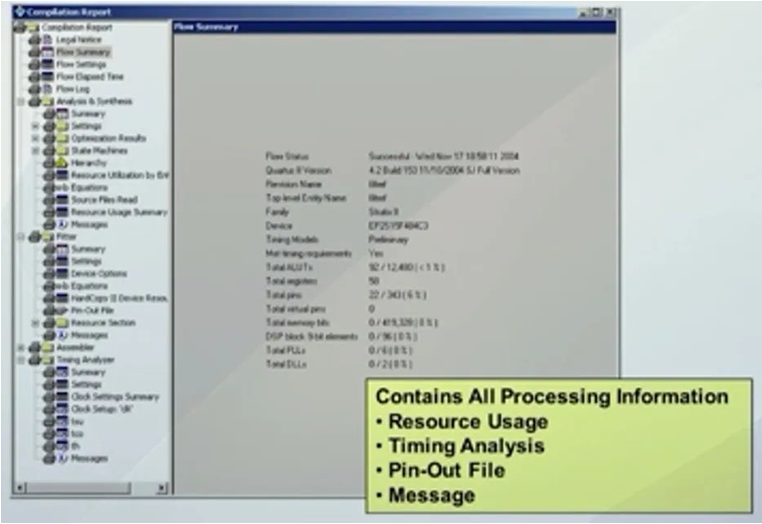

图三是图二右上角部分的放大,展示的是Quarus Ⅱ工具可以报告每一编译子过程的相关信息,如逻辑综合、时序分析、I/O分析等相关信息。

图三,图片来源:学堂在线《IC设计与方法》

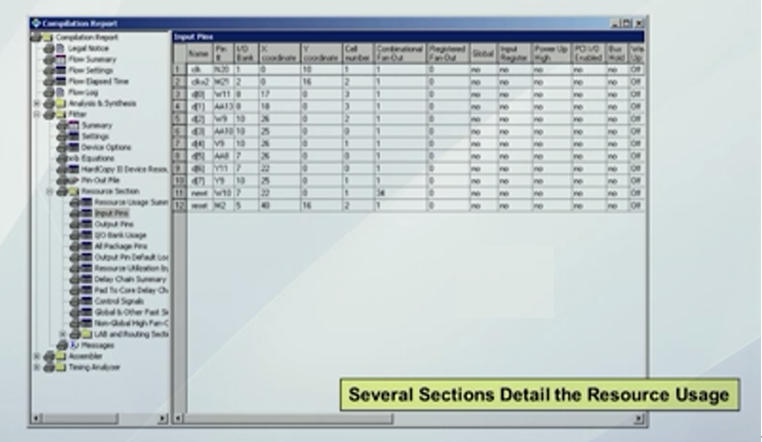

图四是Quarus Ⅱ工具对芯片引脚资源使用(I/O分析)情况的报告,包括输入引脚的信号、名称、是否为特殊引脚等信息。

图四,图片来源:学堂在线《IC设计与方法》

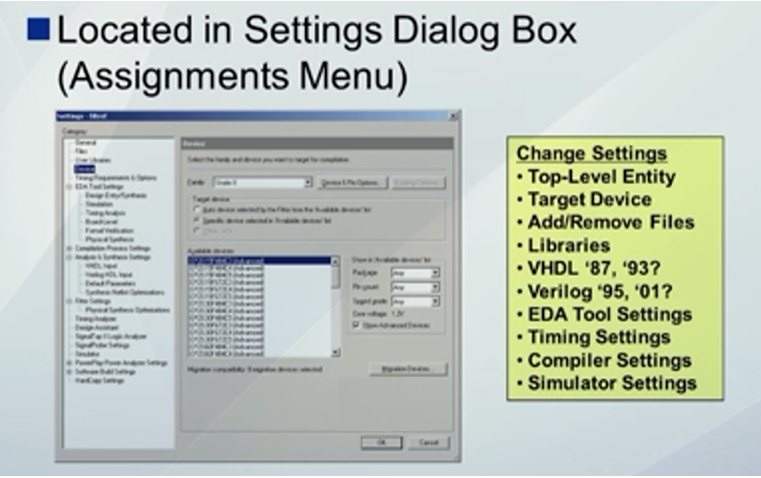

图五展示了Quarus Ⅱ工具逻辑综合(将芯片代码设计转化成电路设计)相关设置界面,需要设计人员检查的设置包括顶层树状结构(Quarus Ⅱ工具会分析芯片设计的树状结构)、目标器件的类型、设计文件和库文件、代码语法标准(确定语法标准采用的版本)、EDA(逻辑综合所使用的平台)工具的选择(Quarus Ⅱ工具内嵌的工具或其他EDA工具)、时序分析设置、逻辑综合操作设置、仿真工具设置。

图五,图片来源:学堂在线《IC设计与方法》

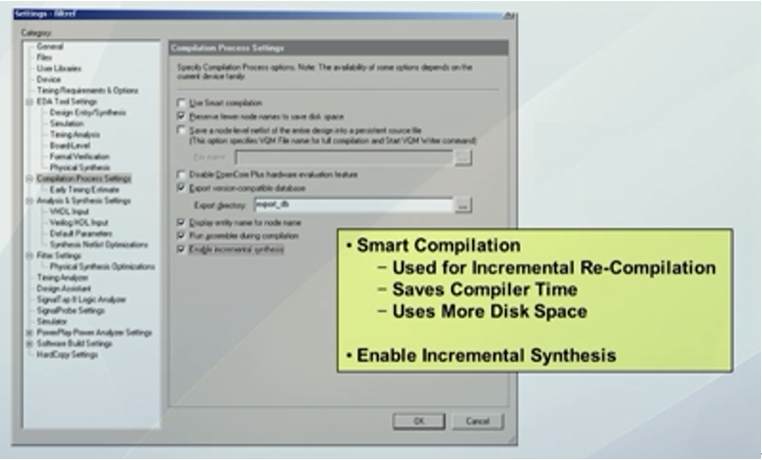

Quarus Ⅱ工具可以提供多种逻辑综合的方法,如智能综合,智能综合采用增量综合方式,可以节省时间和磁盘空间。其他的逻辑综合的方法还包括:节省综合时间的综合方法和使用更多磁盘空间的综合方法(这两种方法课程中未提及,根据图六翻译)。

图六,图片来源:学堂在线《IC设计与方法》

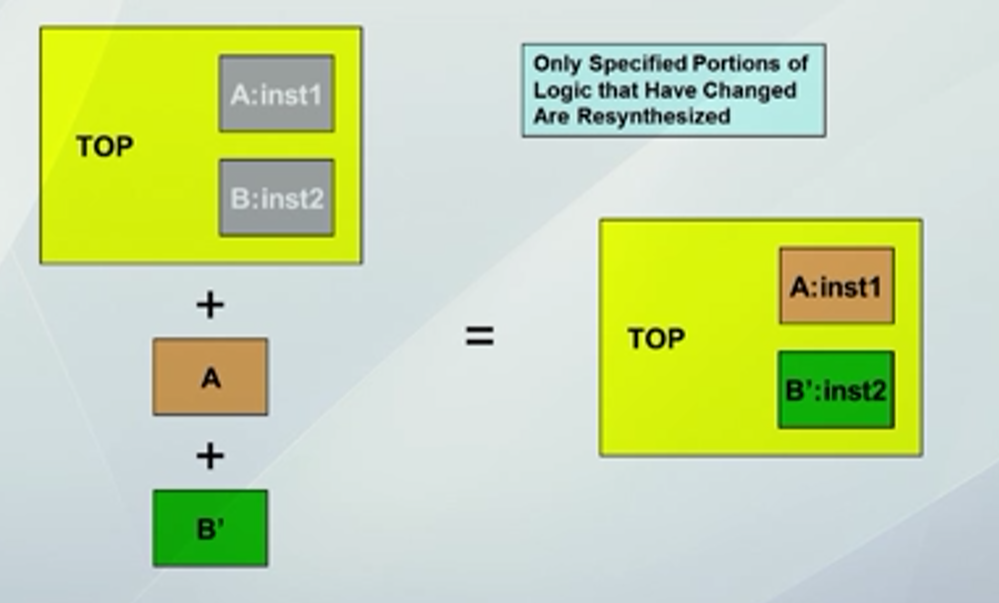

上文提及的增量综合通过只对电路修改部分进行再次逻辑综合,节省时间和磁盘空间。

如图七所示,芯片顶层设计(TOP)包含设计A和B的连接方式,设计A、B的底层设计(具体设计内容)分别包含于A、B中。若第一次逻辑综合后,问题只出现在B的底层设计中,在修改出问题的设计后,软件可以通过只对修改部分(个人理解:顶层设计部分和B的底层设计可能均发生修改,A的底层设计没有修改)进行逻辑综合,以节省时间和磁盘空间。

图七,图片来源:学堂在线《IC设计与方法》

-

IC设计

+关注

关注

38文章

1295浏览量

103914 -

编译

+关注

关注

0文章

657浏览量

32851 -

可编程芯片

+关注

关注

0文章

51浏览量

18617

原文标题:芯片设计相关介绍(28)——Quarus Ⅱ工具部分功能简介(上)

文章出处:【微信号:行业学习与研究,微信公众号:行业学习与研究】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一种基于Logical Effort理论的IC设计方法解析

增大三极管集电极电流Ic的方法

咨询:增大三极管集电极电流Ic的方法

低功耗数字IC设计方法及示例

嵌入式SoC IC 的设计方法和流程

一种全新的深亚微米IC设计方法

基于Logical Effort理论的全新IC设计方法

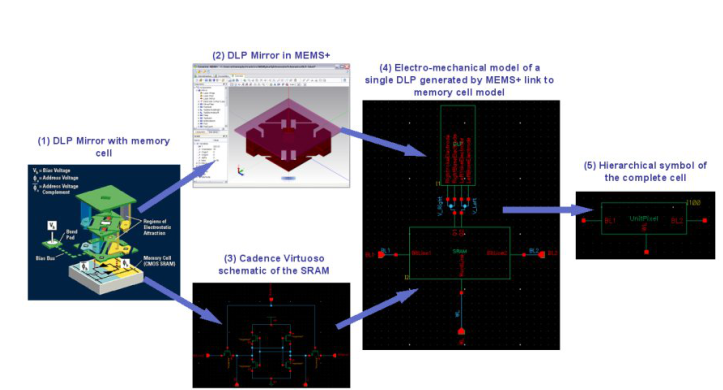

传统MEMS-IC 设计方法和验证的机构化方法介绍

PCB电路设计代换IC的技巧与方法

ic设计是什么专业_IC设计的设计方法

简述进行IC设计的方法和设计流程

IC设计与方法

IC设计与方法

评论