锁存器是具有两个稳定状态的时序逻辑电路,即它是双稳态多谐振荡器。锁存器有一个反馈路径来保留信息。因此,锁存器可以是存储设备。只要设备处于开机状态,锁存器就可以存储一位信息。当使能启用时,锁存器会在输入更改时立即更改存储的信息,即它们是电平触发设备。当使能信号打开时,它会持续对输入进行采样。

取决于触发信号的高电平或低电平,锁存电路可以在两种状态下工作:有效 - 高电平或者有效 - 低电平。

在Active – High锁存电路的情况下,通常两个输入都是低电平,该电路由任一输入上的瞬时高电平触发。

在Active – Low锁存电路的情况下,通常两个输入都为高电平,该电路由任一输入上的瞬时低电平触发。

锁存器主要特性

锁存器是时序电路中的基本构建元素。锁存器没有任何时钟信号,即它们是异步时序电路。

锁存器由静态门组成。

锁存器是一种双稳态多谐振荡器,即它有两个稳定状态并且可以在这些状态之间切换。

锁存器将具有来自输出的反馈路径。因此,它们使用输入信号的先前和当前状态随时改变其输出。

使能后,锁存器的输出会持续受到其输入的影响,即当输入改变时输出会立即改变。禁用时,锁存器的状态保持不变,即它会记住以前的值。时钟或使能信号用作控制信号。

锁存器不断检查所有输入,并在启用时相应地更改其输出。

SR锁存器

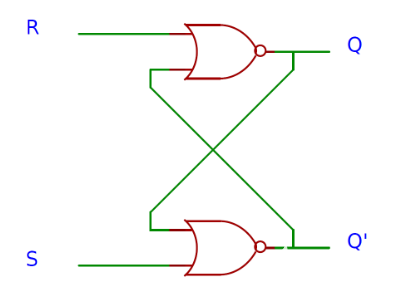

其实,可以使用静态门作为基本构建块来构建一个简单的锁存器,并且可以通过向NOR门电路引入反馈来构建具有两个NOR门。

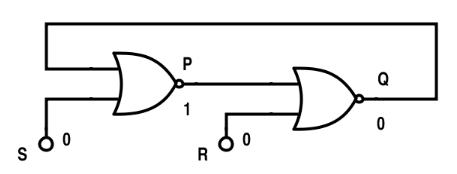

带反馈的简单NOR门逻辑电路如下图所示:

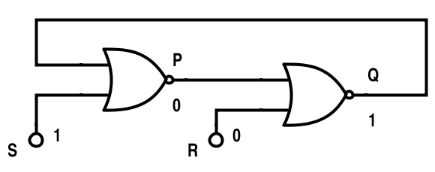

这里,输入S和R都是0 (S = R = 0)。第一个或非门的输出是P = 1。这与R = 0一起被馈送到第二个或非门,因此第二个门的输出是Q = 0。由于电路处于稳定状态,P = 1,Q = 0,如果使 S = 1,则 P = 0,Q = 1,如下图所示:

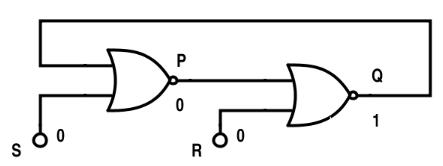

这也是一种稳定的状态,如果S为0,则没有变化,因为Q = 1被反馈给第一个NOR,P仍然保持为0,如下图所示。

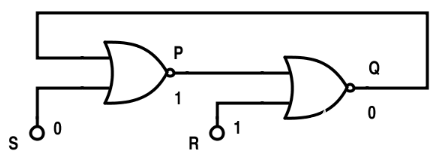

如果R变为1,则Q变为0,这将使P变回1,如下图所示:

如果R为0,那么就没有变化,这样就到达了最开始的地方。

由于输出不仅取决于当前的输入,还取决于过去的输入序列,因此该电路被称为具有记忆性。如果不允许输入条件S = R = 1,则稳定状态输出始终是互补的。当S和R都等于1时,P = 0和Q = 0,这与互补条件相矛盾。因此,输入条件 S = R = 1被认为是不允许的。锁存电路总是画成交叉耦合形式,以强调栅极之间的对称性。

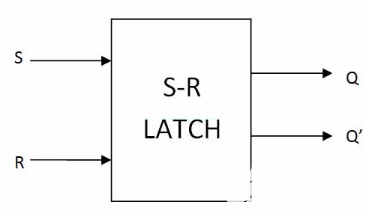

在该电路中,当S=1时,它将输出Q'设置'为 1,当输入R=1时,它将输出Q '重置'为 0。在 S = R = 1的限制下,该电路称为设置 – 复位锁存器(SR锁存器)。

关于竞态条件

在逻辑电路中,竞态条件是指“逻辑电路的两个输入同时变化并使输出暂定的情况”。输入相互竞争以改变输出,它通常发生在将输出作为电路反馈输入的设备中。当设备尝试同时执行两个操作(即同时更改两个输入的状态)时,会出现这种情况。有几种方法可以避免条件竞争,例如使用边沿触发或使用主从触发器。

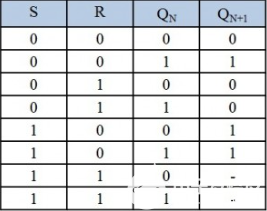

SR锁存器状态表

SR锁存器状态表(真值表)提供有关电路状态的信息,由于时序电路的输出取决于当前和先前的状态,因此这些以称为状态表的表格形式表示,并根据当前状态和其他输入显示下一个状态。

SR锁存器的状态表如下所示:

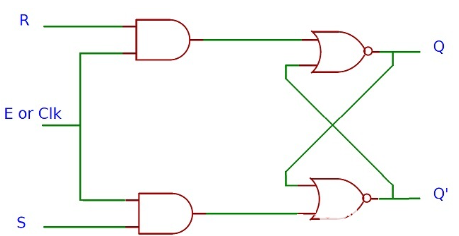

门控SR锁存器

通常情况下,锁存器都是即时的,即当输入发生变化时,输出会立即发生变化。但对于许多应用来说,最好有一个隔离期,即使输入发生变化,输出也不会发生变化。在此期间,输出被称为真正“锁定”。这可以通过使用额外的输入(使能或时钟或门)来实现。如果使能(或时钟或门)信号未置位,则忽略输入并将输出锁存到先前的值。为了使用这个额外的信号,应该添加额外的逻辑,这些电路称为门控SR锁存器。

门控SR锁存器可以通过两种方式制成:通过将第二级与门添加到SR锁存器或通过将第二级与非门添加到反向SR锁存器。

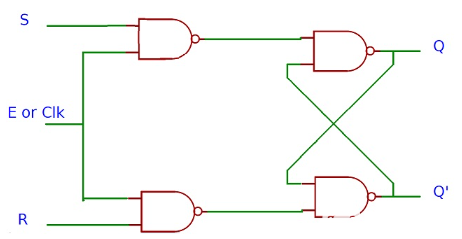

由NOR门构成的门控SR锁存器的电路图如下所示:

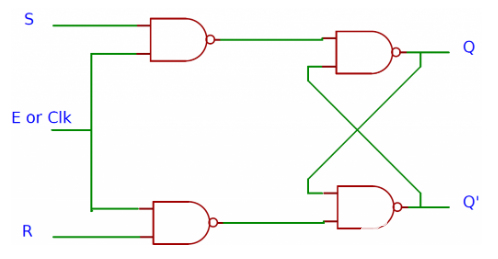

由NAND门构成的门控SR锁存器的电路图如下所示:

当NAND门将输入反相时,反向SR锁存器变为门控SR锁存器。当使能(或时钟)为高时,锁存器被称为启用状态,即输出响应输入。当使能(或时钟)为低电平时,锁存器被禁用并保持在该状态,直到使能启用。

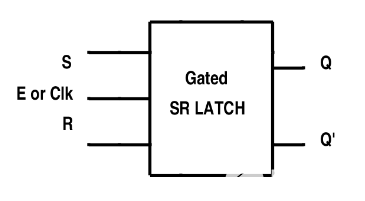

门控SR锁存器的符号如下图所示:

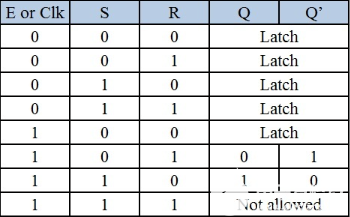

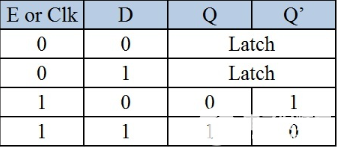

门控SR锁存器的真值表如下图所示:

D锁存器

数据锁存器或延迟锁存器(D锁存器)是存储数据的简单锁存器之一,它也被称为透明锁存器。一个简单的D锁存器可以由两个NAND门构成。

当S = R = 1时发生的SR锁存器中的竞态条件可以在D锁存器中避免,因为R输入被重命名为D的反转S替换。因此没有非法或禁止的输入。在 D锁存器中,Q始终为D。

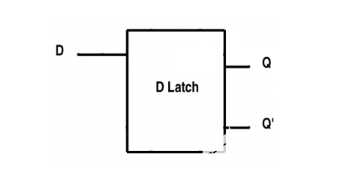

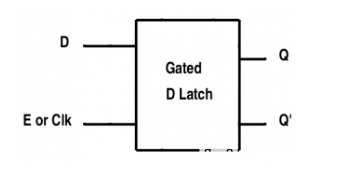

D锁存器的符号如下所示:

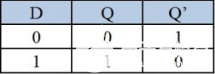

这些简单的D锁存器不常用,但门控D锁存器很常见。简单D锁存器的真值表如下所示。

门控D锁存器

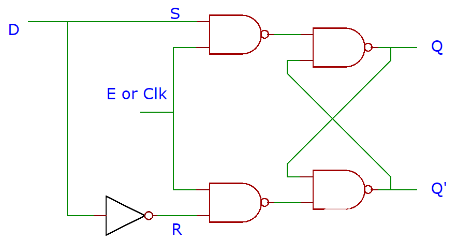

通过修改门控SR锁存器可以轻松构建门控D锁存器。对门控SR锁存器的唯一修改是必须将R输入更改为反相S。由NOR SR锁存器形成的门控锁存器如下所示。

当时钟或使能为高电平(逻辑 1)时,输出会锁存D输入上的任何内容。当使能或时钟为低电平(逻辑 0)时,最后一个使能高电平的D输入将是输出。

这个锁存电路永远不会遇到“竞争”情况,因为单个D输入被反转以提供给两个输入。因此,没有机会获得相同的输入条件。所以D锁存电路可以安全地用于任何电路。

门控D锁存器的符号如下所示:

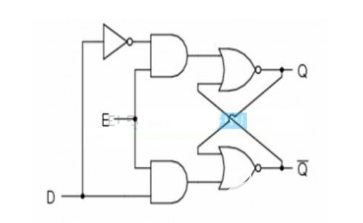

与门控NOR SR锁存器类似,门控D锁存器也可以由门控NAND SR锁存器构成。门控NAND SR锁存器的门控D锁存器电路如下所示。

当然,可以避免使用反相器,因为可以使用与非门来获得反相值。上述电路需要进行一些修改,得到的电路如下所示:

门控D锁存器的真值表(或状态表)如下所示:

锁存器的应用

锁存器的应用主要包括以下几个方面:

它们是基本的1位存储设备。

D锁存器通常用作异步系统中的I/O端口。

数据锁存器有时用于同步两相系统中以减少晶体管数量。

锁存器的优点

锁存器的优点包括以下几方面内容:

速度更快,因为它不需要等待时钟信号,最常用于高速设计。

需要更少的电力。

基于锁存器的设计具有小芯片尺寸。

主要优点是“借时”。其中,如果某项操作未在规定时间内完成,则从其他操作时间借用执行该操作所需的时间。

锁存器的缺点

锁存器的缺点包括以下几方面内容:

锁存器不太可预测,因为有更多机会影响竞争条件。

电平敏感设备,因此亚稳态的机会更大。

由于锁存器电路的电平敏感特性,所以分析锁存器电路很困难。

总结

简单来说,锁存器,就是数字电路中的一种具有记忆功能的逻辑元件,可以在特定输入脉冲电平作用下改变状态。

需要注意的是,锁存器输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态才被保存到输出,直到下一个锁存信号到来时才改变。

-

锁存器

+关注

关注

8文章

906浏览量

41495 -

时序逻辑电路

+关注

关注

2文章

94浏览量

16538 -

SR

+关注

关注

1文章

35浏览量

23412

发布评论请先 登录

相关推荐

锁存器的主要特性、种类及应用

锁存器的主要特性、种类及应用

评论