随着连续几代 PCI Express 以 8 Gbps、16 Gbps 和 32 Gbps 的速度运行,动态链路均衡变得至关重要。均衡会补偿通信信道对信号的影响。

这些影响包括充当低通滤波器的链路,它会衰减数据流中的关键高频分量,此外,由连接器和过孔引起的链路阻抗不连续会进一步降低链路性能。

PCIe均衡可应用于发送端 (TxEQ)、接收端 (RxEQ) 或两端都应用, TxEQ 涉及去加重和预冲,而 RxEQ 涉及连续时间线性均衡 (CTLE) 和判决反馈均衡 (DFE)。

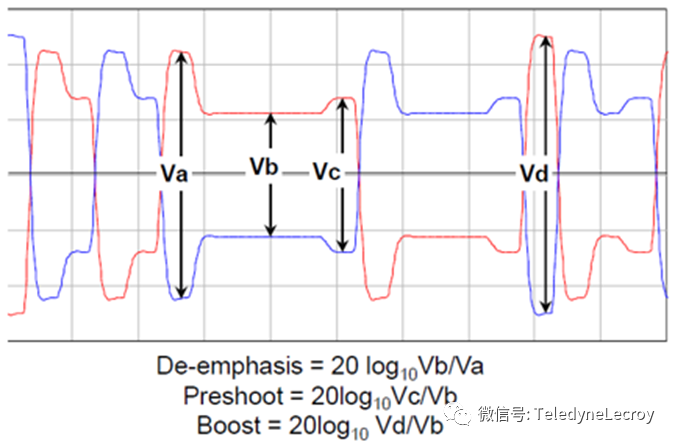

在发送端,去加重会使跳变后的第一位以全幅度 (Va) 发送,相同极性的后续位以降低的电平 (Vb) 传输,但在下一次跳变之前的最后一位除外,它以提高的预冲电平 (Vc) 传输。此外,转换之间的单个bit位以最大增强电平 (Vd) 传输。

去加重和增强的组合补偿了链路会衰减的信号高频成分。均衡涉及多个阶段的链路训练序列,有时会产生意想不到的结果。

使用 PCIE CrossSync PHY关联协议层和物理层数据的能力可以帮助定位链路训练后可能出现的逻辑和电气问题。

PCIE链路训练过程

发送端均衡(去加重、预冲和增强),是由 PCIe 系统的 TxEQ内的三抽头有限脉冲响应 (FIR) 滤波器实现。链路训练的目标是确定给定通信链路的最佳 FIR 滤波器系数,也称为游标系数。链路训练在下行端口和上行端口之间交换有序数据集,包括TS1训练序列和TS2训练序列 。

PCIe 链路训练是如何运行的?

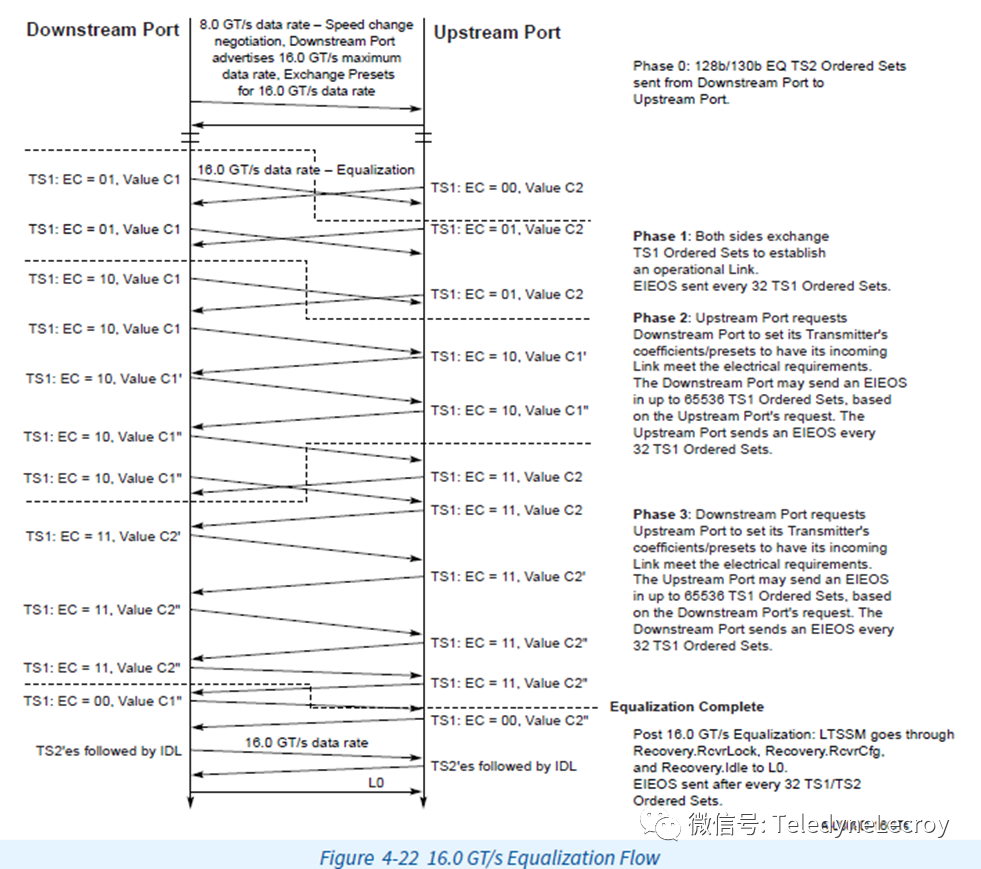

以PCIE4.0为例,PCIe 4.0 链路训练从速度变化协商开始,有4个阶段,阶段 0 到阶段 3。在阶段 0,下行端口以 8GT/s 数据速率向上行端口发送 TS2 有序集,通告 16GT/s 的最大数据速率。在阶段 1,两个端口交换 TS1 有序集,在每 32 个 TS1 有序集之后穿插一个电气空闲退出有序集 (EIEOS),以建立操作链路。

EIEOS 的目的是保证链路伙伴可以检测到电气空闲退出状态,EIEOS 数据包符号(四个交替的 00 00 FF FF 序列)产生规则且具有相对较少的转换的电信号,这对于在调试期间观察信号的物理层属性非常有用。

Presets和P10的作用

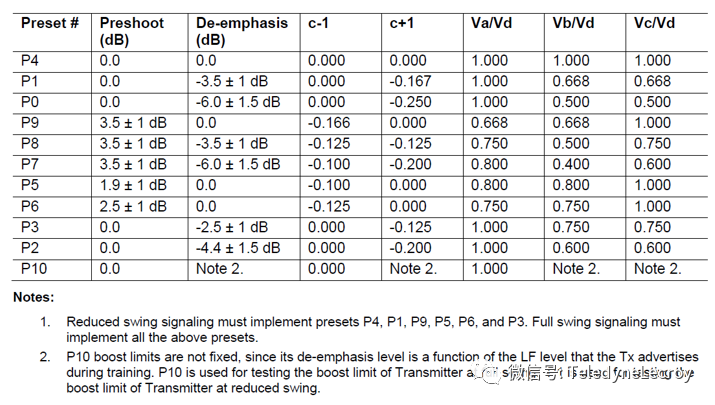

随后的阶段涉及数据交换以优化电气性能。PCIe 标准规定了 11 种去加重、预冲和增强游标系数的预定义组合,称为Preset,并标记为 P0 到 P10。

在链路训练期间,PCIe 设备会请求Preset或游标系数——后者提供更精细的设置选项,而Preset提供快捷便利。Preset是根据电压比,以及前冲和去加重系数(以 dB 为单位)定义的。

但 P10 除外,它用于在全幅度下进行发射机升压限制测试,并且其升压限制不固定,主要用于测试。

在第 2 阶段,上行端口请求下行端口配置其发射机均衡Preset或游标系数,以补偿链路通道并确保最佳性能。阶段 3 交换角色,下行端口请求上行端口配置其发射机均衡Preset或游标系数以补偿链路。均衡训练完成后,下行端口和上行端口交换TS2有序集。

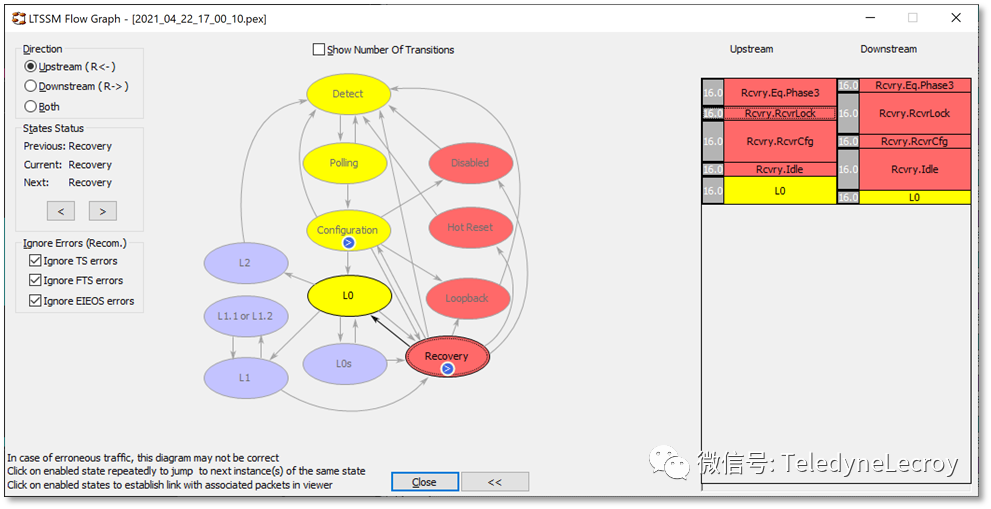

链路训练和状态机 (LTSSM) 会经过 Recovery.RcvrLock、Recovery.RcvrCfg 和 Recovery.Idle 状态,在每 32 个 TS1 或 TS2 有序集之后发送一个 EIEOS,然后再建立活动 L0 状态。因此,TS2 有序集和 EIEOS 可用于触发仪器和定位物理层信号,以帮助调试均衡后的链路训练行为。

比较Preset和报告的TxEQ

要在实际系统中验证链路均衡,可以使用示波器和协议分析仪,以及力科的PCIE CrossSync PHY软件,将两台仪器链接在一起。

CrossSync PHY 安装到示波器上,将来自两台仪器的数据关联起来,以提供完整的链路可见性,让您可以查看与协议分析仪的协议层数据在时间上相关联的来自示波器的物理层波形。

此外,具有 CrossSync PHY 功能的信号采集卡可以监测被测器件并向协议分析仪和示波器提供数据。

如何设置触发

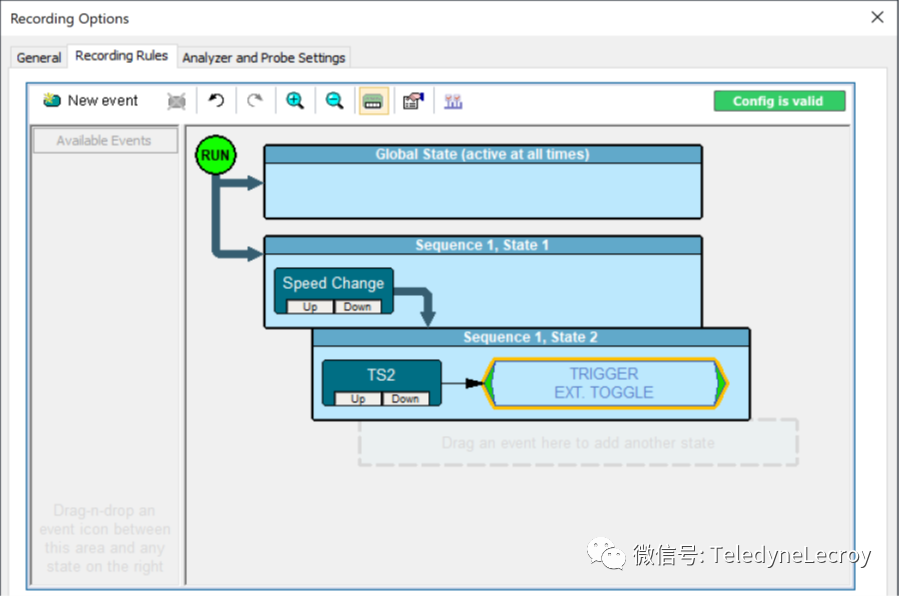

要确定链路均衡过程的有效性,需要在第 3 阶段结束时检查链路行为。

为此,将协议分析器配置为在速度更改为 16 GT/s 后出现的第一个 TS2 有序集上触发 ,并设置示波器以捕获多个链路的上行数据。此触发设置将确保在完成最终均衡设置并转换到活动 L0 状态后捕获数据。

如何检查确认报告的Preset

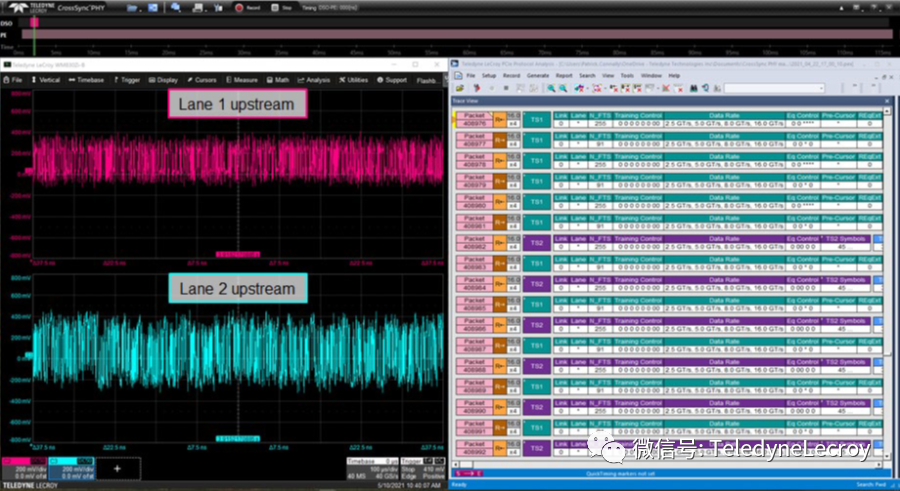

CrossSync PHY 上显示的协议数据显示了数据包详细信息,例如数据包编号、有序集、数据速率和均衡控制,其中也包括Preset值。CrossSync PHY 还显示了与协议数据在时间上相关的的示波器波形,显示了发射机均衡的电气效应。

下图中的示波器波形显示了通道 1 和通道 2 上行信号的电气行为明显不同。为此,将协议分析器配置为在速度更改为 16 GT/s 后出现的第一个 TS2 有序集上触发 ,并设置示波器以捕获多个链路的上行数据。 此触发设置将确保在完成最终均衡设置并转换到活动 L0 状态后捕获数据。

确定是逻辑问题还是电气问题?

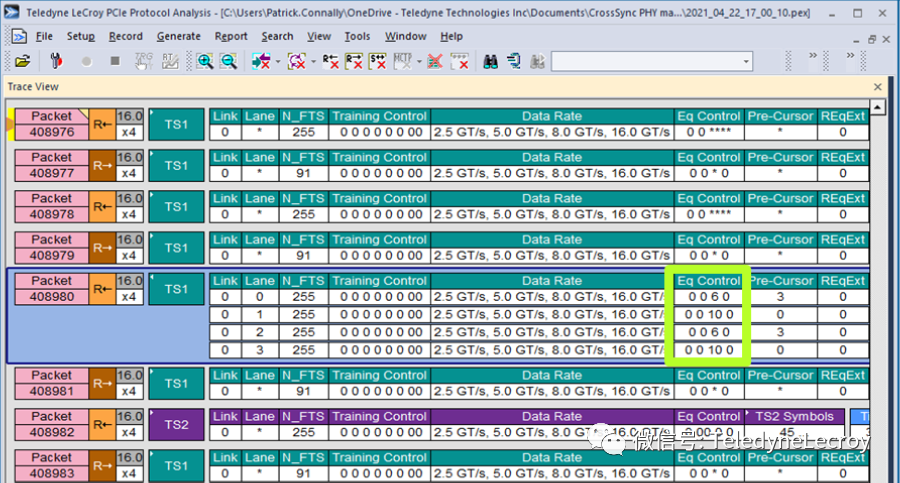

仔细查看阶段 3 结束时报告的 TxEQ 协议层数据,显示通道 0 和 2 报告已训练到 TxEQ P6,而通道 1 和 3 报告已训练到 TxEQ P10。这个结果表示了潜在的意外行为,可能是因为一个通道误报了其状态。

一个设备训练不同的通道到不同的 TxEQ Preset并非不可能,而且 P6 是一种相对常见的Preset,许多设备在 16 GT/s 的信号质量合规性测试中会使用它。但是,P10 并不是期望在实时链接中看到的Preset。

如前所述,它的存在主要是为了方便设备电气测试,如果链路另一端的设备请求 P10,它不知道会发生什么。

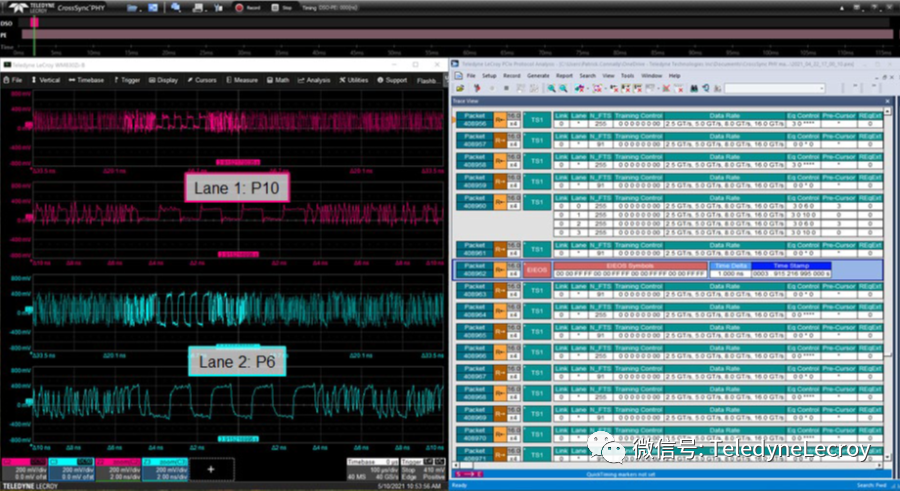

放大物理层波形以检查去加重程度

问题是通道 1 是否真的被训练到 P10,或者它是否错误地报告它被训练到 P10。换句话说,这个意料之外的结果表示的是纯粹的逻辑问题还是逻辑电气问题?

要进一步验证,可以在协议数据中,在第 3 阶段结束附近选择一个 EIEOS 数据包,以放大相应的示波器波形。EIEOS 数据包具有相对较少的转换,在示波器时域波形上可以清楚地看到两个信号之间的去加重差异。

如下图所示,报告说它被训练到 P10 的通道比报告说它被训练到 P6 的通道在转换后对信号的去加重程度要高得多。进一步的验证证明,P10 通道比训练到 P6 的通道眼张开度小的多。此处的解决方案是检查导致设备训练到 P10 的逻辑问题的固件。

总结

力科的PCIE CrossSync PHY 软件可同步示波器和协议分析仪,让您可视化、保存、调用和分析同步的示波器和协议分析仪数据,以帮助解决 PCIe 均衡过程中可能出现的意外问题。一个与均衡后的链路行为相关的示例演示了如何使用 CrossSync PHY 软件来调试异常链路行为。

除了验证有问题的链路训练行为外,PCIE CrossSync PHY还可以通过对边带信号、参考时钟、数据通道和电源轨的可见性来帮助表征整个启动序列,帮助观察电气和协议域中的速度变化。

-

分析仪

+关注

关注

0文章

1507浏览量

52043 -

示波器

+关注

关注

113文章

6240浏览量

184792 -

软件

+关注

关注

69文章

4921浏览量

87388

原文标题:调试PCIE链路动态均衡

文章出处:【微信号:美国力科TeledyneLeCroy,微信公众号:美国力科TeledyneLeCroy】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AD7767-1采用4路菊花链连接,当大于Vref/2之后数据异常,为什么?

CCSDS空间遥控链路异常行为检测算法

基于光流计算的异常拥挤行为检测算法

基于智能监控的中小人群异常行为检测

AIS数据在船舶异常行为检测

消息和指令分析相结合的网络协议异常行为分析

基于用户窗口行为的内部威胁异常检测

如何使用CrossSync PHY 软件来调试异常链路行为

如何使用CrossSync PHY 软件来调试异常链路行为

评论