如果要评选电子工程师近20年来的最耳熟能详的专业词汇,眼图和抖动作为孪生姊妹一定在前10之列。所以业界关于抖动的论述和文章也是时常见诸各种媒体和平台。

本期我们将就抖动和抖动测试做一个专题介绍,包括如下主题:

01. 抖动研究的源起

02. 抖动测试和分析的基本方法和经典理论

03. 抖动测试的演进和新挑战

04. 影响抖动测试结果和精度的因素

1. 抖动研究的源起

抖动测试最早在上个世纪80年代开始萌芽,HP公司电信网络测试部门-苏格兰科技公司1982年在苏格兰推出了针对PDH(Plesiochronous Digital Hierarchy,准同步数字体系)的第一个抖动测量仪器,速率高达E3和DS3,之后在1984年推出首批140 Mb / s抖动测试仪之一。

在90年代推出针对SONET / SDH抖动测试产品和方案。事实上在同步数字传输体系(SONET/SDH)和通讯系统中引入抖动的概念主要用于评估数据包级的传输延时偏差。因此大家也可以看到经典抖动定义也来自于当年的业界巨擘贝尔实验室。

进入90年代以后,随着数字电路系统中的源同步时钟总线的发展,由于外部同步时钟频率渐渐成为瓶颈开始转向嵌入式时钟的串行差分总线,非常典型的就是PCI总线同步时钟频率最高到133MHz就开始转向PCIE1.0 2.5Gbps发展。由此对数字电路系统中的水平时间参数的测量也从传统的Setup/Hold或Skew测量转为水平方向Jitter的测量。

在今天,抖动测试除了是很多高速串行总线和标准的一致性测试众多项目中的重要组成部分和内容,同时还是针对系统级传输性能评估的重要方法,以及探究系统问题根源的重要手段。因此对抖动进行深入的探索和研究无论何时都具有深刻的意义和价值。

2. 抖动测试和分析的基本方法和经典理论

在90年代,伴随着数字电路和系统的串行差分化的同时以x86处理器为核心的软硬件系统广泛应用于各行业,当然也包括测试测量行业,示波器也开始全面武装更强大的x86处理器和windows操作系统,随之而来的是各种算法程序的全面发展和推进,这其中就包括了抖动测量算法和分离的经典理论。

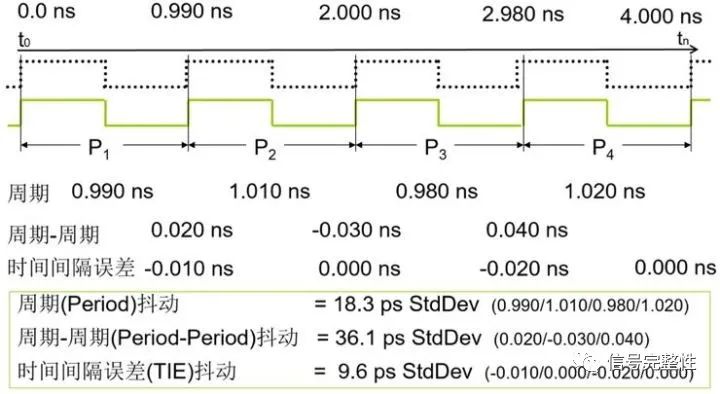

下图显示的是充斥于各种文献的抖动测量中三种基本的抖动算法:

图1 基本抖动算法示意图

周期抖动算法比较简单,以信号本身的每个周期值为样本进行统计分析,可以反映所有样本的平均值及个体与圆心即平均值偏差的情况,用于一般的时钟信号的评估。

周期-周期抖动以两个相邻周期的周期差值为样本进行统计分析,很明显这是对信号周期的一阶微分运算,这一指标对分析锁相环的性能时有很高价值。由此还衍生出N周期—N周期抖动,比如针对DDR总线的时钟测试中就有5/10个连续时钟周期抖动的测试。

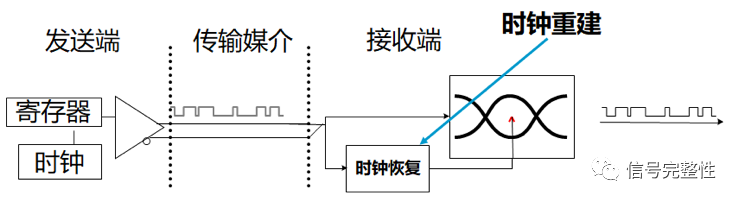

第三个度量方法,时间间隔误差(Time Interval Error,简称TIE)抖动,有时也被称作相位抖动(Phase Jitter),以每个周期点的累计时间值相对当前时间点的理想值偏差为样本进行统计分析,这个时间偏差算法呈现累积效应,是一个积分运算,可以反映出信号的长期抖动,而这一理想位置则需要通过软件时钟恢复(实时示波器方法)或者通过外部输入/硬件时钟恢复(采样示波器方法)得到一个参考时钟作为运算的基准。

TIE抖动在今天的数字电路与通信系统中已经成为分析数据传输中的抖动指标和性能的最为通用的抖动度量方法。关于以上三个经典抖动算法定义和描述,推荐阅读Ref [6]-- PCI ExpressTM Jitter Modeling Revision 1.0RD.

图2 时间间隔误差抖动测量方法示意图

除了上述三个度量方法还有常用到的三个统计学参数:

平均值:相对绝对值的一个固定偏移或偏差,通常不重要因为可以修正。

RMS抖动:通常用于表征随机抖动成分。

Peak-to-Peak抖动:可用于表征确定性(有界)和随机(无界)抖动分量,另外必须在给定的BER下引用或考虑随机(无界)抖动。小测验:

在实时示波器进入windows时代前,业界的老师傅们经常用无限余辉累积触发位置后的一个时钟周期边沿,然后用光标测量边沿累积后的时间宽度值,如下图示,请问这是哪种抖动?

A. 周期抖动 B. 周期-周期抖动 C. TIE抖动

图3 实时示波器上经典抖动测量示意图

思考:

采样示波器在进行分析眼图时也会得到一个抖动测量值,这又是什么抖动呢?

A. 周期抖动 B. 周期-周期抖动 C. TIE抖动

必须要说明的是,业界针对抖动的研究和分析其实最初是从采样示波器开始。因为上个世纪90年代末采样示波器相比实时示波器可以实现的带宽更高(因为等效采样无需高采样率配套,且无需考虑普遍信号测试需求通常输入信号幅度有限因此无衰减和放大器电路因而带宽更高),同时高ADC位数提供的测量精度也更高,因此首先被用于高速芯片及一些器件如光模块等串行数据的眼图分析,并根据眼图结果衍生出抖动分析和测量。

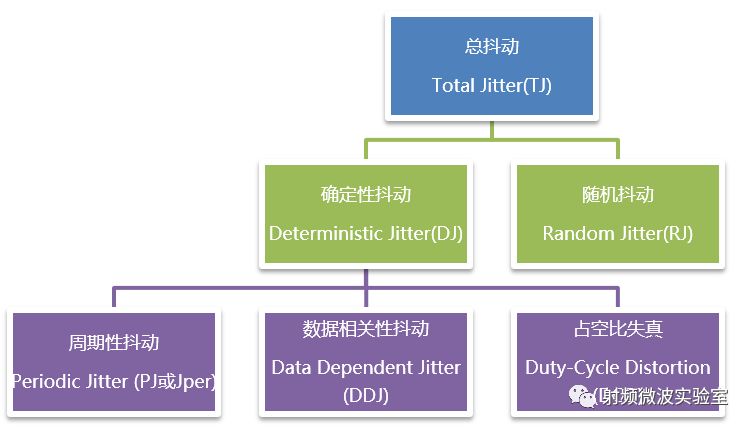

基于眼图堆叠和测量结果,为了评估数字串行总线传输的总体性能因此引入抖动的分析和评估理论。采用的重要评价指标是特定误码率(通常是10E-12)水平下的总抖动Tj @ BER,因为 Eye Open= 1UI – Tj @BER。

那么如何得到总体抖动这一结果呢?

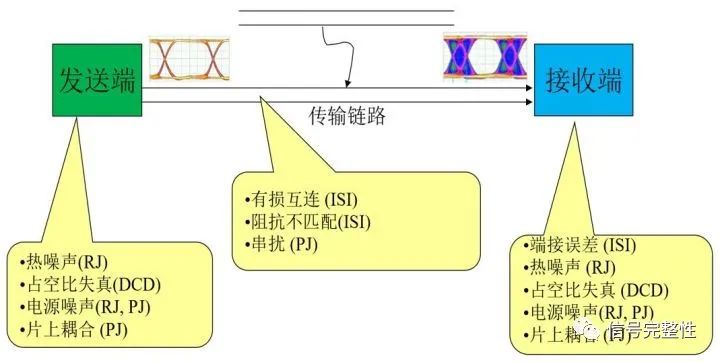

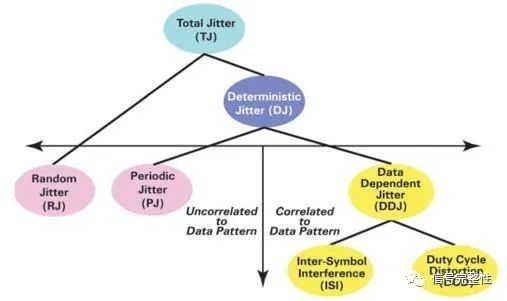

图4 典型的串行传输链路中的抖动根源

一种方法是根据上图中抖动根源按图索骥分别测量得到Rj和各种Dj成分然后卷积得到给定误码水平下的抖动概率密度函数然后推算出Tj。显然这一方法的可操作性不高尤其是早年基于采样示波器叠加的眼图结果进行抖动分析的状况。

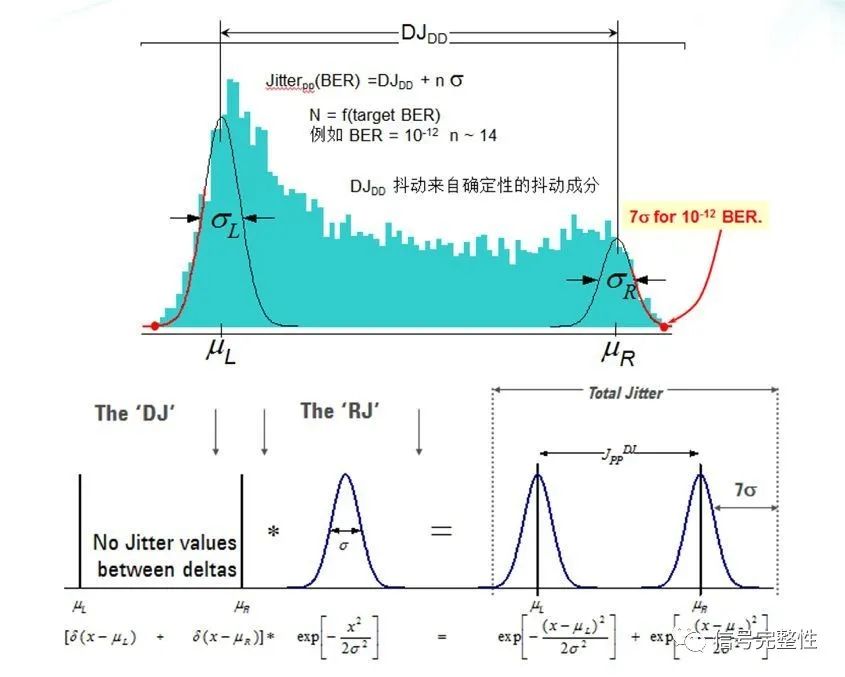

另一种方法就是双狄拉克模型法(Dual-Dirac Model),通过测量和计算Rj(δ)与Dj(δδ)再根据如下公式:

Tj@BER = n x Rj +Dj

计算得到Tj@BER。通常10E-12误码水平时n=14 (因篇幅限制,本文不就n与BER关系做过多描述,参考Ref[1])。

双狄拉克模型法有5个假设前提:

1. 总体抖动可以分解为Rj和Dj

2. RJ遵循高斯分布,可以用单个相关参数的术语进行完整描述,RJ的rms值分布,或等效地,高斯分布的标准偏差σ

3. Dj遵循有限和有边界的分布

4. DJ遵循由两个Dirac-delta函数形成的分布。两个delta函数的时间延迟分离给出了双狄拉克模型相关DJ,如下图所示

5. 抖动是一种静止现象或者可重复观测。也就是说,测量了在适当的时间间隔内对给定系统的抖动后无论何时再启动该时间间隔范围的测量,都会给出相同的结果

双狄拉克模型法基于眼图左右交叉点的抖动直方图,提供了最简单的概率密度函数:交叉点分为两个Dirac-delta函数,位于μL和μR(DJ主导区域),然后采用人为拟合快速过渡到RJ主导的尾部。有许多方法可以实现双狄拉克模型,在所有这些模型中,估计总体抖动的主要问题是如何描述抖动分布尾部的问题,两个标准偏差为σ的高斯分布的尾部由固定量DJ(δδ)= |μL - μR|分隔。

图5 双狄拉克模型分解RJ和DJ示意图

有的时候还会经常看到另一个测量结果DJ(p-p),这个如何理解?

真实的DJ从不遵循简单的双狄拉克分布,因此期望从双狄拉克模型中提取的DJ接近实际的峰峰值DJ是不合理的。DJ(δδ)是模型相关量,必须在假设DJ遵循由两个Dirac-delta函数形成的分布的情况下导出,如图5所示。

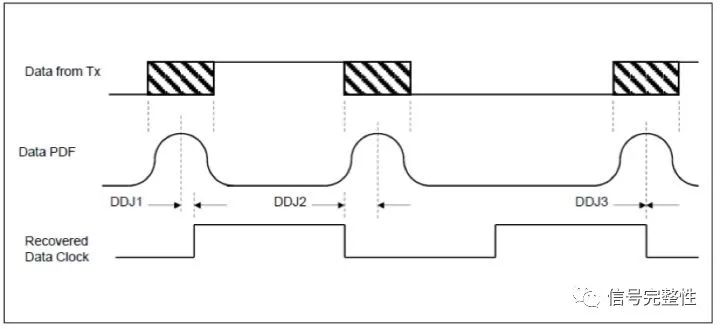

相比DJ(δδ)总是可以测量得到,而DJ(p-p)只能在特定情况下可测。比如当DJ仅由数据相关抖动(DDJ)组成时,可以通过比较重复数据码型的平均跳变次数来测量。通常DJ(δδ)小于DJ(p-p)。因此总结,DJ(δδ)定义明确且可测,而DJ(p-p)仅能在特定情况下测量得到,而且对估计总体抖动没有作用。

顺便提一下,虽然DJ(p-p)无法测量且意义不大,但是DJ的子成分如DDJ(p-p)和ISI(p-p)却是有界且可测,在实时抖动分析结果里经常可以看到。

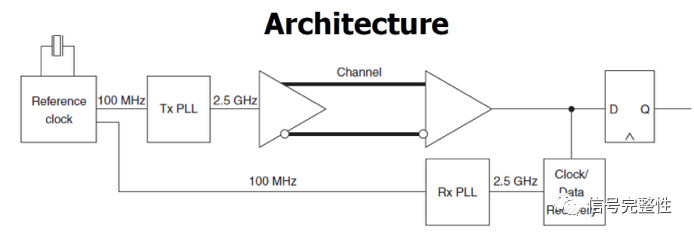

针对一个典型的包含发送端,传输链路以及接收端以及CLK的典型系统架构,比如PCIExpress:

图6 典型的PCIExpress架构

通过分别测量和分析得到系统各单元的Rj标准偏差和Dj(δδ)后可以得到整个系统的抖动参数:

之后就可以得到整个系统在特定误码率下的总体抖动。关于双狄拉克模型的相关原理及知识,请参考Ref [1].

由于采样示波器在早期只是纯粹进行眼图叠加进而进行总体抖动估算而很难对具体的成因进行分析,因此无法满足很多的应用需求(直到2006年左右在采样示波器上开发出码型同步触发技术从而可以稳定捕获特定码型比如不长于2ˆ16的PRBS码型,才引入了抖动分解技术)。

随着实时示波器在平台和性能上的大幅提升,在实时示波器上进行抖动分析越来越普遍并渐渐成为主流。实时示波器无需外部触发或同步时钟信号,同时相比采样示波器具有长内存可以一次触发采集一定时长的波形用于抖动分析进而做出对实际工作有指导性的抖动分解结果。

那么首先实时示波器如何进行抖动分析呢?

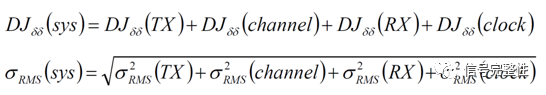

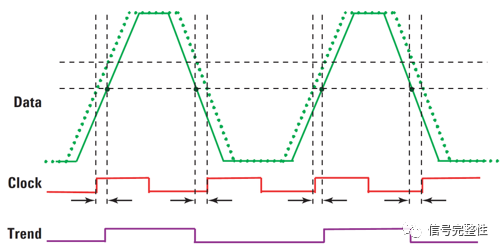

如下图示,实时示波器首先捕获一定时长的波形,然后基于特定标准的数据的时钟恢复算法通常为一阶或二阶锁相环,带宽因标准差异而不同,针对CLK通常采用Constant CLK即首先计算周期的平均值得到基准,分析得到信号的TIE抖动。

基于此TIE抖动结果,抖动分析软件会分析得到抖动趋势图(Trend),这一趋势图提供了每个时间点的数据边沿位置相对于理想位置时间差即TIE的趋势图。如果是数据相关抖动DDJ如ISI则会显示出与数据码型的强相关性,如果是周期性抖动Pj成分则会显示出与其它特定频率信号的相关性。

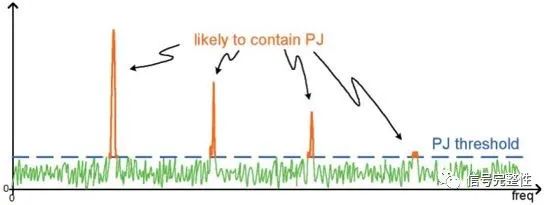

分析抖动的另一种方法是采用频域角度,针对TIE抖动趋势图做FFT数学函数,基于重复频率成分的抖动视图角度。在这种情况下,数据结果被处理绘制为垂直轴上的定时误差值与水平轴上的频率。这个角度在寻找与数据本身特征不相关的周期抖动Pj时,会特别有用。

实时抖动分析软件还提供了“直方图”视图,将抖动分析结果显示为概率分布的函数(PDF)(数据记录中所有TIE测量结果合成),表现为定时误差与命中数(N)的二维显示。实时直方图的结果应该与从眼图产生的重复直方图的测量结果密切相关。但是,通过实时采样的长存储深度,可以从单次采集信号中获得更多数据。此外,基于实时示波器的重复多次采样,可以产生更准确和完整的PDF。

图7 EZJIT软件实时抖动分析的处理方法

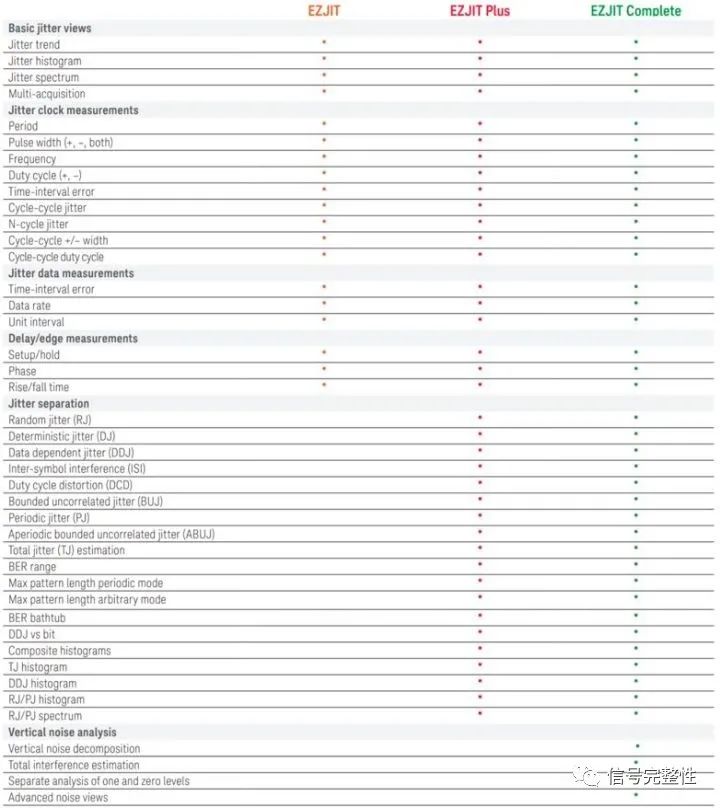

Keysight实时示波器抖动分析软件EZJIT提供的功能就到这里。

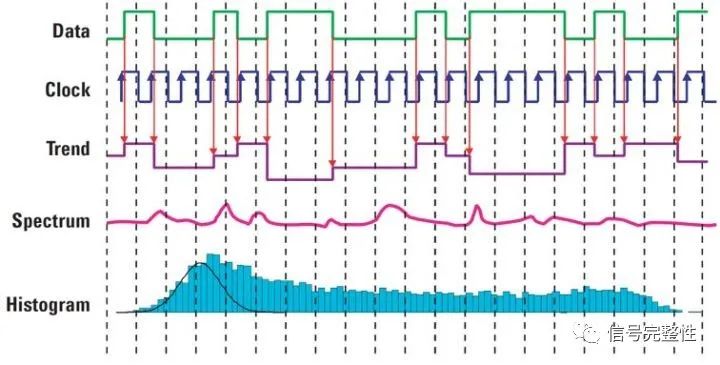

然后,实时抖动分析软件是如何进行一步步的抖动成分分解的? 抖动分解是EZJIT PLUS的功能。如Ref[2] [3]文献描述,根据经典抖动成因分解模型:

图8 经典抖动成因分解模型

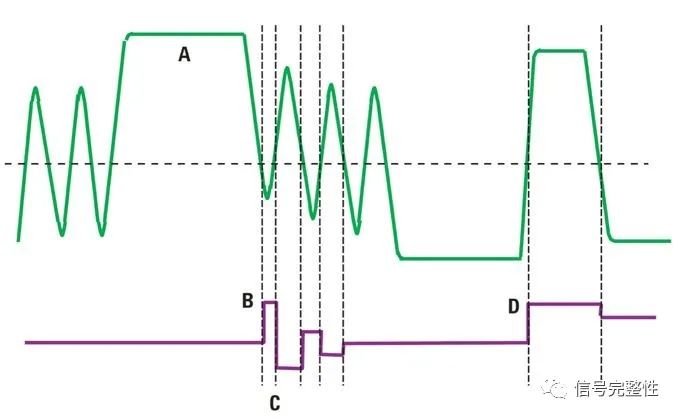

首先第一步,根据数据码型特点(在EZJIT Plus软件里可以选择Periodic Data 或Arbitrary Data)将DDJ(数据相关抖动,主要是ISI即码间干扰)和RJ和PJ(与数据无关抖动成分)分离开来;根据DCD和ISI的不同表现再进行分离。

有时甚至可以采用发送特定如101010…码型以准确测量DCD抖动。在Arbitrary Data模式下EZJIT PLUS软件使用线性回归技术从TJ中提取DDJ。这种线性回归类似回声消除或其他自适应滤波应用。这一线性回归技术要求设定一组系数来描述数据相关抖动的如何从传输的数据码型计算,EZJIT PLUS软件里指这套系数为ISI Filter。(关于如何设定ISI Filter请参考Ref [5])

图9 典型DCD(左)和ISI(右)

第二步,基于第一步已经去除了DDJ成分的频谱图将PJ和RJ分离。对功率谱密度积分推导出RJrms,PJ成分求和可以得到PJrms。针对RJ的特性在EZJIT Plus软件里可以设定RJ的带宽,如白噪声为宽带宽,粉红噪声为窄带宽。(相关说明请参考Ref[3])

图10 分离了DDJ后高于设定阈值的被当作PJ,去除后就可以根据剩余的频谱分量计算RJrms

第三步,根据TIE的直方图视图结果基于前面描述的双狄拉克模型法拟合出DJ(δ-δ)。结合前面的频谱法拟合出的RJrms,就可以确定要求的误码率水平下的总体抖动即TJ@BER,基于此可以绘出浴盆曲线(Bath Tub)等图表。

到这里EZJIT PLUS就完成了实时示波器的抖动分析和分解的全部过程,最终输出包括分解完毕的各个抖动分量值,总体抖动@给定BER水平,浴盆曲线等。这也是我们进行抖动分析和分解最终需要得到的结果。

为了获得准确的分析和测量结果在进行实时抖动软件分析时必须进行正确的设置,包括恰当的信号垂直刻度,足够的波形数据也就是捕获时长,以及足够的采样率设置等等因素,另外针对前面提到的包括数据周期重复模式还是任意码型,RJ带宽及噪声设置,以及如何设置ISI滤波器尺寸等详细请参考文末所列参考文献2,3,4,5等。

另外要强调的是足够的波形数据和捕获时长除了可以捕获更多的时钟周期或数据UI进行更准确的抖动分析外也意味着可以捕获更低频的抖动因为捕获的整个波形周期更长,这也是示波器长存储的重要价值之一。

3 抖动测试的演进和新挑战

早年的经典抖动定义和分析分解方法在21世纪初基本已经确立,是通用串行电路分析的重要方法之一。但是随着数据速率的持续推高和电路复杂程度的加深比如链路宽度以及对均衡算法的应用等因素,特定标准的抖动定义和算法也在不断演进。

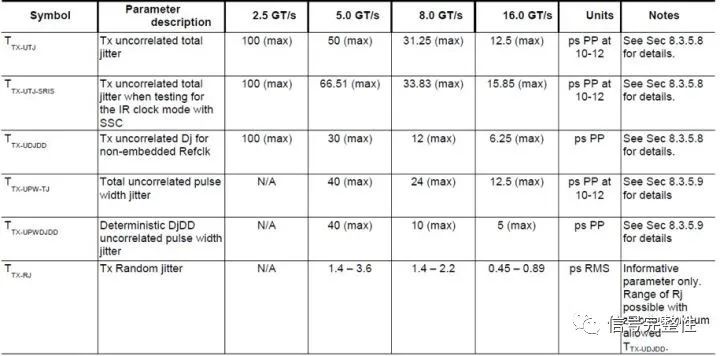

典型如PCIExpress3.0/4.0针对TX抖动测试重新进行了规划,定义TP1测试点(发送端芯片封装管脚处)抖动分为数据相关抖动和数据不相关成分。数据相关抖动成分主要源于封装损耗和反射等信号完整性效应。而数据不相关成分则源于PLL抖动,电源噪声和多链路之间串扰等。

PCIE4.0 Base规范里明确说明了之所以做如此分离的原因,因为这种分离与Tx和Rx均衡能力很好地匹配,Tx或Rx均衡不会减轻不相关的抖动成分,也无法通过均衡恢复水平时间窗口裕量即降低抖动或得到更加张开的水平眼图。重要的是,通过均衡可恢复的裕量(数据相关成分)不作为不可恢复的抖动计入预算。

从Tx测量中去除了数据相关的抖动,就可以分析剩余的抖动成分,计算剩余抖动成分的UTj和确定性抖动(双狄拉克模型)UDJDD分量。高频抖动(在通道中受到抖动放大)由分离的TTX-UPW-DJDD和TTX-UPW-TJ参数来解决。

图11 PCIE4.0 Base规范里描述的DDJ测量和定义

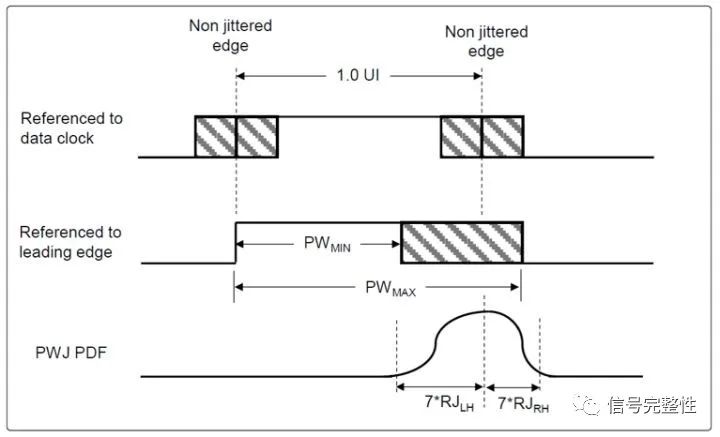

并引入了全新的PWJ,Pulse Width Jitter:

图 12 PCIE3.0/4.0引入PWJ

图13 PCIE4.0 Base规范定义的抖动测量项目

在PCIE4.0 Base规范中,最终定义了如上表的分析项目。可以看到,除了针对性的就DDJ专门做了定义并分离,针对Uncorrelated Jitter依然采用了前面描述的经典抖动分析和分解理论进行分析。关于最新的PCIE4.0标准中,针对抖动测量和分析的定义请参考PCIE4.0 Base规范,Ref [6]。

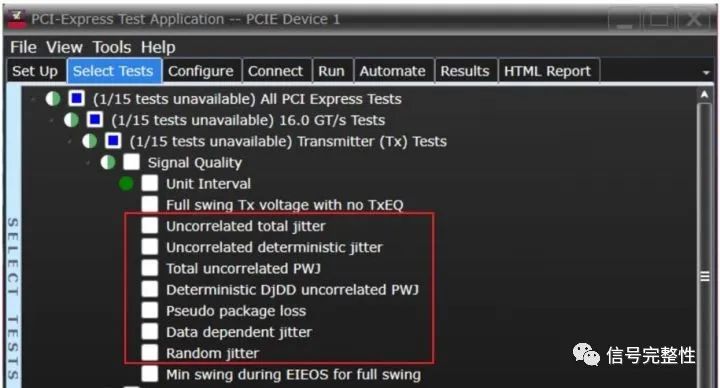

传统的抖动测试软件EZJIT作为通用抖动分析软件,没有按照PCI Express的新定义进行抖动分析和处理,因此如果需要进行完全符合PCI Express标准和规范的抖动分析就需要借助于实时示波器上的一致性测试软件如D9040PCIC测试软件,针对PCIE4.0 Base测试点有非常全面的抖动测试项目如下图示:

图14 Keysight D9040PCIC一致性测试软件测试项目

除了PCIE标准外,其它一些标准在抖动定义和测量分析方面也有很多发展和演进,比如USB3.x标准作为典型的接口一致性测试规定不同的测试码型,奈奎斯特码型CP1或者CP10用于RJ,PRBS码型CP0或CP9用于Tj测试,当然也需要一致性测试软件进行测试,具体不做更多举例。

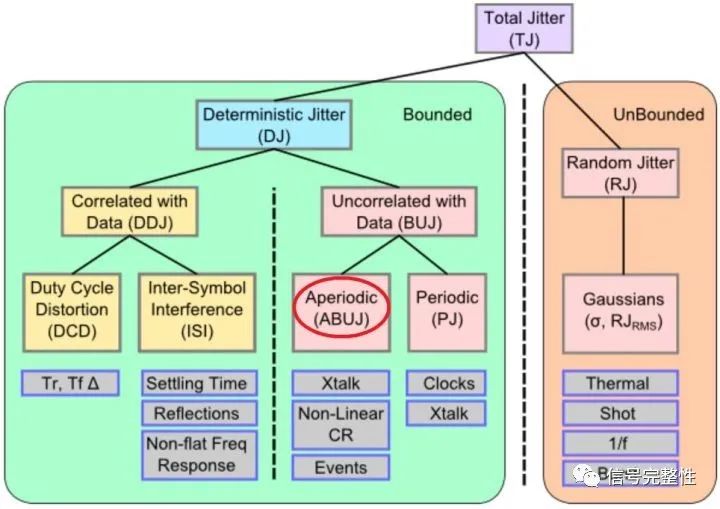

另外针对多链路传输如IEEE 802.3系列标准在实现200G/400G时,相对早期单链路串行总线的抖动定义和测量分析,必须考虑跨链路的数据串扰引起的抖动,如下图所示:

图15 更全面的抖动成分分解模型

这种串扰或者地弹等引起的抖动,呈现为非周期,有界和与数据无关的特性,因此命名为ABUJ(Aperiodic Bunded Uncorrelated Jitter )。

针对这一新的抖动成因,继续采用EZJIT Plus软件的频谱法分析时,会存在将这一由串扰引起的ABUJ归入RJ的风险,从而得到过大的RJ结果,最终导致过大的TJ结果,带来测量误差。

图16 数据中存在XTALK引起ABUJ抖动时频谱法分析RJ产生误差

如何解决这一新的问题和挑战呢?

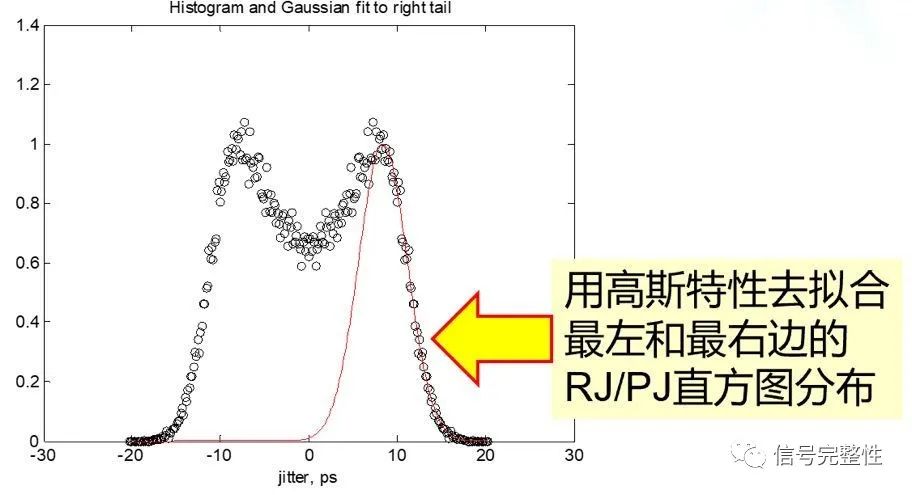

在EZJIT Plus软件里增加了Tail Fit方法进行RJ提取,如下图所示:

图17 EZJIT PLUS软件里增加Tail Fit法提取RJ

这一方法指的就是在实时示波器的抖动分析软件里采用双狄拉克模型法进行RJ提取:

图18 Tail Fit法RJ拟合示意图

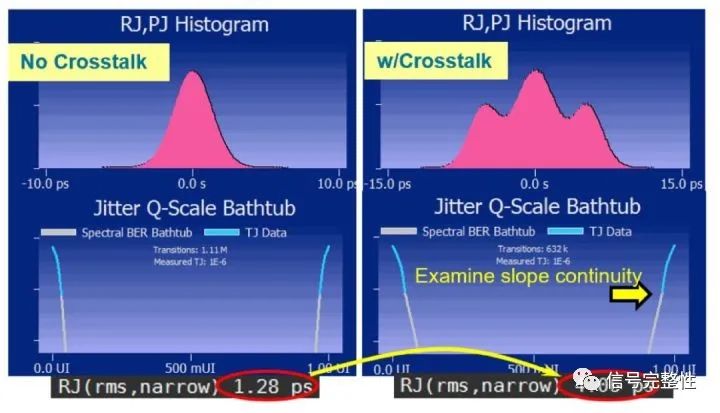

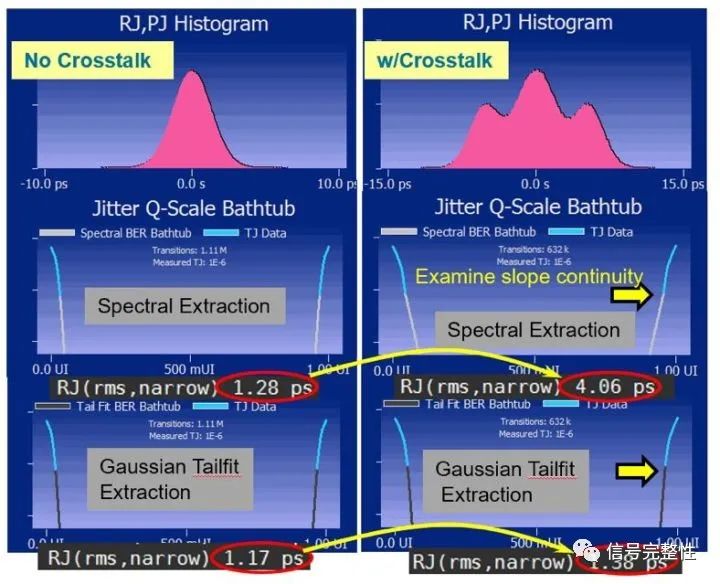

在以往未使用高斯拟合的原因是由于总直方图中的点稀缺,曲线拟合的点数仍然很少,它会给你带来不稳定的结果。下图显示了针对一个数据信号存在和不存在串扰情况下分别采用频谱法和高斯尾部拟合法对比的结果。

左边显示的是无串扰情况下分别采用频谱法和高斯法结果相近,右边显示在有串扰情况下,频谱方法得到的RJ明显偏大,采用高斯法后得到的RJ结果就显然回归正常。

图19 高斯法和Tail Fit两种方法分别对存在和不存在串扰引起的ABUJ分离差异对比

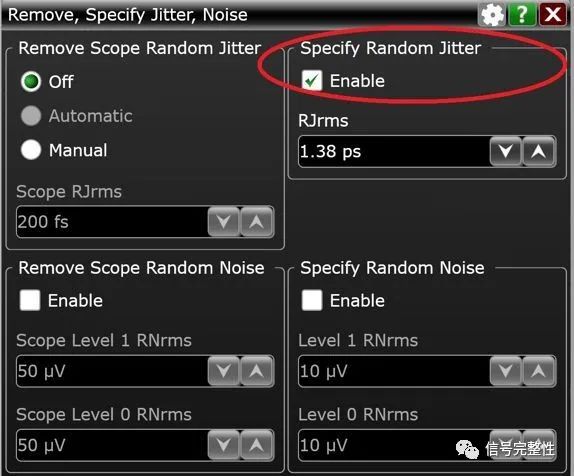

除了采用高斯尾部拟合法外,为了获得更高精度的测量,还可以先关闭相邻通道的串扰源,进行一次抖动测量并记录RJrms结果,打开串扰源,在下图中指定RJrms,然后再进行抖动测量,ABUJ就被归入有界抖动,不会被归入RJ成分并可准确得到,而TJ也可准确得到。

图20 EZJIT PLUS软件里手动去除RJ分析ABUJ示意图

近10年左右,除了在信号水平方向进行更加深入的抖动分析外,在信号的垂直方向进行噪声和干扰分析也慢慢开始兴起,但相比水平方向的抖动对眼图关闭和系统BER影响的理论比较成熟,业界在垂直方向噪声和干扰对垂直方向眼图闭合分析的理论依然在发展中。

垂直方向噪声和干扰对信号传输的影响的分析功能目前在Keysight采样示波器N1000系列的 N1010100A软件包和实时示波器的 EZJIT Complete 软件中均可支持:

图21 EZJIT软件3个等级提供强大的测量和分析能力

抖动测量和分析的理论将一直随着被研究的信号标准的发展而发展,因此其步伐也不会停止,因此本文所列演进和挑战也只能是略举一二例罢了。

4 影响抖动测试结果和精度的因素

抖动测量和分析在今天的串行数据电路设计和测试中的重要意义不言而喻,因此如何进行精确测量当然也成为每个工程师都关心的问题。

首先针对被测信号在示波器上要做出正确的测量设置。这些正确设置包括恰当的垂直刻度设置,通常建议信号在垂直刻度方向占满7格左右即用足垂直显示精度。

水平方向主要包括足够的采样率设置和存储深度,对实时采样示波器而言,采样率应当满足所用带宽的2.5倍以上。存储深度不足导致波形采集数据不足可能会导致实时示波器不能进行正确的时钟恢复。太长的存储深度则会导致数据波形过大,运算速度变慢。

因此建议按照规范或标准数据量捕获波形进行分析,比如部分标准或规范通常推荐1M UI进行分析,USB3.x和PCIE3.0即是如此,当然到PCIE4.0已经更改为2M UI。

对一般性串行数据抖动分析,应当达到100K UI量级数据以上。有时部分标准需要进行SSC(扩频时钟)测量,如果进行手动分析,建议根据需要测量的SSC周期数和所用采样率计算恰当的采样深度。

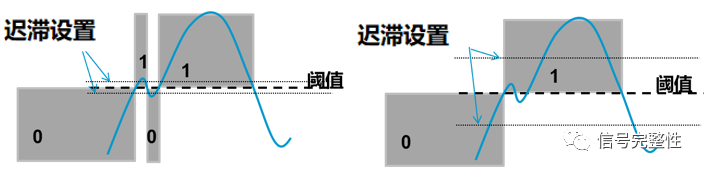

另外针对信号的阈值(Threshold)设置和迟滞(Hysteresis)设置也非常关键,通常建议设置信号幅度一半的电平为阈值,差分总线通常为0V。

针对一些有共模偏置的信号建议先手动测量信号幅度和共模电压以选取准确的阈值。准确迟滞设置也非常重要,因为可以避免示波器将信号边沿上的一些因为反射导致的不连续误判为ISI抖动的一个bit。

如下图示,左边设置的迟滞门限较低,因此会将波形上升沿上的一个回勾当作一个有效bit,显然这会被归入ISI抖动,右边迟滞设置电平门限拉高就会对这个回勾忽略不计。

图22 准确的迟滞设置避免将波形回勾计为一个bit的ISI抖动

如果想获得准确TIE测量结果,还有一个必须强调的是准确的遵循被测信号规范设置的时钟恢复算法,这是实时示波器进行抖动分析和分解的重要基础。相关信息请阅读各标准规范。

其它还包括在上期提到的关于EZJIT Plus如何进行抖动分解的一些设置,比如ISI滤波器的大小(Filter Size),Rj带宽等等。

总之,如果要进行一次准确的抖动分析和测量,涉及的知识非常广泛的,操作也略显繁琐。因此在对抖动测试不甚熟悉的情况下建议使用示波器上的抖动测试向导(Setup Wizard),抖动向导会对信号进行自动设置,包括信号刻度及阈值和迟滞等。建议安装Keysight实时示波器离线软件D9010BSEO进一步深入了解。

除了操作层面外,仪器的哪些指标对抖动测量的结果和精度会有比较大的影响呢?或者如何选择一个恰当的示波器完成预设的目标或工作呢?

首先是测量系统的恰当带宽。

测量系统带宽包括示波器和探头与电缆及夹具等连接部件等,如果不符合标准和规范要求,低于规范要求带宽则会带来信号输入链路额外的ISI抖动。

在今天已经普遍应用的针对电缆夹具和探头的去嵌技术如N2809A—Precision Probe和包含InfiniiSim的D9020ASIA分析套件也可以部分解决这些效应,当然也会带来额外的副作用即同步放大了仪器的本底噪声,必然带来额外误差。过高带宽也是不推荐的,因为会引入更多的高频带噪声。

其次实时示波器的采样率也会有影响。

通常更高采样率会有更高精度。显而易见,更高采样率会有更高的分辨率和边沿解析度,对最终的抖动分析结果会有影响。

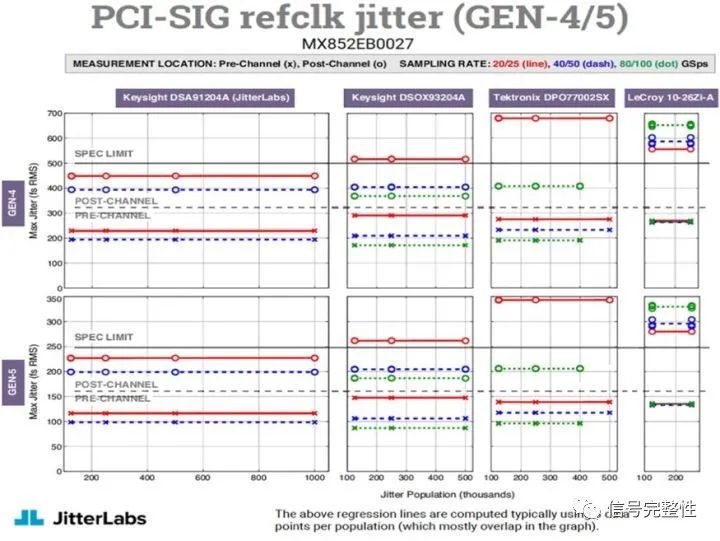

下图是源自第三方的Jitter Labs针对PCIE Gen4 /Gen5时钟测量结果对比,可以看到Keysight 90000A和90000X(当前替代型号是V系列)与T公司及L公司另两款产品测试结果对比。

红色为20/25GSa/s,蓝色为40G/50GSa/s,绿色为80/100GSa/s,Post-Channel和Pre-Channel指对PCIE Gen4/Gen5时钟测试的不同测试点位置。很明显在同型号产品上更高采样率得到的结果更好。K公司产品对比T/L产品相对结果明显更优,这又是什么原因呢?

图23 不同型号示波器不同采样率测试结果对比

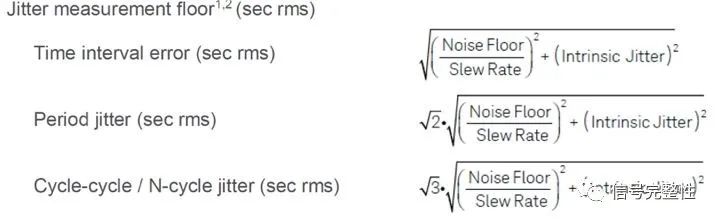

第三,仪器的本底噪声和固有抖动。

Keysight公司产品相比业界其它公司产品有更低的噪声本底和固有抖动,因此在上图Jitter Lab测量对比结果中显示出更高的精度。

一般实时示波器在采用频谱法进行抖动分析时都会采用功率谱密度积分得到RJrms值,频谱法进行功率谱积分时会将示波器的宽频本底噪声带入到RJ的分析结果中,带来更多的误差。而仪器的固有抖动也是误差之源,参考如下公式:

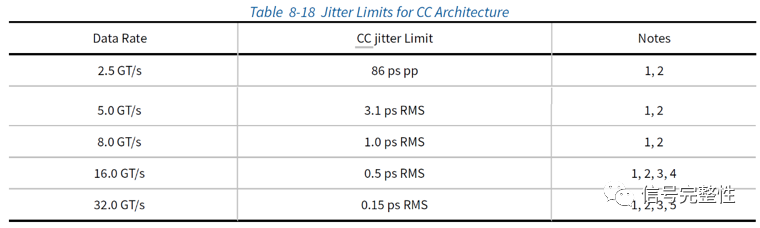

从公式中还可以看出噪声本底和信号本身的跳变斜率(Slew Rate)相关。在今天越来越低的信号幅度,越来越快的边沿,越来越低的裕量测试场景下,典型如PCIExpress规范里对CC CLK的CC Jitter描述,在32GT/s,CC Jitter Limits达0.15ps RMS,对实时示波器的测量精度提出了更高要求:

图24 PCIExpress5.0规范对CC Jitter Limit的要求

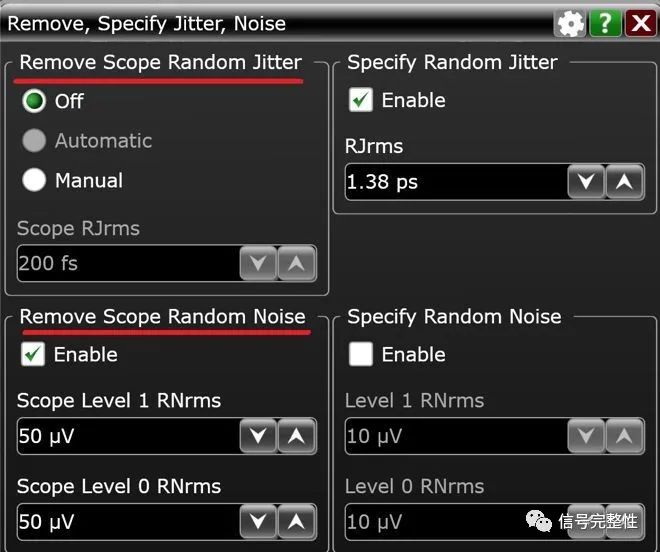

为了满足这些标准和规范的最新要求,业界除了在算法上做出一些改进和提高外,Keysight公司在EZJIT Plus/Complete软件里提供了去除示波器本身的随机抖动和噪声的选项,从而去除测量误差提高测量精度。

图25 EZJIT COMPLETE软件提供去除示波器随机抖动和噪声功能

另外捕获足够时长的波形用于数据分析也是抖动测试中的一个关键。

因为足够的波形数据和捕获时长除了可以捕获更多的时钟周期或数据UI进行更准确的抖动分析外也意味着可以捕获更低频的抖动因为捕获的整个波形周期更长,这也是示波器长存储的重要价值之一。

因此在选择和购买示波器的时候,推荐选择具有更长存储深度配置的产品。

以上谈到了实时示波器的4个影响抖动测量精度的主要因素或指标,虽然抖动软件的分析算法一直与时代同步进行提高和改进,但是在实际工作中尽量选择更高精度的设备依然是获得高精度的测量结果的最有力保障。

从抖动测试到相噪测试——实时示波器的新战场

实时示波器因为其高采样率下长存储和重复单次采样能力在抖动分析应用领域成为主力设备。随着数据速率的持续提高,裕量的下降,比如前面提到的PCIE5.0规范中关于CC Jitter 的要求,仅从时域角度进行测量已经显得捉衿见肘。

InfiniiVision 实时示波器 -

利用超快的波形捕获率执行一般性日常调试,更快地捕获毛刺信号

Infiniium 实时示波器 -

利用超高带宽、超低本底噪声和高 ENOB 的示波器,轻松获得开发下一代技术时所需的信号完整性

另一方面随着近几年实时示波器的ADC位数从8bit向10bit全面升级,实时示波器的无杂散动态范围(Spurious Free Dynamic Range)等指标得到了全面提高,典型如Keysight公司的 S和UXR系列实时示波器已经实现了从500MHz--8GHz和13--110GHz 硬件10bit ADC的全天候覆盖,其本身的SFDR指标均非常优异。因此实时示波器也开始进入频域指标测量领域,比如相位噪声,Phase Noise。

首先来看什么是相位噪声?

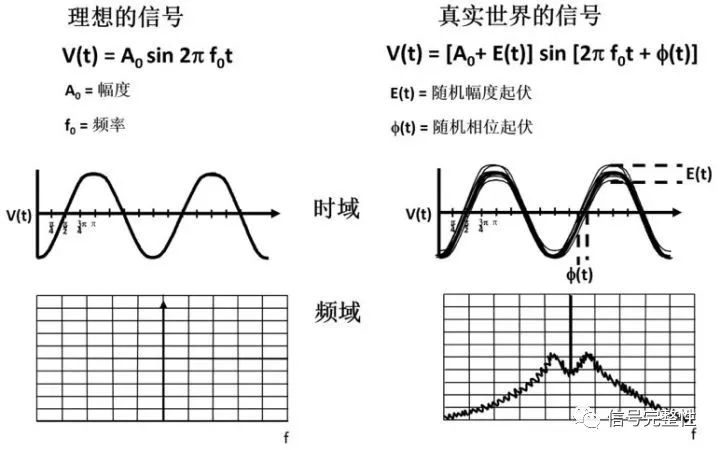

在维基百科中,相位噪声的定义是“时域不稳定性(抖动)导致波形在相位上发生快速、短期、随机的波动,这种波动在频域中的表现即为相位噪声”。这一术语中的“噪声”一词告诉我们,它指的不是杂散或确定性波动。

定义中提到的“短期”是为了与确定时钟源纯净度时所用的其他方法加以区别,例如以百万分之几(ppm)为单位的稳定度。它通常是以更大的时间长度进行测量,例如秒或分钟。

图26 理想与真实信号在时域和频域的对比

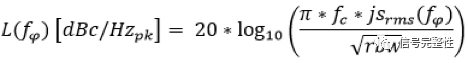

虽然有许多技术术语可以量化相位噪声,但最常采用的指标之一是“单边带(SSB)相位噪声”,L(f)。在数学上,美国国家标准与技术研究院(NIST)将L(f)定义为从载波的偏移频率处的功率密度与载波信号的总功率之比,单位为dBc/Hz:

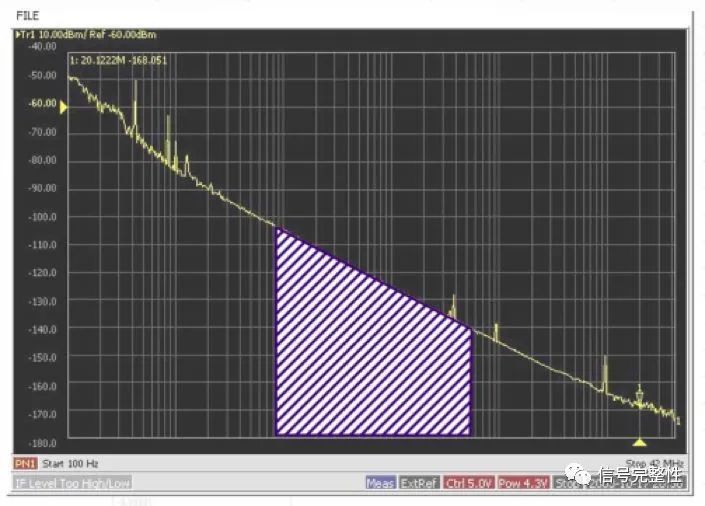

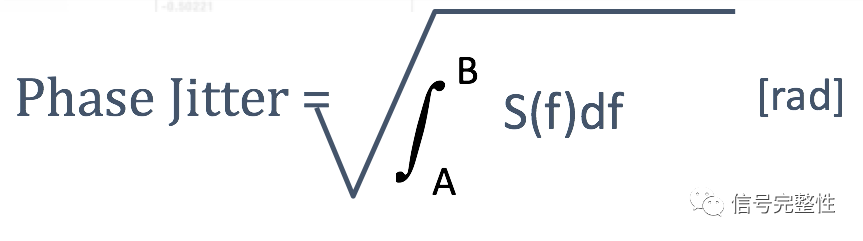

基于频域相噪的测量结果可以再转化为时域的相位抖动,这就是数字和时域研究人员感兴趣的结果。如下图示,相位抖动可以对阴影频带范围内相噪进行积分得到。

图27 基于相噪测量得到相位抖动

对于传统的数字领域的公司和工程师而言,如果为了测试相位噪声而专门进行相位噪声测量仪器的投资,很明显其性价比是不高的。因此发掘现有设备的潜能让其发挥更大作用,也是一个不错的选择,而普遍存在的实时示波器当然是最佳的选择。

相比其它频域仪器测量方法,采用实时示波器进行相噪分析的优点除了节约投资外主要还有实时示波器可以测量方波时钟信号或者带SSC(扩频时钟)的时钟信号相噪,尤其是SSC扩频时钟在高速串行数据标准如PCIExpress/USB等参考时钟信号里是相当常见的。

另外采用实时示波器的方法可以测量100MHz以上的时钟频率偏移,而频域仪器一般限定在100MHz范围内。针对数字域常见的差分信号,示波器可以采用高阻探头直接探测或者采用2个通道输入再进行差分运算,无需额外的附件Balun(巴伦)。

当然实时示波器还可以直接测量传递到数据信号上的相位噪声。实时示波器还有强大的数据存储和记录能力可以保存波形用于传统的数字分析工具比如PCIExpress 标准的CLK Jitter Tool等。

总而言之,采用实时示波器进行相位噪声的分析和测试,不仅可以发挥实时示波器的作用节约投资,而且针对频域测量仪器在数字标准和信号上的不足提供了更多优点:

支持更广泛信号类型

更广泛的时钟信号如方波、带SSC时钟、数据信号

更简便丰富的连接方式无需Balun以及探头

更轻松的电缆接入

更大的频率偏移支持能力

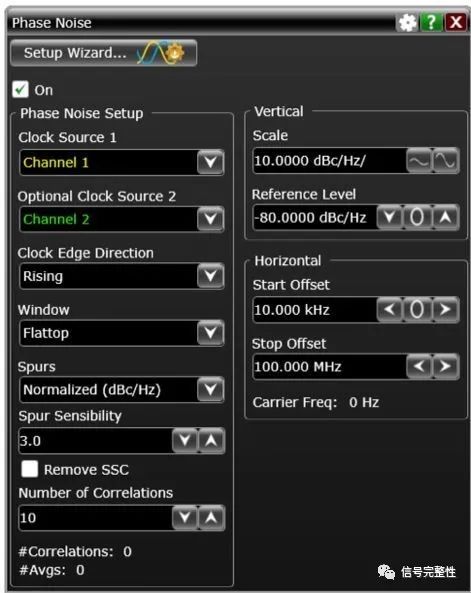

……Keysight公司在2018年推出了基于Infinium系列实时示波器的D9010/D9020JITA抖动/噪声/相噪分析软件,除了包含EZJIT Complete的全部功能外,还提供了功能强大的相噪测试功能:

将单边带(SSB)相位噪声绘制为对数频率与dBc / Hz

使用2个通道和交叉相关来降低宽带测量噪声

通过降低宽带测量噪声来测量差分时钟的相位噪声

测量带扩频调制(SSC)时钟的相位噪声

减少交叉相关时间间隔误差(TIE)测量中的宽带噪声(RJ)

在相位噪声图上测量两个频率之间的积分抖动

使用InfiniiMax探头测量电路中的时钟/数据相位噪声

图28 D9010/D9020 JITA软件相噪测试设置

图29 D9010/9020 JITA 单边带相位(SSB)噪声测量结果

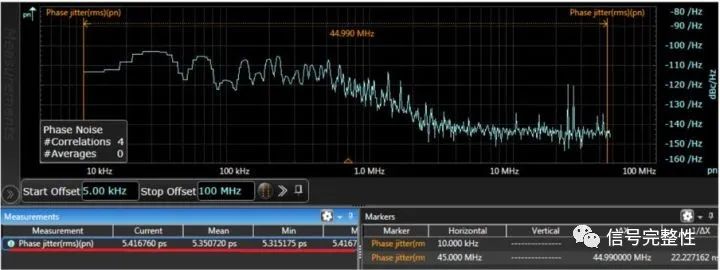

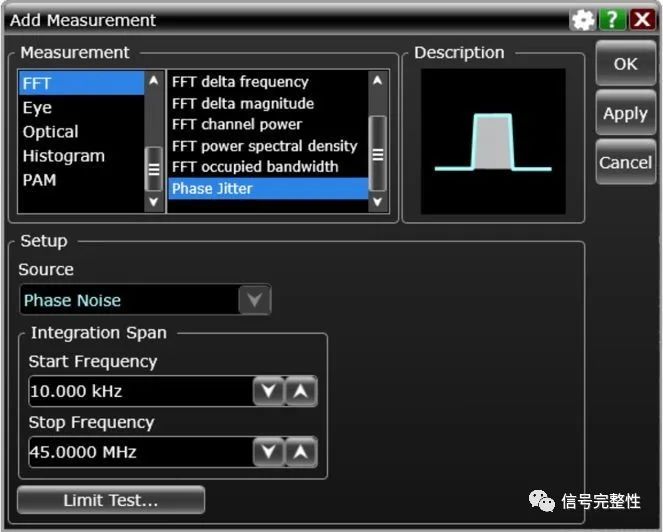

基于相噪测量结果,然后在测量菜单下选择FFT →Phase Jitter项目,参照下图,选择感兴趣的频带,就可以得到Phase Jitter测量结果,如下图示:

图30 基于相噪测试结果的相位抖动测量

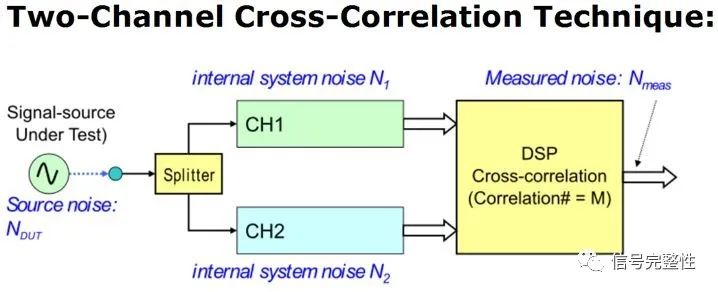

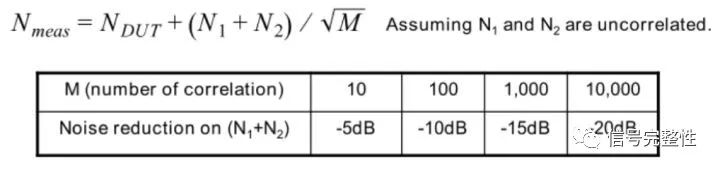

为了获得更精确的测量结果,相噪测试时还可以进行2-通道互相关降低仪器本底噪声。时钟信号通过功分分成两个信号输入到示波器的两个通道,可以执行双通道互相关技术。

时钟信号可以是单端或差分(如果差分信号则建议分别针对正负信号经过功分后用SMA电缆接入1-3或2-4通道)。然后在通道上执行互相关操作,如下图30所示。

通过每个通道的DUT噪声是相干的并且不受互相关的影响,而每个通道产生的内部噪声是不相干的,并且以或者的速率通过互相关运算减少,其中M是进行波形相关运算的采集数量,采用的波形相关运算数量越大则进行平均运算时的速度越慢。

图31 双通道互相关降低仪器本底噪声示意

图32 相关运算数量和降低噪声性能对应关系

相噪测试为实时示波器进入频域测量打开了另一扇窗户,尤其是针对数字和时域信号日益增长的频域测试需求。

审核编辑:汤梓红

-

示波器

+关注

关注

113文章

6240浏览量

184792 -

抖动

+关注

关注

1文章

69浏览量

18860 -

眼图

+关注

关注

1文章

67浏览量

21124

原文标题:抖动与抖动测试

文章出处:【微信号:SI_PI_EMC,微信公众号:信号完整性】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

抖动的知识及测量方法

抖动测量三种方法

从抖动分析到相噪分析

如何对C-RAN组网时的CPRI时延抖动进行测试?

MIPS平台上运动控制器的调度抖动的测试方法设计详解

抖动测试和分析的基本方法和经典理论

抖动测试和分析的基本方法和经典理论

评论