一、对于一个部件,比如射频功放,供电是直流48V,其他的接口都是信号的输入/输出/控制等,像这类的部件需要单独进行EMC要求吗,如果要测试EMC,一般测哪些项,需要放在整机上测试吗?

答:如果能自成系统,有封闭的外壳,独立完成功能,就需要测试EMC;48VDC输入,一般要测试CE;正常应用,如果手能接触到,需要测试ESD;射频功放看应用到什么领域,每个领域有对应标准; 比如:信息技术类设备,需要测试RE、CE、ESD、RS、EFT、SURGE、CS、PMS、DIP;军用设备,需要按照GJB151B-2013对应领域,有不同测试项目,常规RE102、CE102、CS112、CS114、CS115、CS116、RS103;

二、一款控制器,除了电源和CAN通讯模块其余全是信号采集,工作电流100mA,在做传导发射电流法时总是超标,当控制器不接地时发射有显著改善,这种情况作何解释?(在控制器接地时,电流钳只夹电源线时是不超标的。)

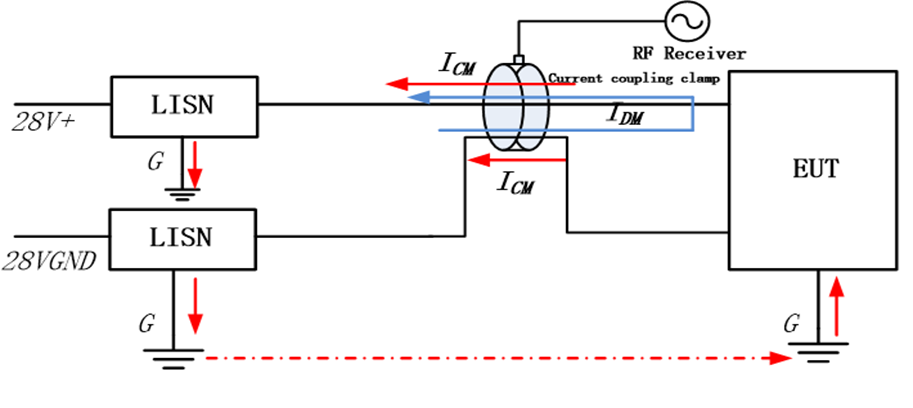

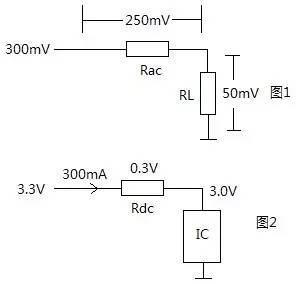

答:传导电流法测试不接地时候显著改善这种情况我们也经常碰到,因为驱动超标的是共模电流源,产品不接地后电流的回路阻抗变大了,但如果激励源电压还是一样时候,按最简单的电路算法,回路电流自然会变小,如下图所示。但是通常噪声也不会全部消失,因为就高频而言,EUT对地还是有分布电容寄生参数的。

只测试电源线不超,说明主要的问题可能在信号采集线或者CAN上,一般来说,控制器产品信号线电流法会PCB内的开关电源噪声最为敏感,耦合到信号线上的方式以传导为主,特别是电源地噪声。最好的处理方式就是在靠近接口连接器的位置增加滤波电路。

三、在EFT整改中,通常在注入端口的线上套磁环:

1)请问磁环的选型有哪些注意事项?

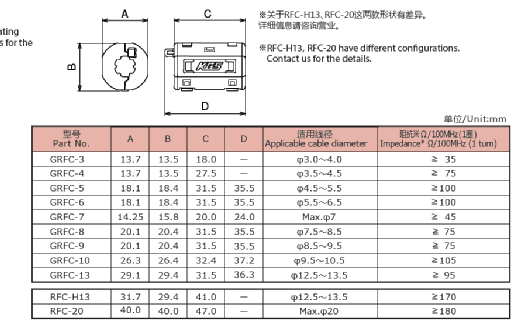

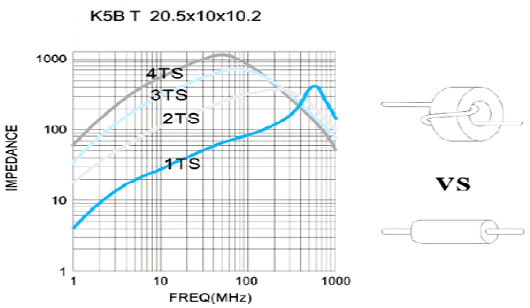

答:磁环磁芯材料选型需要依据前面我们在部分学员的问题答疑中给出的内容来判断。EFT干扰的频谱特征比较宽,但主要能量频谱都集中在几十M以下,因此你需要选择在这个频率段有比较好阻抗性能的磁芯。

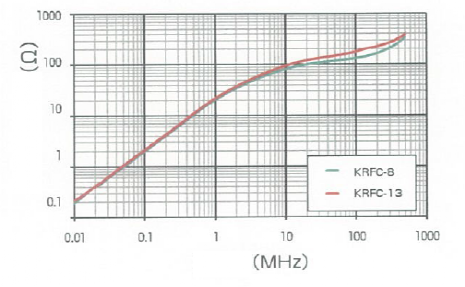

但是这个频率段比较尴尬,其实锰锌材质也行,镍锌材质也可以,也可以是别的复合材质,如果厂家能给出下面类似的表格或图形,选择起来可能就容易多了。

2)是直接套的效果好,还是将线在磁环上饶几圈的效果好?

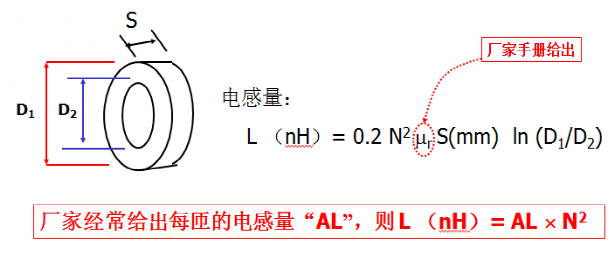

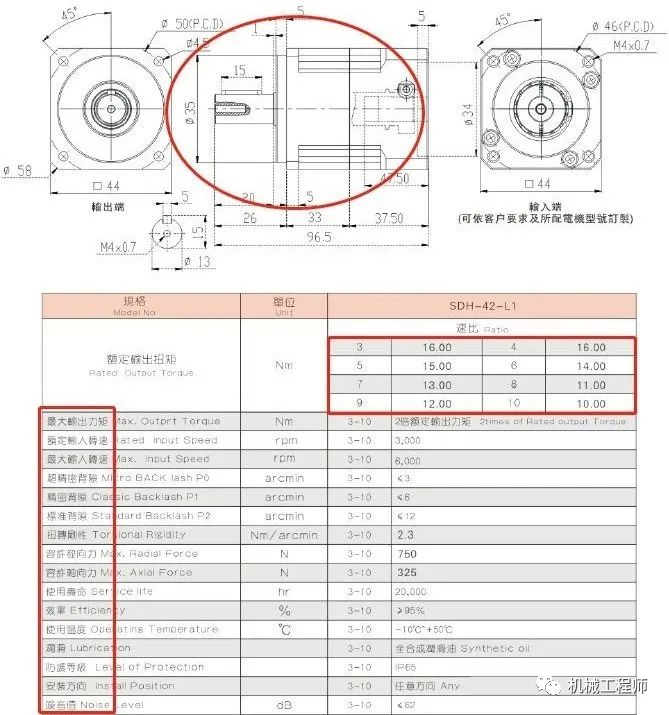

肯定是要套几圈的,用磁环不饶几圈就是对滤波资源的变相浪费。下图两幅图中,第一个图形给出了磁环绕圈获得阻抗值的计算方法,显然增加圈数,磁环阻抗是以平方单位增加的;此外阻抗还和磁环的尺寸有关,也就变相回答了上面的问题,选型除了材料因素外,磁环尽可能选大个的。第二个图形则直观的告诉你圈数和阻抗的关系,注意饶制过于密集时,会因为分布参数(线间寄生电容)的原因,高频阻抗下降。

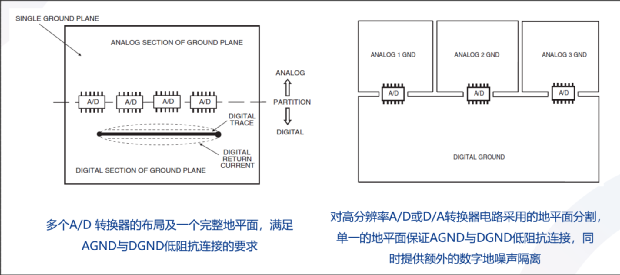

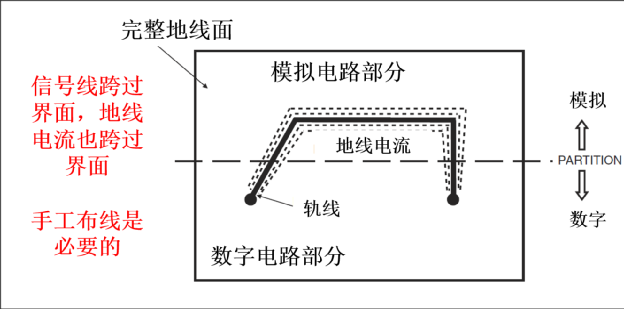

四、数字地和vwin 地:A/D芯片【放在完整平面】和【又要同时放在两端】怎么理解?

答:第一幅图讲的是,如果在PCB布局布线设计时,Layout工程师如果能做到模拟区域和数字区域的严格区分(含器件布局和PCB走线),依据高速信号电流的镜像回路理论,数字电路的回流电流就不会耦合如模拟区域的地平面上,此时我们可以PCB板不做数字地与模拟地的物理分割,而是采用完整的GND平面设计方式;

第二幅图讲的是,如果是某些高敏感度的模拟信号处理,AD芯片的信号分类也非常清晰,那么此时就可以采用单点连接的地分割设计方案,PCB汇接点可以设计在芯片附近区域。

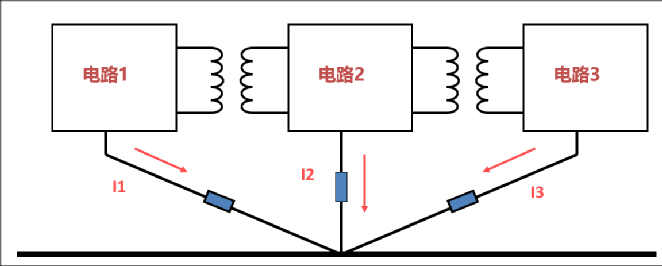

五、数字电路和功率地:功率电路和MOS管脚在GND地采取单点连接。这种情况不会出现共地阻抗干扰的情况么,理由是?

答:单点连接的原理如下图所示,我们说过电流一定要走loop形式构成环路才能符合我们说的电路电流基本定律,两个电路之间只有一个共地点,那么也就是公共电位参考点,因此就不会互相构成影响。

审核编辑:汤梓红

-

控制器

+关注

关注

112文章

16332浏览量

177795 -

emc

+关注

关注

170文章

3914浏览量

183116 -

MOS

+关注

关注

32文章

1269浏览量

93675 -

磁环

+关注

关注

3文章

159浏览量

21755

原文标题:EMC工程问题解答(四)

文章出处:【微信号:EMCjishufuwu,微信公众号:深圳市赛盛技术有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

磁环的选型有哪些注意事项

磁环的选型有哪些注意事项

评论