异步计数器是那些输出不受时钟信号影响的计数器。由于异步计数器中的触发器提供有不同的时钟信号,因此在产生输出时可能会有延迟。设计异步计数器所需的逻辑门数量非常少,所以它们的设计很简单。异步计数器的另一个名称是“波纹计数器”。

异步计数器中使用的触发器数量取决于计数器的状态数量(例如Mod 4、Mod 2等)。计数器的输出状态数称为计数器的“模数”或“MOD”。计数器可以拥有的最大状态数为2n,其中n表示计数器中使用的触发器数量。例如,如果有2个触发器,则计数器的最大输出数为4,即 2*2。因此,它被称为“MOD-4计数器”或“模数4计数器”。

主要类型

4 位异步UP计数器

4位异步DOWN计数器

4位异步UP/DOWN计数器

1、异步4位UP计数器

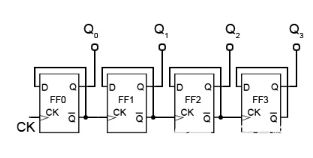

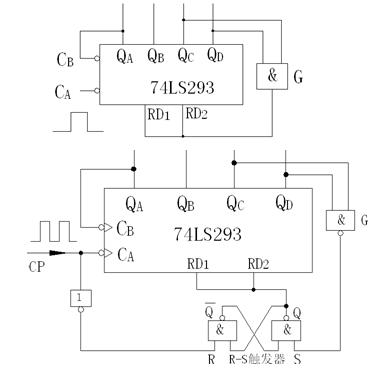

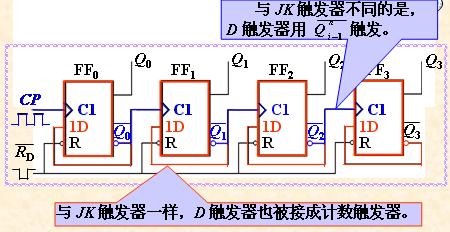

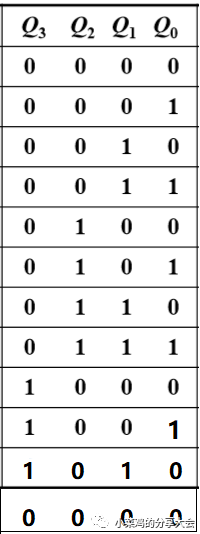

带D触发器的4位异步UP计数器如下图所示,它能够计数从0到15的数字。所有触发器的时钟输入级联,每个触发器的D输入(DATA输入)连接到触发器的状态输出。

这意味着触发器将在时钟信号的每个有效边沿或上升沿触发。时钟输入连接到第一个触发器,而计数器中的其他触发器接收从前一个触发器的 Q' 输出输入的时钟信号。当时钟信号出现上升沿时,第一个触发器的输出将发生变化。

在异步4位UP计数器中,触发器以切换模式连接,因此当时钟输入连接到第一个触发器FF0时,其在一个时钟脉冲后的输出将变为20。

每个触发器的Q输出的上升沿触发其下一个触发器的时钟输入,它将下一个时钟频率触发到其应用输入的一半,每个触发器(Q0、Q1、Q2、Q3)的Q输出表示 4 位UP计数器的计数,例如20 (1) 到23 (8)。

工作原理如下:

现在假设触发器的4个Q输出最初为0000。当时钟脉冲的上升沿施加到FF0时,输出Q0将变为逻辑1,下一个时钟脉冲将Q0输出变为逻辑0。这意味着时钟脉冲的输出状态在一个周期内切换(从0变为1)。

由于FF0的Q'连接到FF1的时钟输入,那么第二个触发器的时钟输入将变为1。这使得FF1的输出为高电平(即Q1=1),表示值为20。这样下一个时钟脉冲将使Q0再次变高。

所以现在Q0和Q1都为高,这导致4位输出11002。现在如果应用第四个时钟脉冲,它将使Q0和Q1变为低状态并切换FF2。因此输出Q2将变为00102。由于该电路是4位向上计数器,因此输出是从0、1、2、3….15即00002到11112(0到1510)的二进制值序列。

例如,如果当前计数=3,则递增计数器将计算下一次计数为4。

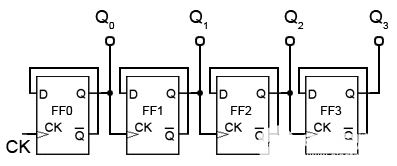

2、异步4位DOWN计数器

下图显示了一个4位异步DOWN计数器。这是对UP计数器的简单修改。4位向下计数器将从15到0向下计数。所有触发器的时钟输入级联,每个触发器的D输入(DATA输入)连接到逻辑1。

这意味着触发器将在时钟信号的每个有效边沿(正边沿)处切换。时钟输入连接到第一个触发器。计数器中的其他触发器接收来自前一个触发器的Q输出而不是Q' 输出的时钟信号。

这里Q0、Q1、Q2、Q3代表4位递减计数器的计数。当时钟信号的上升沿出现时,第一个触发器的输出将发生变化。例如,如果当前计数=3,则向上计数器将计算下一个计数为2。输入时钟将导致下一个触发器的输出(计数)发生变化。

异步递减计数器的操作与异步递加计数器的操作完全相反。在这里,输入端的每个时钟脉冲都会减少单个触发器的计数。因此,递减计数器从15、14、13…0计数,即(0到1510)或11112到00002。

另外,UP/DOWN计数器都是使用异步设计的,基于时钟信号,目前还没有广泛的使用,因为它们在高时钟速度下并不可靠。

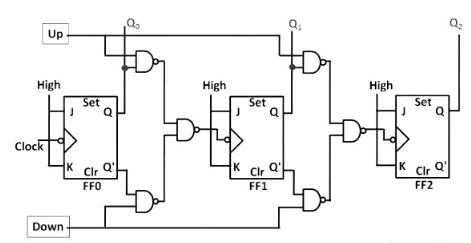

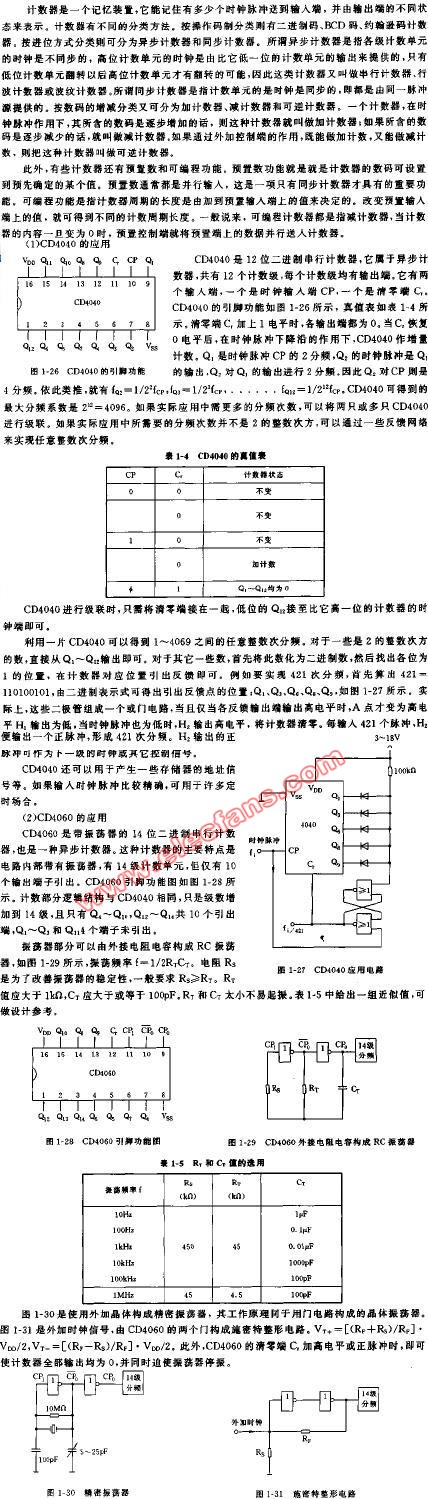

异步3位UP/DOWN计数器

通过将UP计数器和DOWN计数器的概念相加,便可以设计出异步3位UP/DOWN计数器。3位异步加/减计数器如下所示。

它可以根据时钟信号输入以任何一种方式计数,从上到下或从下到上。

向上计数;如果UP输入和DOWN输入分别为1和0,则第一个触发器到第三个触发器之间的NAND门会将FF0的非反相输出传递到FF1的时钟输入。类似地,FF1的Q输出将传递到FF2的时钟输入。因此向上 / 向下计数器执行向上计数。

向下计数;如果DOWN输入和UP输入分别为1和0,则第一个触发器到第三个触发器之间的NAND门会将FF0的反相输出传递到FF1的时钟输入。同样,FF1的Q输出将通过FF2的时钟输入。因此UP/DOWN计数器执行向下计数。

UP/DOWN计数器比UP计数器或DOWN计数器慢,因为加法传播延迟将添加到NAND门网络。

关于时钟纹波

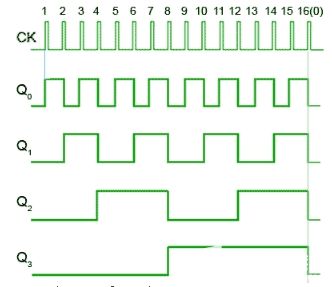

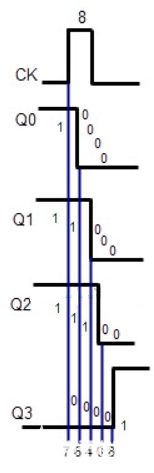

驱动电路的各个时钟脉冲的时间延迟之和称为“时钟纹波”,下图可以清楚的解释逻辑门如何在每个触发器中产生传播延迟。

逻辑门的传播延迟用蓝线表示,它们中的每一个都会增加下一个触发器的延迟,所有这些单独的触发器的总和称为电路的传播延迟。

由于所有触发器的输出以不同的时间间隔变化,并且对于时钟信号的每个不同输入,每次输出都会出现一个新值。例如,在时钟脉冲8处,输出应从11102 (710) 变为00012 (810),时间延迟为400到700ns(纳秒)。

对于8个以外的时钟脉冲,序列将发生变化。虽然该瓶颈问题阻碍了该电路用作可靠的计数器,但它作为简单有效的分频器仍然很有价值,其中高频振荡器提供输入,链中的每个触发器将频率除以2。

主要优点

异步计数器可以很容易地用T触发器或D触发器设计。

异步计数器也称为纹波计数器,用于低速电路。

它们用作除以N计数器,将输入除以N,其中N是整数。

异步计数器也用作截断计数器。这些可用于设计任何Mod编号计数器,即偶数Mod(例如:Mod4)或奇数Mod(例如:Mod3)。

主要缺点

有时“重新同步”可能需要额外的触发器。

要计算截断计数器的序列(Mod不等于2n),可能需要额外的反馈逻辑。

在计数大量位时,异步计数器的传播延迟非常大。

对于高时钟频率,由于传播延迟,可能会出现计数错误。

主要应用

异步计数器用作分频器,用作除以N的计数器。

用于低功率应用和低噪声发射。

用于设计异步十进制计数器。

用于环形计数器和约翰逊计数器。

异步计数器用于Mod N纹波计数器。例如Mod 3、Mod 4、Mod 8、Mod 14、Mod 10等。

总结

简单来说,异步计数器可以说成是异步时序电路,其主要特点是每个触发器的时钟脉冲端CP不全都连接在一起,所以触发器的翻转时刻有先有后,其输出可能会产生干扰延迟现象,但其电路结构设计相对简单。

-

触发器

+关注

关注

14文章

2000浏览量

61129 -

异步计数器

+关注

关注

0文章

10浏览量

8038

发布评论请先 登录

相关推荐

基于Multisim的计数器设计仿真

同步计数器和异步计数器是什么 同步计数器和异步计数器的主要区别?

异步计数器的主要类型

异步计数器的主要类型

评论