本文主要阐述了SLM21364的过流保护触发电路的工作原理,以及RCIN管脚外接电阻电容的选择。

过流保护工作原理

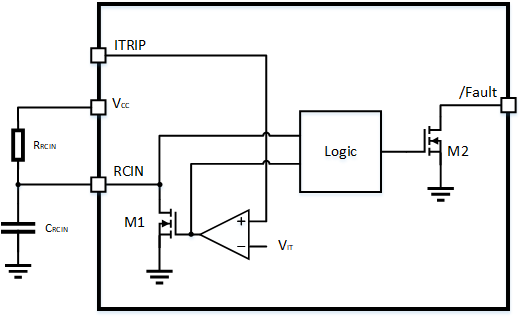

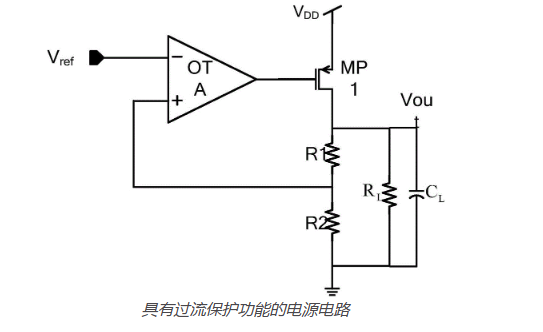

SLM21364通过外部电流检测电阻和ITRP管脚的监控实现系统过流检测和保护功能。图1是SLM21364的过流保护触发电路的典型应用和内部框图。

图1. RCIN管脚应用及内部逻辑图

RCIN管脚外接电阻RRCIN和电容CRCIN,当ITRIP管脚电压大于VIT时,Fault管脚输出为低,此时,RCIN管脚的内部下拉MOSFET(M1)导通,迅速拉低RCIN电压,释放CRCIN的电荷,拉低时间为TRCIN_F。当ITRIP管脚电压小于VIT时,RCIN的内部下拉MOSFET关断, RCIN管脚呈现高阻状态,Vcc电源通过RRCIN对CRCIN充电,当RCIN管脚电压上升到阈值电压(通常为8V)后Fault管脚输出置高恢复, 其中RCIN管脚电压开始充电到Fault管脚置高恢复的时间为TFLTCLR。

RCIN管脚充放电时间

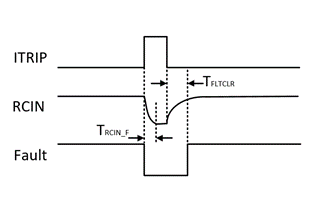

为了正常配置Fault的恢复时间,RCIN在ITRIP管脚开始充电的时刻必须为零电平,需要在ITRIP由高变低前迅速拉低RCIN电平,由图2所示,RCIN的拉低时间为TRCIN_F, 主要由内部下拉MOSFET(M1)的输出电流决定。

图2. RCIN,ITRIP和Fault管脚的时序逻辑

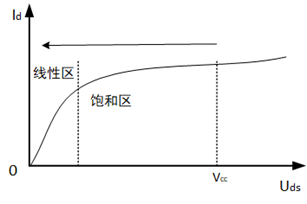

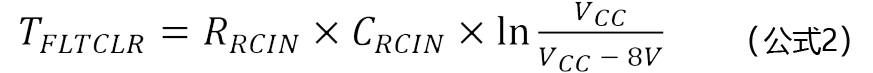

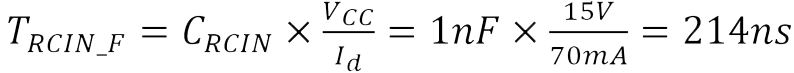

根据电容放电公式,,近似得到:

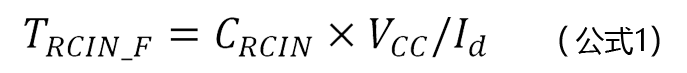

图3是RCIN下拉MOSFET(M1)的输出特性曲线,当M1的Drain和Source两端电压Uds比较高时,下拉电流Id呈现电流源特性,主要工作在饱和区。Id电流的大小主要由内部门级电压决定。针对SLM21364的内部设计,M1的饱和电流约为70mA。在Vcc和Id确定的情况下,为了保证RCIN管脚每次正常拉低到零电平, TRCIN_F需小于1μs,则实际应用中应保证CRCIN<2.2nF。

图3. RCIN下拉MOSFET(M1)的输出特性曲线

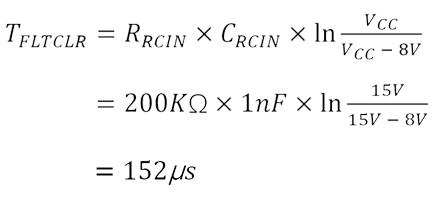

确定CRCIN的大小之后,可以根据Fault管脚置高恢复时间TFLTCLR的需求来选择合适的RRCIN。TFLTCLR的时间是由RCIN管脚的充电时间决定,并由以下公式计算:

实验测试结果

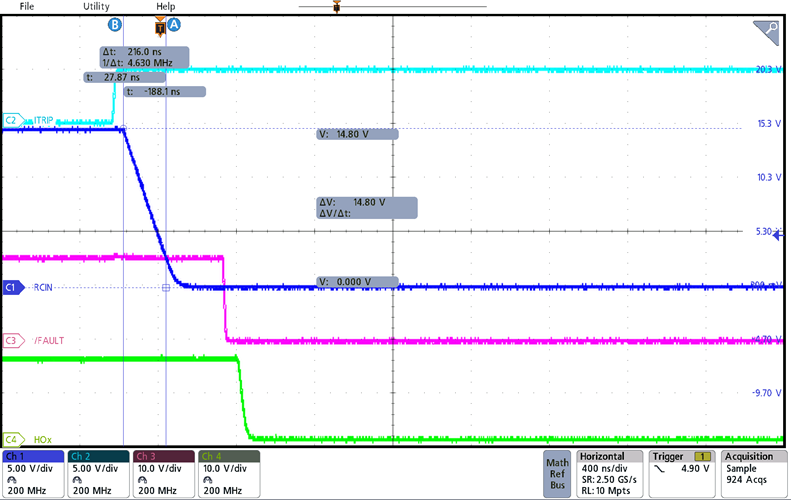

当Vcc=15V,选取RRCIN=200KΩ, CRCIN=1nF, 测得RCIN放电实验波形如图4所示:

CH1: VRCIN, CH2: VITRIP,CH3: VFAULT, CH4: HO

图4. RCIN放电实验波形

Vcc=15V,RRCIN=200KΩ, CRCIN=1nF

由公式1计算可得RCIN的拉低时间为:

和图4中测得RCIN的拉低时间216ns是一致的。

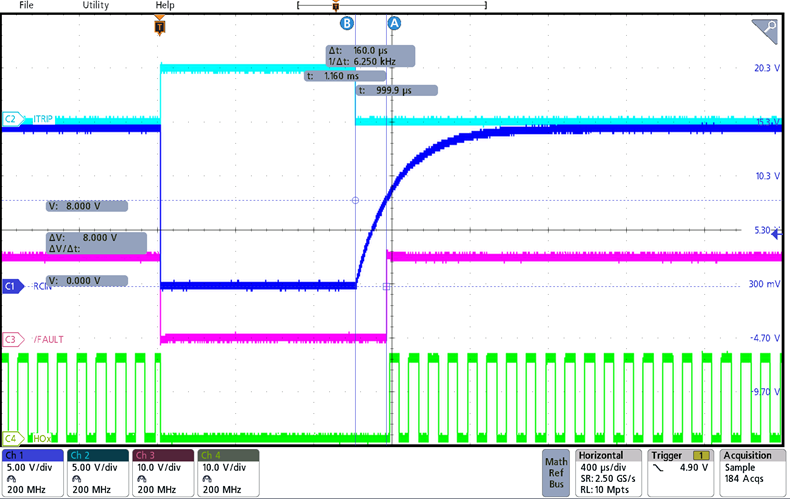

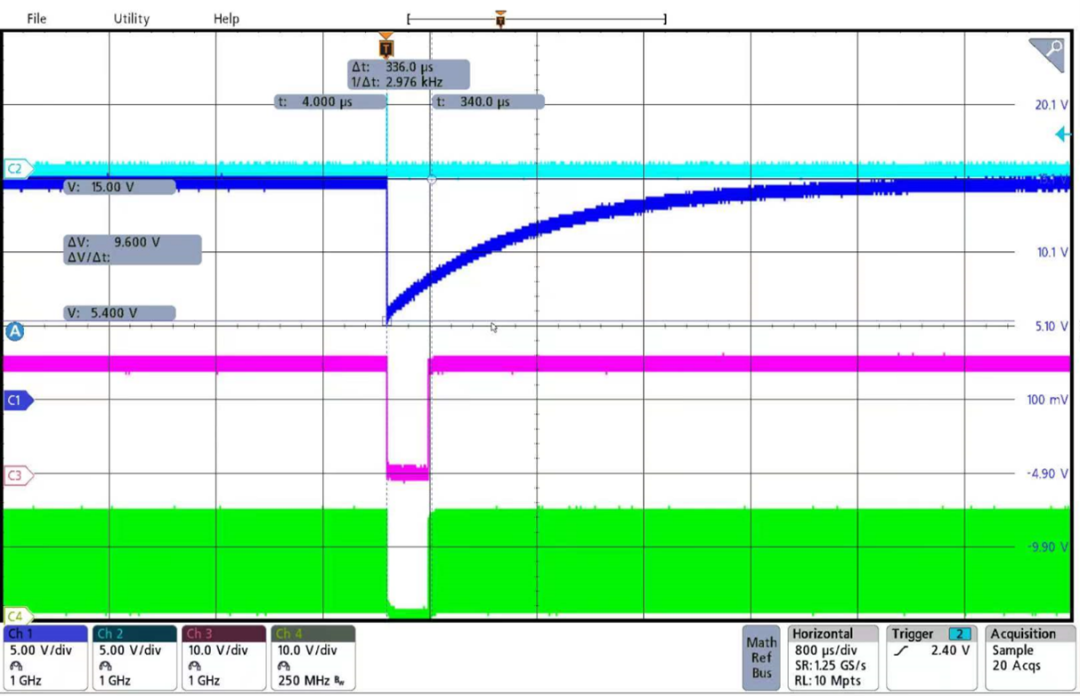

上述实例相同条件下, 测得RCIN充电实验波形如图5所示:

CH1: VRCIN, CH2: VITRIP, CH3: VFAULT, CH4: HO

图5. RCIN充电实验波形

Vcc=15V,RRCIN=200KΩ, CRCIN=1nF

由公式2计算可得:

和图5中测得的FAULT管脚置高恢复时间160μs是一致的。

当Vcc=15V,选取RRCIN=200KΩ, CRCIN=10nF, 测得RCIN放电实验波形如图6所示:

CH1: VRCIN, CH2: VITRIP, CH3: VFAULT, CH4: HO

图6. RCIN充放电实验波形

Vcc=15V,RRCIN=200KΩ, CRCIN=10nF

由于CRCIN取值较大,RCIN管脚在ITRIP触发后下拉速度较慢,且RCIN过流信号维持时间较短,从图中看到RCIN电压并不能完全拉低到零电平就开始充电。这样会导致Fault管脚的恢复时间远远小于设置的时间,带来系统保护风险。如果CRCIN取值过大,或者ITRIP维持时间过小,甚至会出现保护失效的极端现象。

总结

SLM21364的RCIN外接RC电路主要用来配置系统过流保护后的FAULT恢复时间,为了正常配置FAULT恢复时间,需要保证RCIN在RC充电前即过流ITRIP信号下降前下拉到零电平。对于一般的电源系统,过流持续时间在几十μs以下的应用,建议RCIN的放电电容CRCIN<2.2nF,典型值选取1nF。然后再根据FAULT恢复时间需求,确定RCIN的充电电阻RRCIN的大小。

审核编辑:汤梓红

-

过流保护

+关注

关注

10文章

236浏览量

32042 -

触发电路

+关注

关注

4文章

118浏览量

28271 -

RC电路

+关注

关注

2文章

162浏览量

30245

原文标题:应用笔记 丨SLM21364的RCIN管脚外接RC电路的选择

文章出处:【微信号:数明半导体,微信公众号:数明半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SLM21364的过流保护触发电路的工作原理

SLM21364的过流保护触发电路的工作原理

评论