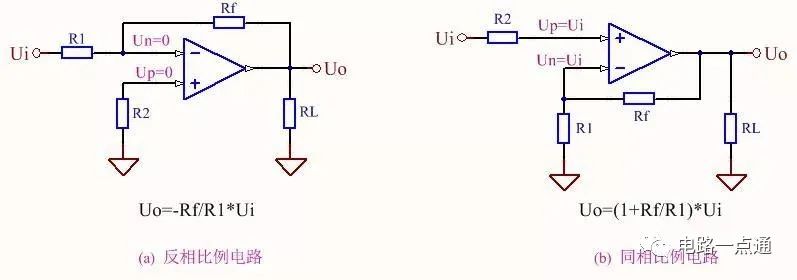

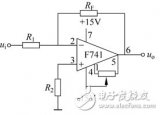

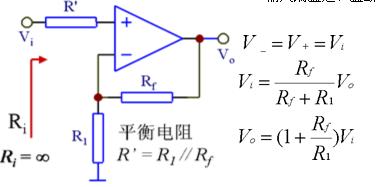

实际应用中,常要获取两个信号的差值或对多个vwin 信号进行叠加混合,这时就要使用信号叠加电路和求差电路。图一所示的反相比例和同相比例电路是比例运算电路的基本拓扑结构,以此为基础,利用叠加原理和戴维南定理就可以构造出信号叠加电路和求差电路。

图一 比例运算电路基本拓扑结构

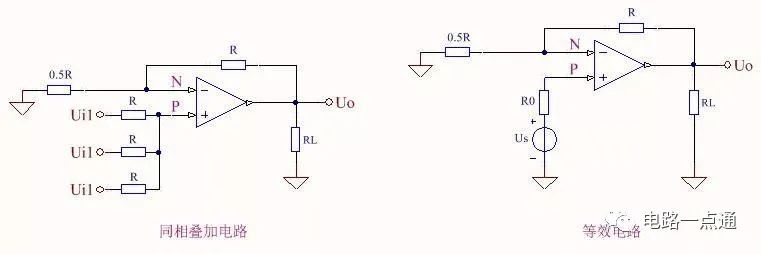

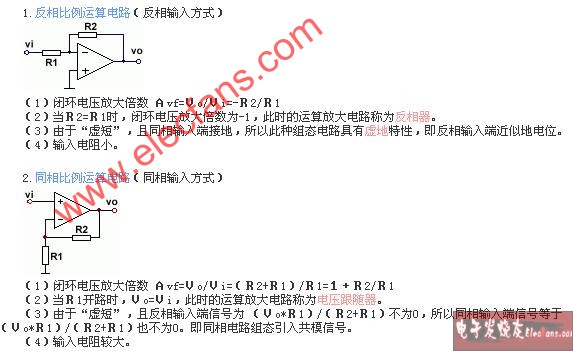

一. 信号叠加分同相叠加和反相叠加,图二为信号同相叠加电路,其戴维南等效电路如图二右侧所示。

图二 同相叠加及其等效电路

从图二可看出,等效电路就是图一(b)所示的基本同相比例电路,利用叠加原理得P点开路电压 Us=1/3(Ui1+Ui2+Ui3),电压源等效内阻R0=R//R//R;直接套用基本同相比例电路的公式,可得:

Uo=(1+R/0.5R)*Us=Ui1+Ui2+Ui3 , 输出为三个输入信号的同相叠加。

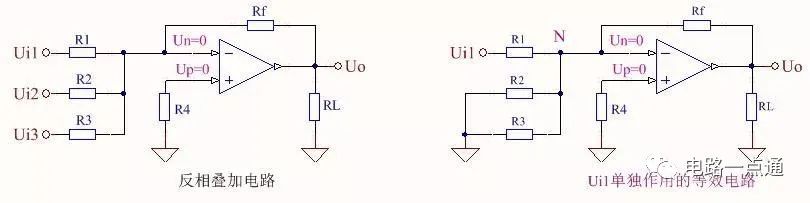

图三 反相叠加与等效电路

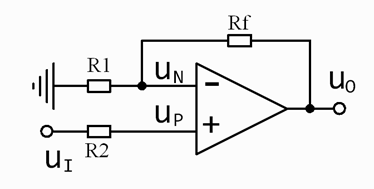

图三为信号反相叠加电路,其输出等于各个输入信号单独作用时的输出之和,当Ui1单独作用时,将Ui2、Ui3对地短路,此时的等效电路 如图三右侧所示。因同相端接地,反相端为虚地点,即N点为零电位,R2、R3上没有电流,可以认为R2、R3 存在与否对电路无影响,即可以拿掉,等效电路就和图一(a)的基本反相比例电路相同,直接套用反相比例电路公式,得Ui1单独作用时的输出:Uo1=-Rf/R1*Ui1 ; 同理可得:Uo2=-Rf/R2*Ui2 ; Uo3=-Rf/R3*Ui3 ; 总输出Uo=Uo1+Uo2+Uo3 ;当Rf=R1=R2=R3时, Uo=-(Ui1+Ui2+Ui3),完成了输入信号的反相叠加。

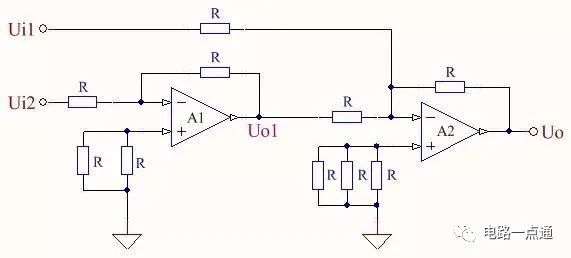

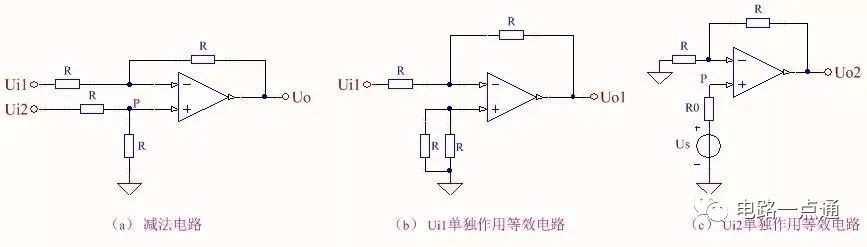

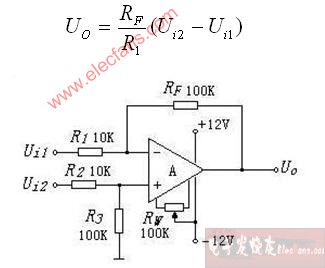

二.采用不同思路可构成不同的求差电路。用信号反相并求和的思想,可以得到图四所示的减法电路。

图四 信号反相与叠加实现的求差电路

该电路由两级运放构成,其中A1构成反相器,A2构成两信号反相叠加电路,图中运放同相端并联的电阻,是为了运放两输入端的电阻平衡。第一级输出Uo1=-Ui2 ; 按图三反相叠加电路的结论,得该电路输出为:Uo=-(Uo1+Ui1)=Ui2-Ui1 ,实现了信号的求差运算。

图五 差分电路实现的求差电路

图五是按同相比例和反相比例相结合的思想,利用差分电路构成的求差电路,与图四相比,只用一个运放单元,但该电路不能用虚地概念,运放两输入端存在共模电压,实际使用时,应尽量选高共模抑制比的运放。当Ui1单独作用时,等效电路如图五(b)所示,为基本反比例电路,此时Uo1=-Ui1 ; 当Ui2单独作用时,利用戴维南定理,将电路等效为图五(c)所示电路,其为基本同相比例电路,P点开路电压Us=R/(R+R)*Ui2=0.5Ui2 ; 等效电源内阻R0=R//R ; 直接套用同相比例电路公式, 得Uo2=(1+R/R)*Us=Ui2 ; 电路输出Uo=Uo2+Uo1= Ui2-Ui1 ; 实现了信号求差运算。

- 运算电路

+关注

关注

8文章

114浏览量

26621 - 电压

+关注

关注

45文章

5293浏览量

114879 - 接地

+关注

关注

7文章

714浏览量

45293

原文标题:信号叠加和求差电路

文章出处:【微信号:硬件测试杂谈,微信公众号:硬件测试杂谈】欢迎添加关注!文章转载请注明出处。

发布评论请先登录

相关推荐

比例求和运算电路实验

比例求和运算电路

比例运算电路:同相比例运算电路与反向比例运算电路的区别

什么是电路拓扑结构_多种pfc电路的拓扑结构介绍

比例运算电路基本拓扑结构

比例运算电路基本拓扑结构

评论