监控系统中对更高质量视频图像的需求需要在传感器和可用视频数据之间建立高级链接。仅由软件处理组成的图像处理系统无法满足这些需求,基于ASIC的系统无法提供所需的灵活性。由于像素处理的计算密集型特性,使用JPEG2000编码的基于FPGA的成像处理设计提供了一种强大而灵活的方法。

高清数字视频已变得司空见惯;我们大多数人都在自己的家中拥有高清设备。然而,将该技术转移到实时军事监视应用在捕获高清图像和分发大量数据方面带来了重大挑战。图像传感器现在正在千兆像素领域生产,使用较小的百万像素探测器阵列实现。图像数据采集必须灵活,以便于与各种传感器接口,并且必须与数据处理和压缩紧密耦合才能分发数据。与传统软件或ASIC成像处理系统相比,利用FPGA协处理器具有许多优势,并且可以将复杂的算法打包到一个小型,功能强大的设备中。

因此,基于FPGA的处理器可以在高清图像传感器和低带宽JPEG2000压缩数据之间提供关键链路。可重构计算的这一趋势使得满足机载和地面车辆平台(如捕食者无人机、收割者无人机、蜂鸟无人机直升机、MULE自主地面机器人、浮空器等)中强大成像系统的需求成为可能。基于 FPGA 的高性能计算允许军事监视系统接收和处理来自各种来源的高清传感器数据,并使用 JPEG2000 压缩数据以进行传输。

像素处理对于 FPGA 而言是无痛的

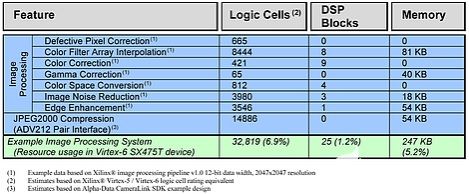

图像像素处理的高度计算特性可以在现代FPGA器件中高效实现。Virtex-6 SX475T FPGA 具有超过 475 K 个逻辑单元和 2,016 个嵌入式 DSP 模块,可灵活连接到系统的其余部分,包括集成的 6.5 Gb 收发器以及许多其他功能强大的元件。这些特性允许在单个FPGA器件中将许多图像处理功能流水线连接在一起,用于多个图像传感器。表1中详述的示例图像处理设计表明,全功能图像处理和压缩通道只需要不到7%的FPGA资源。

表 1:图像处理系统示例 – FPGA 资源要求

(单击图形可缩放 1.9 倍)

图像处理系统需求:够硬吗?

军事监视系统希望能够查看广阔的区域,例如大于16平方公里,因为“通过苏打吸管观察”无法获得太多信息。此外,监控系统通常必须在距离目标数公里的距离内运行,以保持安全,同时生成高分辨率图像。所有这些都需要捕获和处理大量的图像数据。例如,DARPA ARGUS-IS系统使用368个500万像素探测器(总计1.8千兆像素),能够生成超过260 Gbps的原始数据。

这些数据必须在实时系统中捕获和处理,通常具有极端的SWaP限制。此外,成像系统在捕获原始像素数据后可能需要许多其他所需的功能才能使用:

有缺陷的像素校正

彩色滤光片阵列插值

色彩校正

伽玛校正

色彩空间转换

图像降噪

边缘增强

视频缩放

视频窗口 – 对象跟踪

稳

视频压缩(JPEG2000、H.264、MPEG-4)

数据加密

用于传输和/或存储的视频输出

基于FPGA处理器的可重构计算技术非常适合满足这些苛刻的需求。这种方法比专用软件处理系统更小、更快、更高效,并且比ASIC方法更灵活、更具成本效益。图像传感器和软件处理之间的基本环节非常适合FPGA技术。

适应各种图像传感器接口

监控系统和其他成像平台正在迅速发展和扩展,以利用各种传感器进行光学,红外和合成孔径雷达技术,并且图像尺寸一直在增加。图像传感器的物理接口各不相同,因此处理系统需要一个灵活的模块化接口,以便与这些系统一起扩展和扩展。可重构计算系统通过支持多种格式和物理接口的传入数据来满足这一需求,例如,CameraLink、SDI、原始像素、LVDS、多千兆位串行接口、光纤等。基于FPGA的系统非常适合从各种来源和协议采集图像数据,因为具有可编程I/O模块、集成收发器和SERDES模块。

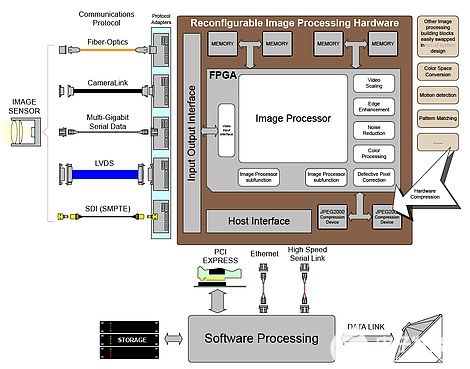

此外,监控系统可能具有许多不同的任务目标,这些目标需要在处理视频数据时具有灵活性。例如,系统可能需要每隔几秒钟提供整个视场的全分辨率图像,或者使用较小的图像窗口跟踪移动目标,该窗口以10 Hz更新。系统可能需要控制图像系统具有的数据带宽,以便下行链路或存储数据以供以后传输。基于FPGA的图像处理器可以在系统中重新配置,从而允许在不修改硬件的情况下添加升级和附加功能,例如模式匹配或运动检测。与任何预定义的图像采集卡或基于ASIC的硬件相比,这是一个很大的优势。图1显示了可重构图像处理系统的灵活性,该系统能够从各种源和接口接收图像数据,实现一系列计算复杂的图像处理功能,并通过各种接口输出压缩的视频流。

图 1:可重构图像处理硬件的灵活性

使用 JPEG2000 进行前期数据压缩

从任何系统中的彩色图像传感器接收的数据必须首先进行插值以获得每个像素的RGB分量,然后通常转换为YCrCb色彩空间,以使用色度子采样来减少数据量。然而,通过使用FPGA处理系统,视频数据可以使用JPEG2000进一步压缩,并且在无损压缩中将带宽额外减少2:1,在视觉无损压缩中减少10:1,在有损压缩中最大可降低100:1。FPGA图像处理器提供的压缩数据允许系统轻松存储,通过软件进一步处理,并将数据传输给用户。使用 JPEG2000 进行图像数据压缩可为系统提供卓越的结果,而无需预先进行数据压缩,并减少系统需要处理的数据。

JPEG2000编解码器在军事监视应用中特别受欢迎,因为它提供了非常高的性能,低延迟,执行无损压缩的能力以及其他非常有用的功能。这种压缩标准的工作原理是使用小波变换将单个图像帧分解成分辨率越来越低的子波段。然后将数据排列成数据包,其中包含有关连续像素组的信息。生成的图像流提供了有用的功能,例如可选区域、可选分辨率、错误恢复能力和带宽限制,此外还允许系统以图像流的压缩格式使用它。例如,JPEG2000数据可用于远程监控系统,以从相同的图像传感器下行链接小型高清图像窗口或广域快照的灵活组合,而无需先解压缩数据。

它也可以在特定带宽下使用,只需提取部分JPEG2000数据并截断流的更高分辨率部分即可。这对于传输图像数据非常有用,因为图像中最重要的信息可以使用不到20%的JPEG2000数据流来传递。由于每个视频帧都经过单独压缩,因此进一步增强了这种误差恢复能力,这使得数据链路能够以较少的纠错方式运行。因此,与其他压缩标准相比,JPEG2000对数据丢失的担忧较少,后者需要来自多个帧的信息进行解码。最后,JPEG2000数据可以在同一原始流中以不同的分辨率和质量进行查看。

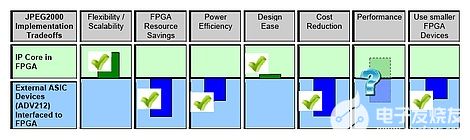

虽然JPEG2000编码器的实现相当复杂,但FPGA提供了大量资源,可以在图像处理设计中包含此功能。有一些 IP 核可随时集成到 FPGA 设计中,或者 FPGA 可用于与 ADV212 ASIC(JPEG2000 片上系统)接口。这两个选项都有自己的优点和缺点(表2),这些编解码器选项中的任何一个都可以在COTS硬件上使用,例如阿尔法数据ADM-XRC-5T2-ADV夹层FPGA板。

表 2:在 FPGA 中使用 IP 核实现 JPEG2000 图像压缩时,与使用连接到 FPGA 的外部 ASIC 设备相比,需要进行设计权衡。

将 COTS FPGA 硬件用于图像处理器

为了 促进 高级 图像 数据 处理, 模 块 化 FPGA 图像 处理 板 ( 例如 基于 PMC/XMC 的 板 卡 ) 可以 用于 工业 标准 的 嵌入式 计算 系统, 包括 CompactPCI、 VME、 VXS、 VPX、 PCI、 PCI Express 和其他 外 形 规格 中的 系统。这些小型 (74 mm x 144 mm) 模块可与最大的 FPGA 器件一起使用,可用于工作站开发系统,或直接移至坚固耐用的部署监控系统中。对于 JPEG2000 压缩,COTS 板提供 IP 核所需的大量板载内存和/或专用 JPEG2000 专用集成电路。主机计算系统可以轻松控制硬件图像处理器卡以应用用户设置,重新配置FPGA以进行各种视频操作,控制图像窗口,命令目标跟踪以及接收输出视频流。这种COTS硬件通常提供软件驱动程序和API接口,使控制和数据传输在系统中无缝。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19259浏览量

229638 -

dsp

+关注

关注

553文章

7987浏览量

348724 -

FPGA

+关注

关注

1628文章

21728浏览量

602949

发布评论请先 登录

相关推荐

基于FPGA的可重构系统结构分析

求一种可重构测控系统的设计构想

面向可重构系统的一种功耗相关硬件任务调度算法设计

一种基于体系结构模板的粗粒度可重构SoC设计方法

一种可重构的硬件处理器方法

一种可重构的硬件处理器方法

评论