高性能计算(HPC)市场进入超预期的高速发展阶段,先进封装Advanced Packaging成为高性能运算芯片成功与否的关键技术。在第十四届中国集成电路封测产业链创新发展高峰论坛(CIPA 2022)“高峰论坛”上,矽品研发中心副总经理王愉博博士与产业探讨未来高性能计算的先进封装发展趋势。

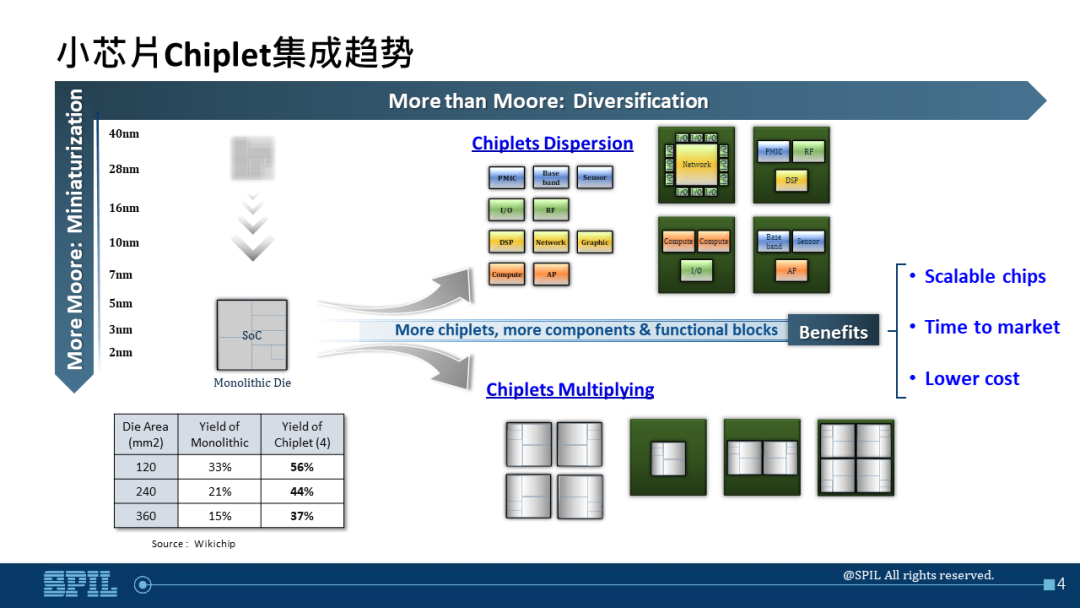

数据处理需求激增,AI算力对于高性能计算GPU的需求日趋增长,芯片上的晶体管数量也以十倍的成长率迅速增长。为了满足晶体管的数量,芯片的尺寸越来越大,但同时受限于radicle size而造成发展瓶颈。在摩尔定律趋缓,芯片的价格越来越高,良率因为芯片的尺寸增大而日益下降,小芯片Chiplet已成为先进封装发展的重要趋势。

王博士说明在最新一代Chiplet,依照不同的功能做区隔,使整体的速度效益达到明显的提升。或是利用封装体的形态把两个相同的芯片相互串联,发挥更高的效能,这种Chiplet表现方式可避免芯片因尺寸太大而造成晶圆厂制作的良率损失。无论Foundry或OSAT,都可以运用多种封装相结合的方式整合,包含2.5D/3D IC封装,以及FO-EB及FO-MCM封装等,王博士详细分析封装形态如何把Chiplet运用在未来高性能运算。

UCLe产业联盟

由日月光、AMD、Arm、Google Cloud、Intel、Meta、微软(Microsoft)、高通(Qualcomm)、三星(Samsung)和台积电(TSMC)等半导体业者共同组成UCIe(Universal Chiplet Interconnect Express)产业联盟持续推动芯片互连(die-to-die interconnect)技术标准化和促进开放式Chiplet生态系统,目前已有超过40家公司加入联盟,透过UCIe制定协定标准将可有效提高Chiplet生态系统整体效率,降低开发时间和成本。

日月光在封装和互连平台技术的专业知识,有助于确保UCIe提出的标准切实可行,并且在封装制造具有商业可行性和成本效益。

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50714浏览量

423138 -

日月光

+关注

关注

0文章

146浏览量

19039 -

chiplet

+关注

关注

6文章

431浏览量

12584

原文标题:Chiplet 小芯片的时代机遇与趋势

文章出处:【微信号:ASE_GROUP,微信公众号:ASE日月光】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Chiplet在先进封装中的重要性

Chiplet技术有哪些优势

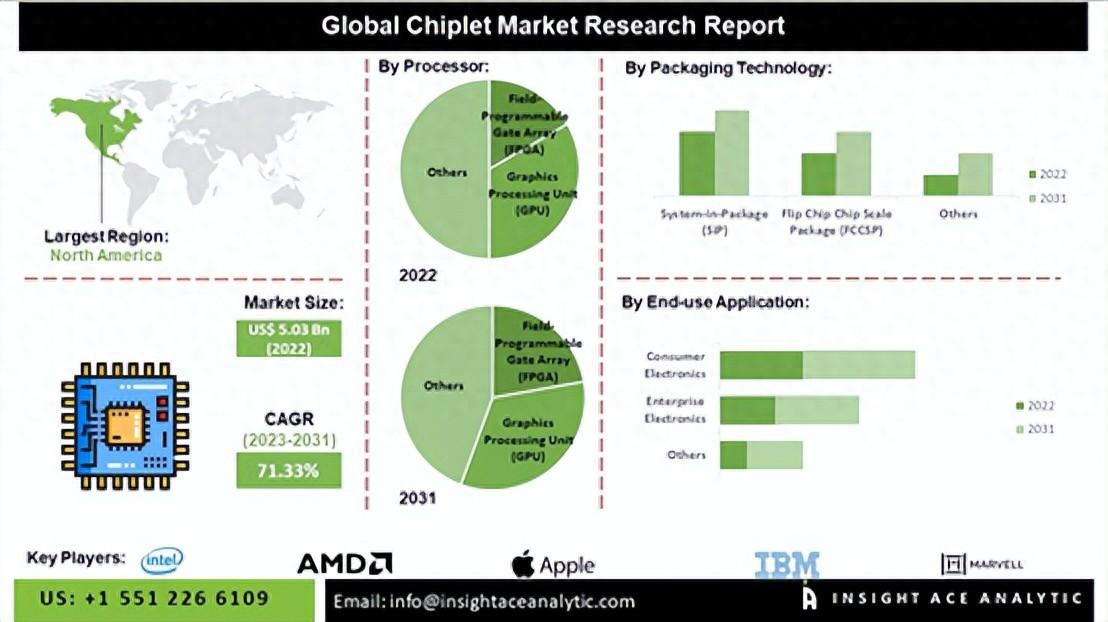

2031年全球Chiplet市场预测

国产半导体新希望:Chiplet技术助力“弯道超车”!

剖析 Chiplet 时代的布局规划演进

西门子EDA创新解决方案确保Chiplet设计的成功应用

Chiplet是否也走上了集成竞赛的道路?

Chiplet技术对英特尔和台积电有哪些影响呢?

芯砺智能Chiplet Die-to-Die互连IP芯片成功回片

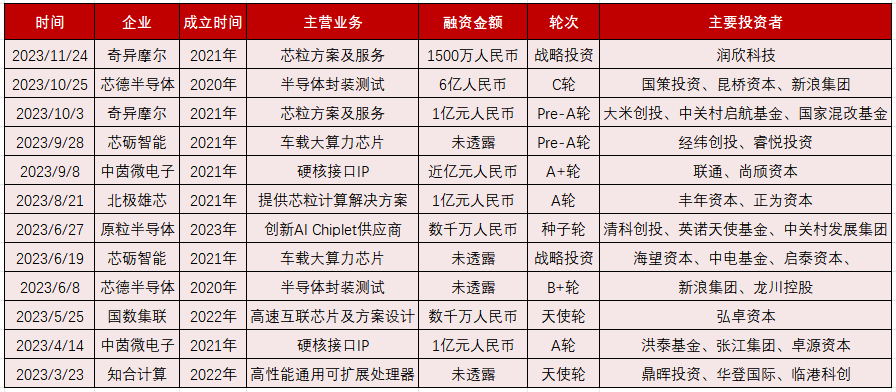

2023年Chiplet发展进入新阶段,半导体封测、IP企业多次融资

Chiplet小芯片的时代机遇与趋势

Chiplet小芯片的时代机遇与趋势

评论