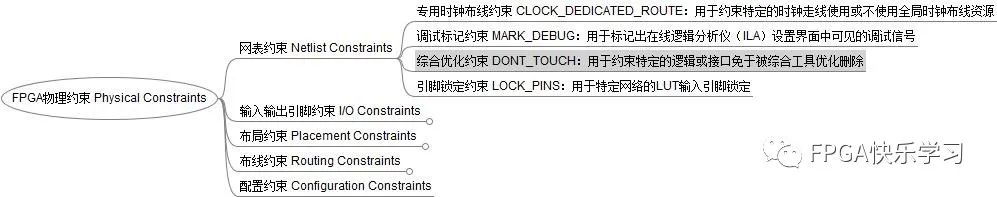

概述

对设计中的信号施加DONT_TOUCH约束,可以避免这些信号在综合编译过程中被优化掉。例如,有些信号节点在综合或布局布线编译过程中可能会被优化掉,但是我们希望在后期调试过程中能够监控到这些信号,此时就可以使用DONT_TOUCH约束达到保留这些信号的目的。又如,有时在设计中会对一些高扇出的信号进行手动的逻辑复制,也可以使用DONT_TOUCH约束避免它们被优化掉。

工程实践

下面有一个简单的例子,看看DONT_TOUCH约束如何使用。原始代码如下,目前只有一个寄存器vga_valid,它对应了adv7123_blank_n、vga_r、vga_g、vga_b等信号的输出。

reg vga_valid;

always @(posedge clk or negedge rst_n)

vga_valid<= vga_origin_vld;

assign adv7123_blank_n = vga_valid;

assign vga_r = vga_valid ? vga_rdb:5'd0;

assign vga_g = vga_valid ? vga_gdb:6'd0;

assign vga_b = vga_valid ? vga_bdb:5'd0;

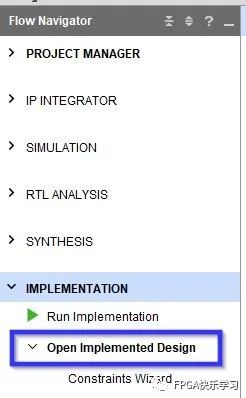

编译工程后,点击RunImplementation,打开实现界面。

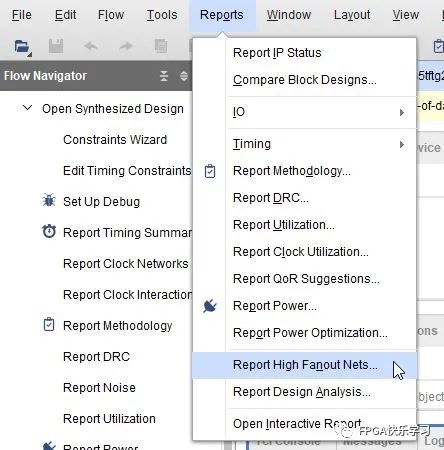

点击菜单Reports à Report High Fanout Nets。

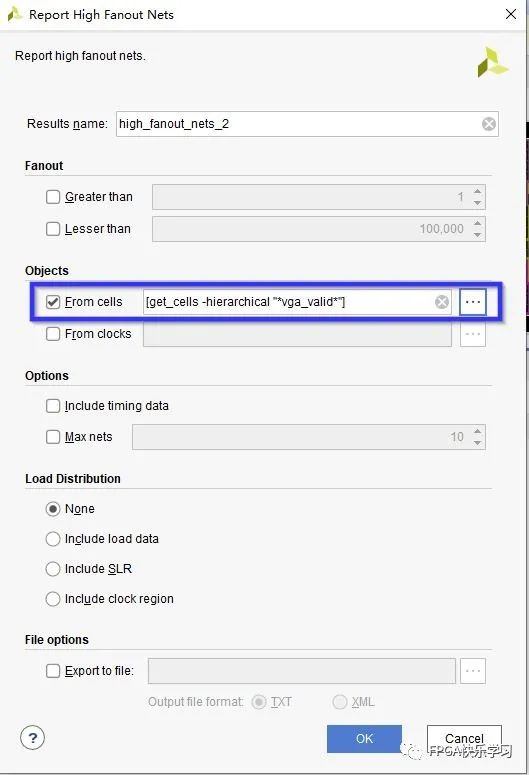

如图,设定From cells为[get_cells-hierarchical "*vga_valid*"],即查看所有带vga_valid字符的信号。

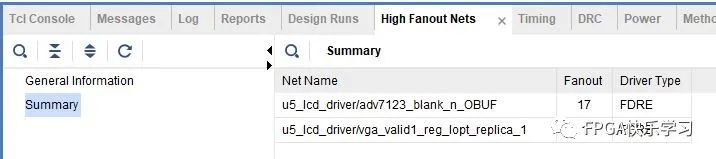

此时,可以看到当前vga_valid信号的扇出为17。

这个例子中,vga_valid的扇出为,其实并不多。但是在实际工程中,我们可以通过类似的方式查看到设计中高扇出的关键信号节点。然后,我们会如下在代码中,对这样的信号做逻辑复制。意图减少单个信号的扇出。

reg vga_valid1;

reg vga_valid2;

always @(posedge clk or negedge rst_n)

vga_valid1<= vga_origin_vld;

always @(posedge clk or negedge rst_n)

vga_valid2<= vga_origin_vld;

assign adv7123_blank_n = vga_valid1;

assign vga_r = vga_valid2 ? vga_rdb:5'd0;

assign vga_g = vga_valid1 ? vga_gdb:6'd0;

assign vga_b = vga_valid2 ? vga_bdb:5'd0;

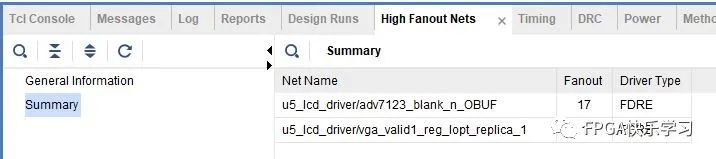

如图,可惜我们做过逻辑复制的代码,最终综合实现下来,并没有减少扇出,和原始代码实现的效果完全一样。怎么回事?综合工具太聪明了,识别了你这个小伎俩,为了减少设计资源消耗,综合工具默认优化掉了代码中新增加的vga_valid2。

但是,工具并不懂我们真正的心思,怎么办?此时DONT_TOUCH约束就派上用场了。如下,在不希望被综合优化的2个寄存器前面,加上(*dont_touch ="true"*)的语法。

(*dont_touch = "true"*) reg vga_valid1;

(*dont_touch = "true"*) reg vga_valid2;

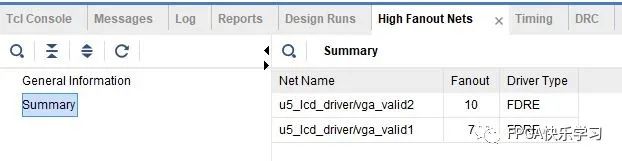

重新编译后,我们看到,代码生效了。vga_valid1和vga_valid2分担了原本vga_valid的扇出。

-

寄存器

+关注

关注

31文章

5336浏览量

120224 -

网表

+关注

关注

0文章

15浏览量

7646

原文标题:物理约束实践:网表约束DONT_TOUCH

文章出处:【微信号:FPGA快乐学习,微信公众号:FPGA快乐学习】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA物理约束之布局约束

物理约束之配置约束

物理约束之布局约束

DONT_TOUCH约束

touch DONT_TOUCH约束

Adam Taylor玩转MicroZed系列74:物理约束

物理约束实践:网表约束DONT_TOUCH

物理约束实践:网表约束DONT_TOUCH

评论