作者:Sanjay Rajasekhar and Arvind Shankar

多路复用(多路复用)逐次逼近寄存器模数转换器(SAR ADC)应用具有尺寸和功率限制,通常由每通道vwin 信号链设计选择决定。本文介绍了为什么配备模拟输入高阻态(高阻抗)技术的多路复用SAR ADC是大幅减小解决方案尺寸和功耗而又不影响性能和精度的关键。

介绍

多路复用SAR ADC通常用于需要持续监控系统中多个关键变量的应用。在光通信应用中,激光偏置可以通过光功率测量进行监测,而在VSM应用中可以监测来自电极的EEG/ECG信号。这些多路复用应用程序有一些共同的要求:

有许多频道需要监控。通常,ADC通过所有通道进行排序。

通道电压通常彼此不相关。

系统级尺寸和功耗存在严格的限制。

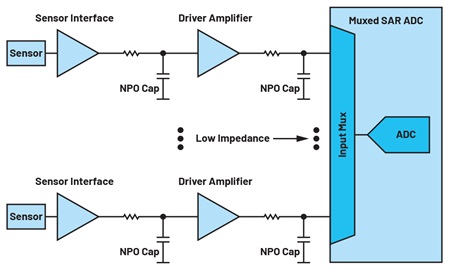

由于这些要求,出现了一些挑战。当ADC在一个通道上完成转换时,ADC内的采样电容充电至通道电压。如果采样电容上的该电压与顺序上的下一个通道电压大不相同,则必须设计信号链,以便在允许的采集时间内将采样电容精确地建立到新电压。传统上,这个问题的解决方案是使用宽带驱动放大器和RC滤波器。典型信号链如图1所示。

图1.具有传统多路复用SAR ADC的信号链。

传感器可以输出电压或电流,传感器接口电路可以分别是仪表放大器或跨阻放大器。电容器通常为NP0/C0G类型,因为其他类型的电容器会导致明显的失真。NP0电容器具有高线性度但低密度。选择NP0电容的值也比ADC内部采样电容大得多。它执行两个关键功能:

减少ADC采样电容的反冲

通过滤除超出所需建立带宽的噪声来降低信号链的宽带噪声

在传统的信号链中,人们被迫使用一个驱动放大器和一个大电容。每个驱动器放大器的功耗可能在十分之一mA到几mA之间。每个电容器(包括间隙)可能占用约 1 mm2的电路板区域。在许多通道上复制该信号链会对系统尺寸和功耗产生显著不利影响。这是当今多路复用SAR ADC应用的主要问题之一。

什么是输入高阻技术?

在模拟输入的上下文中,术语高阻态技术是指在不消耗静态或连续功率的情况下大幅增加ADC的有效输入阻抗的电路技术的集合。这使得ADC的输入易于驱动。

假设多路复用ADC在通道N – 1上转换,下一个要转换的通道是通道N。

在转换启动(CNV)的上升沿,对通道电压进行采样。在图2中,CNV的第一个上升沿对通道N – 1上的电压进行采样。然后,ADC转换通道N – 1上的采样电压。转换后,禁用输入高阻态,ADC继续采集序列中的下一个通道,即通道N。通道N上的电压通常与通道N – 1上的电压有很大不同,ADC电容现在充电到通道N-1。这会导致通道N(深蓝色虚线)上的电压产生巨大的冲击,并在采样时刻(CNV的第二上升沿)引入较大的通道电压误差。这就需要一个大的外部电容器来吸收冲击力,需要一个驱动放大器来提供必要的电荷。

图2.高阻态使能和禁用时AD4696的相位。

当输入高阻态使能时,ADC的内部采样电容在开始实际采集之前充电至其将要采集的通道上的当前电压。在通道N – 1上转换后,立即引入一个高阻态相位,将ADC采样电容精确充电至通道N上的当前电压。这意味着,当ADC采样电容连接到外部输入时,它不会产生任何电荷,也不会产生任何反冲。在实践中,由于内部开关的电荷注入(第一次充电踢),通常会有很小的残余误差。这种小的残余误差导致通道N采样时刻的建立误差几乎可以忽略不计。启用高阻态时的这种电荷误差将极大地改善系统的稳定动态。

当通道N上的采样完成后,ADC必须继续进行转换。因此,内部开关将ADC采样电容与外部输入断开。这会导致由于开关开路电荷注入而导致第二次充电踢。通常,第二次电荷踢有更长的建立时间,因此第一次电荷踢的大小决定了通道上的建立误差。因此,必须将第一次电荷踢的大小降至最低。

输入高阻态技术作为EasyDrive的一部分集成到AD4696(最新一代多路复用SAR ADC)中™功能集。因此,AD4696在通道上开始采集非常顺利。它免除了为每个通道增设反冲吸收电容器和驱动放大器的需要。这大大降低了系统尺寸和功耗,并显著简化了信号链,如图3所示。

图3.采用AD4696多路复用SAR ADC的信号链。

AD4696系列采用输入高阻态的一个重要优势是,执行高阻态功能的电路都可以以转换速率进行上电循环。因此,高阻态函数的功耗与ADC的吞吐速率成线性关系,就像核心SAR ADC本身一样。与传统的、相当刚性的信号链设计相比,这提供了极大的灵活性。

输入高阻态功能也内置于LTspice模型®的AD4696。对第一次和第二次电荷踢进行精确建模,从而能够可靠地仿真信号链设计的稳定伪影。

一些微妙之处

回想一下,NP0电容还为信号链提供宽带噪声滤波。现在我们想消除电容器,我们必须找到其他方法来过滤噪声。实现相同有效信号链噪声带宽的一种简单方法是增加外部串联电阻。AD4696内置一个60 pF内部电容和一个240 Ω典型内部电容串联。通过设置外部电阻,我们可以将信号链噪声带宽调谐到所需值。

如果没有NP0电容,外部电阻在信号链的噪声性能、线性度和精度方面起着重要作用。小值电阻有助于快速建立采样电荷,从而提高线性度和精度,但代价是有效噪声带宽更高,导致总噪声增加。相反,大阻值电阻可以更好地滤除噪声,但代价是线性度和精度下降。

如下一节所述,AD4696中高阻态技术的一大优势是,它允许使用大阻值电阻(以获得更好的噪声滤波),而不会降低线性度和精度。这样可以优化信号链中的所有参数——噪声、线性度、精度、功耗和解决方案尺寸。

测量结果

测量采用2 kΩ外部电阻,无需任何NP0电容。结果表明,启用模拟输入高阻时,交流和直流性能显著提高。该实验涉及AD4696内核ADC以1 MSPS运行,但选择越来越多的通道作为循环序列的一部分。数据在一个通道上收集,而序列中的其他通道则提供0 V输入。

图4显示了1 kHz、–1 dBFS音调下目标通道的失真性能。当通道在禁用高阻态的情况下排序时,由于采样电容未充电至后续通道电压,因此会出现非线性建立误差。这会导致明显的失真。启用高阻态后,失真性能有了很大的改善。

图4.THD 与序列中的通道数的关系。测试音:1 kHz,–1 dBFS。

图5显示了带和不带高阻态功能的直流稳态建立误差。在该测试中,目标通道提供接近满量程的输入,序列中的其他通道以0 V驱动。 在目标通道上执行转换,同时向序列添加越来越多的通道,并绘制平均输出代码与预期代码的偏移。

图5.16位电平LSB中的直流建立误差。

当内核ADC以低于1 MSPS的吞吐量运行时,用户可能需要进一步降低有效信号链噪声带宽,以限制模拟前端噪声混叠。这将需要更高的电阻值,而高阻态功能极大地有助于在这些条件下保持性能。

结论

AD4696系列器件采用的输入高阻态技术为多路复用SAR应用提供了无与伦比的优势,例如降低系统级功耗、减小尺寸和减少元件数量等,同时保持高水平的交流性能和直流精度。它免除了每个通道对专用驱动器放大器和反冲吸收电容器的需求。高阻态功能本身的功耗与ADC的吞吐速率成比例,为系统级设计提供了出色的灵活性和多功能性。AD4696的LTspice模型可用于仿真用户希望设计的任何系统中的电荷踢效应。

审核编辑:郭婷

-

放大器

+关注

关注

143文章

13583浏览量

213367 -

SAR

+关注

关注

3文章

416浏览量

45949 -

adc

+关注

关注

98文章

6495浏览量

544461

发布评论请先 登录

相关推荐

如何利用输入高阻态技术降低解决方案功耗和尺寸

如何利用输入高阻态技术降低解决方案功耗和尺寸

评论