作者:Rolynd Aquino , Francis Ian Calubag, and Janchris Espinoza

本文包含有关如何在创建自己的IBIS模型时使用LTspice的图解指南——从IBIS预建模程序到IBIS模型验证。它还包含有关如何在LTspice中准确提取IBIS模型的I-V、V-T、斜坡和C_comp数据的详细说明。此外,定性和定量FOM被描述为验证IBIS模型性能的方法。该用例介绍了假设的ADxxxxx 3态数字缓冲器的IBIS模型开发,它具有可用于输入的IBIS模板和3态CMOS接口,可以启动IBIS模型的创建。®

介绍

仿真在构建任何系统时都起着关键作用。它允许设计人员预见问题并防止耗时且昂贵的修订。目标始终是第一次就做对!在高速数字接口仿真的情况下,如果设计不当,简单的PCB走线可能会影响信号质量。在信号完整性仿真中,IBIS(输入/输出缓冲器信息规范)模型用作器件数字接口的表示。

如本IBIS系列文章的第一部分所述,IBIS是一种行为模型,它通过表格电流与电压(I-V)和电压与时间(V-T)数据描述器件数字接口的电气特性。重要的是,IBIS模型要尽可能准确,并且没有任何解析错误,以避免以后使用时出现任何问题。此外,对于具有数字接口的每个部件或设备,应该有一个可用的IBIS模型。因此,每当客户需要时,他们都可以直接从制造商的网页下载。但是,情况并非总是如此。对于IBIS模型用户来说,他们经常面临的一个问题是模型可用性。当他们为设计选择的零件没有IBIS模型时,这可能会延迟产品开发。

IBIS模型的最佳来源是制造商本身;但是,用户仍然可以创建IBIS模型。本文介绍了一种使用LTspice创建从SPICE模型派生的最基本IBIS模型的方法。以下各节使用IBIS建模手册4.0版中的规范来讨论LTspice仿真设置。验证IBIS模型也使用定性和定量品质因数来解决。

什么是“最基本的”IBIS模型?

为了帮助客户使用LTspice创建基本的IBIS模型,需要定义术语“基本”。基本的IBIS模型不仅取决于I/O模型关键字,还取决于需要建模的数字缓冲器类型。这意味着需要重新审视早期版本的IBIS,以定义对缓冲器进行建模所需的最低要求以及当时正在建模的数字接口类型。事实证明,单端CMOS缓冲器是可以使用IBIS建模的最简单的数字IO之一,这就是本文的讨论范围。

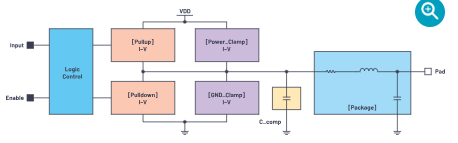

图1.3态CMOS缓冲器的IBIS模型。

| Model_type | [包装] | C_comp | [GND_夹] | [Power_夹] | [下拉] | [引体向上] | V-T 表 | [坡道] |

| 输入 | ✓ | ✓ | ✓ | ✓ | — | — | — | — |

| 3 态 | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ |

| I/O | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ |

图1显示了3态CMOS缓冲器IBIS模型的结构。如第1部分所述,IBIS模型中的组件或关键字取决于模型类型。表1总结了基本IBIS模型的组成部分,具体取决于Model_type。

使用案例

在本文中,将使用假设ADxxxx器件的LTspice模型来创建IBIS模型。它是一款具有使能引脚的单输入和单输出数字缓冲器。因此,生成的IBIS模型将有两个输入(DIN1和EN)和一个三态输出(DOUT1)。

作为一般准则,生成IBIS模型有五个基本步骤:

设置预建模过程。

执行LTspice仿真,从SPICE模型中提取C_comp、V-I和V-T数据。

格式化 IBIS 文件。

使用IBIS解析器测试检查文件。

将相同加载条件下IBIS模型的仿真结果与SPICE模型结果进行比较。

IBIS模型提供典型、最小和最大数据。它们通过工作电源电压范围、温度和工艺拐角来确定。为简洁起见,本文仅介绍典型条件。

ibischk系列黄金解析器可用于检查IBIS模型是否符合IBIS规范。ibischk 可执行文件可在 IBIS.ORG 网页上免费获得。本文使用了集成了ibischk的第三方IBIS模型编辑软件。

预建模程序

在开始仿真之前,用户应下载器件的数据手册,以及安装SPICE模型和LTspice文件。通过确定器件具有的数字接口数量和类型(例如输入、漏极开路、3 态等)对器件进行初始评估。

从器件数据手册中,确定工作电源电压、工作温度、集成电路 (IC) 封装类型、器件引脚排列、时序规格的负载条件 (R负荷和/或 C负荷)用于数字输出和低电平输入电压(V国际禁毒局) 和高电平输入电压 (V英赫) 用于数字输入。ADxxx SPICE模型如图1所示,其规格如表2所示。

图2.ADxxxx 3态数字缓冲器SPICE模型。

| 数据表参数 | 价值 |

| 电压输出 | 1.8 V(典型值) |

| 工作温度 | 25°C |

| V国际禁毒局 | 0.3 × VDD |

| V英赫 | 0.7 × VDD |

| 集成电路封装 | 6 引脚 SOT-23 |

| C负荷 | 15 pF |

通过使用关键字,有关设备数字接口的所有信息都放在IBIS文件中。关键字是IBIS模型中用括号括起来的标识符,如第1部分所述。详情请参考。

与IC封装模型相关的关键字是[封装]。它包含RLC(电阻-电感-电容)寄生效应,代表从芯片焊盘到IC焊盘/引脚的键合。此信息可以从制造商处获得。如果该设备与正在评估的设备具有完全相同的封装并且来自同一制造商,则还可以查找另一个IBIS文件的[包]数据。表 3 列出了 6 引脚 SOT-23 封装的器件封装寄生效应。

| [包装] | |||

| 变量 | 典型值 | 最小值 | 麦克斯 |

| R_pkg | 1.595E-01 | 那 | 那 |

| L_pkg | 4.455E-09 | 那 | 那 |

| C_pkg | 0.370E-12 | 那 | 那 |

器件引脚排列如表4所示。关键字 [Pin] 用于描述引脚及其相应的型号名称。[引脚] 通常采用 3 列格式。第一列用于引脚编号,第二列是引脚说明,第三列用于型号名称。一些封装具有更多类似的引脚(VCC,GND)。这些引脚可以按模型分组和描述在一起。在这种情况下,鉴于给出的SPICE模型没有关于内部晶体管级原理图的信息,最好为每个数字接口提供一个单独的模型。型号名称“电源”和“GND”用于命名IBIS文件中的电源和接地引脚。非数字接口和“不连接”引脚被描述为“NC”或无连接。请注意,型号名称区分大小写。由于它们将在建模过程的后面使用,因此应指示确切的模型名称。

| [引脚] | Signal_name | Model_name |

| 1 | 电压输出 | 权力 |

| 2 | 迪恩1 | cmos_di1 |

| 3 | 英文 | cmos_en |

| 4 | 杜特1 | cmos_out1 |

| 5 | 接地 | 接地 |

| 6 | 数控 | 数控 |

ADxxxx真值表如表5所示。这在设置LTspice仿真时非常有用。了解如何将DOUT1引脚设置为高阻抗(高阻态)模式、逻辑1和逻辑0非常重要。

| 英文 | 迪恩1 | 杜特1 |

| 0 | 0 | 高阻态 |

| 0 | 1 | 高阻态 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

LTspice 设置和仿真

通常,如前所述,IBIS模型通过I-V(电流与电压)和V-T(电压与时间)数据描述数字缓冲器的行为。每种类型的数字接口都有自己的一组IBIS建模所需的I-V和/或V-T数据,如表1所示。这些数据集在表 6 中更详细地呈现。记下每个数据集的备注。那些标记为“推荐”的表示它们的缺失不会导致 ibischk 解析器测试中的错误。但是,这些数据集在信道vwin 中具有一定的效果。例如,钳位数据有助于分析信号反射。

|

IBIS关键词 输入 |

输入 | 3 态 | ||

| V-I 数据 |

C_comp Z |

必填 | 必填 | |

| [Power_Clamp] | 推荐 | 推荐 | ||

| [GND_Clamp] | 推荐 | 推荐 | ||

| [引体向上] | — | 必填 | ||

|

[下拉] |

— | 必填 | ||

| V-T 数据 | [上升波形] | 加载到VDD | — | 推荐 |

| 负载至接地 | — | 推荐 | ||

| [下降波形] | 加载到VDD | — | 推荐 | |

| 负载至接地 | — | 推荐 | ||

| [坡道] | — | 必填 | ||

[Power_Clamp] 和 [GND_Clamp]

图3.[Power_Clamp] 和 [GND_Clamp] 关键字结构的概念图。

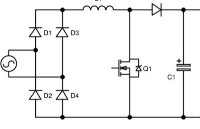

[GND_Clamp] 和 [Power_Clamp] 通过表格 I-V 数据显示数字缓冲器的静电放电 (ESD) 器件的行为。[Power_Clamp] 表示以 VDD 为基准的 ESD 器件的整体行为,而接地钳表示以 GND 为基准的 ESD 器件的整体行为。

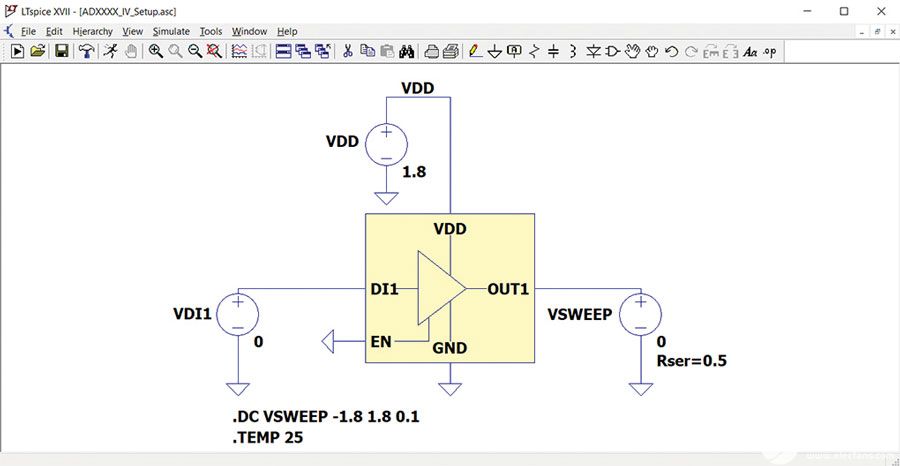

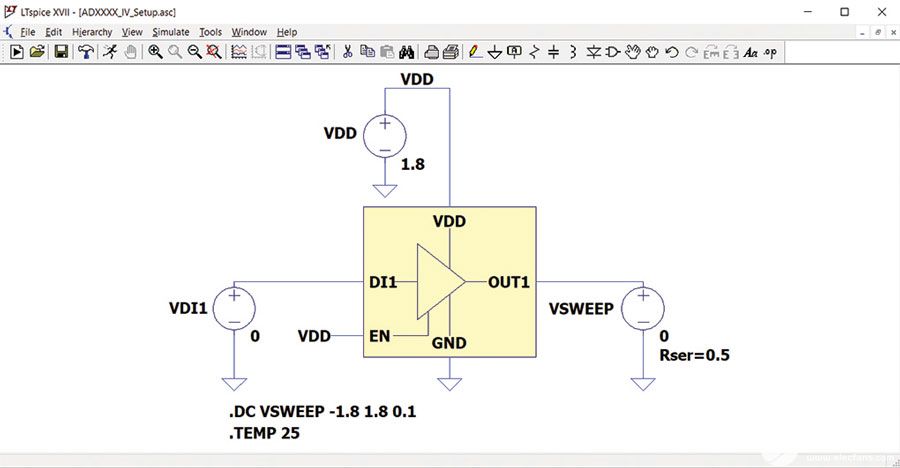

在LTspice中,I-V数据可以使用.DC SPICE 命令/指令。DOUT1的接地钳位使用图4中的设置进行测量。在设置中,施加适当的电源电压以将器件配置为高阻抗状态(请参阅表5)。这可确保ESD器件与核心电路隔离。VSWEEP是参考GND的扫描电压。 将VSWEEP接地可确保仅表征GND箝位ESD器件。

图4.ADxxxx DOUT1接地箝位设置。

根据IBIS规范,I-V数据应扫描到供电轨之外(最好从–VDD扫描至2 × VDD)——在本例中为–1.8 V至+3.6 V。通过直接执行此操作,超过VDD的扫描电压将打开电源钳ESD器件。为避免这种情况,最初将VSWEEP从–1.8 V扫描至+1.8 V,并使用外推方法添加3.6 V数据点。此方法适用于所有 I-V 数据集。

此外,请注意,所有 I-V 数据集最多只接受 100 个数据点。超过此数据点数将在 ibischk 解析器测试中提示错误。设置 .DC 命令使得生成的数据点数小于或等于 99。这是为了容纳 2 × VDD 外推的额外一个数据点。

使用直流扫描,在仿真中可能会遇到非常高的反向电流。为此,将起始扫描从近似二极管势垒电位(–0.7 V)设置为VDD(+1.8 V)。然后将符合 –VDD 的数据外推到 2 × VDD I-V 数据。另一种方法是将一个小电阻Rser与VSWEEP串联以限制极端电流。

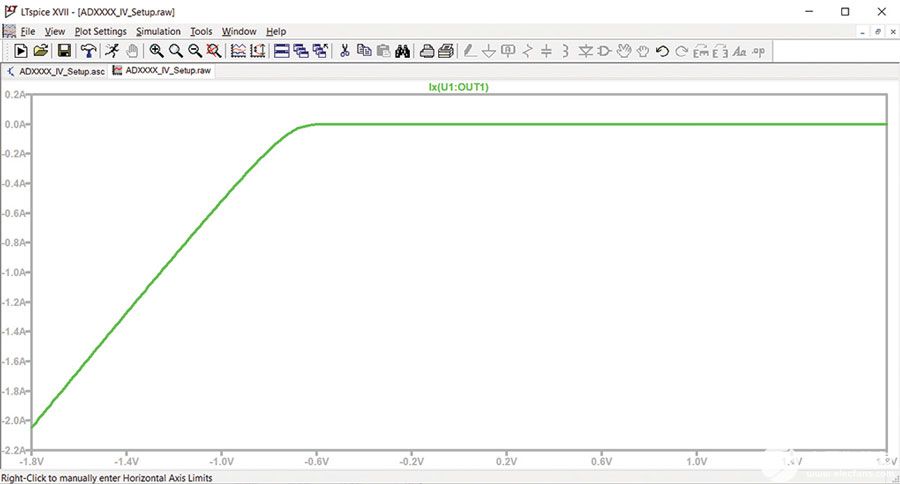

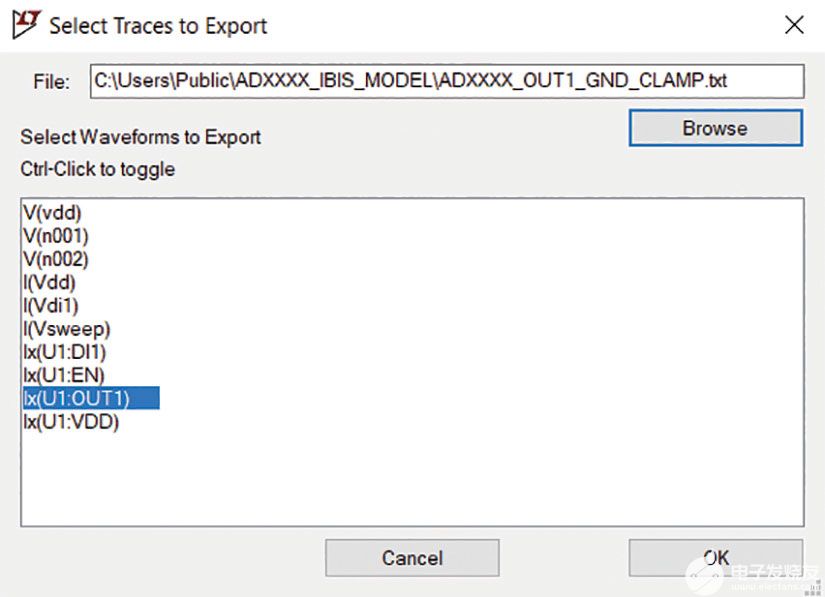

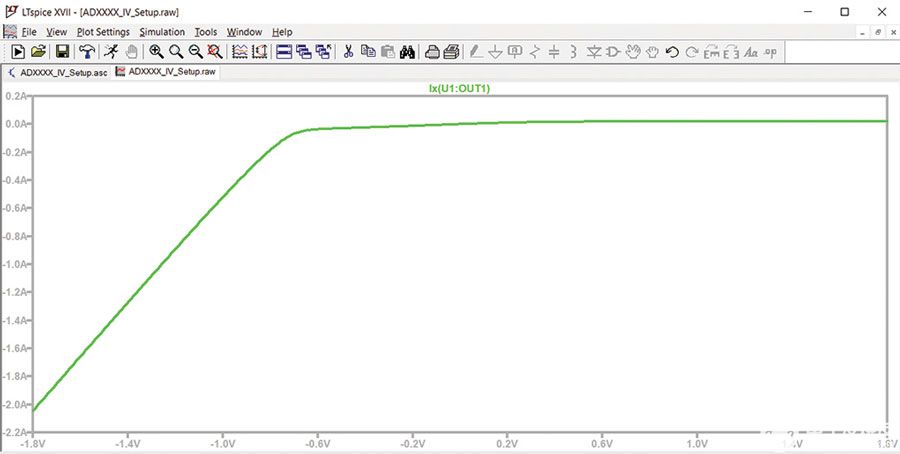

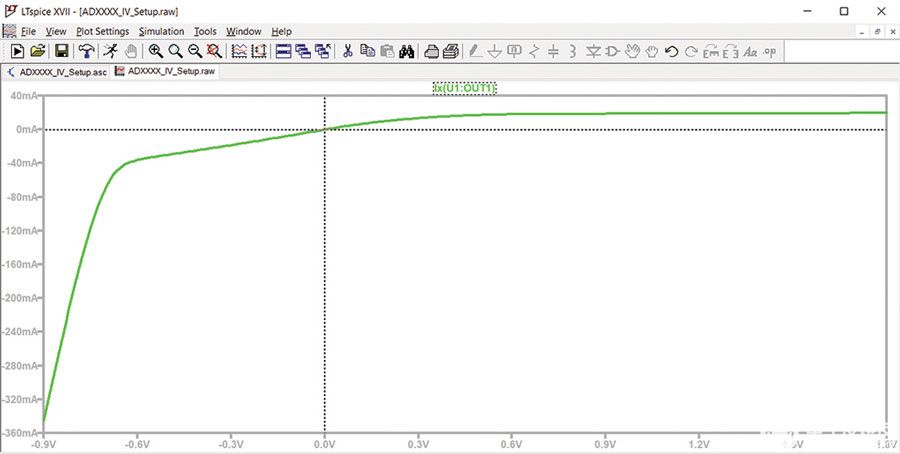

通过单击“运行”按钮,LTspice运行仿真。由于正在评估 DOUT1,因此感兴趣的节点是 Ix(U1:DOUT1)。虽然I(VSWEEP)在技术上也是正确的,但Ix(U1:DOUT1)上的电流极性是IBIS模型所需要的。这是为了尽量减少 I(VSWEEP) 数据的进一步数据格式,使其适合模型。结果应如图 5 中的图形所示。仿真后,先单击“结果”窗口保存数据,然后单击“文件”->“将数据导出为文本”。导航到要保存的目录,然后单击要测试的节点,然后单击“确定”(如图 6 所示)。

图5.接地钳仿真结果。

图6.将仿真数据导出为文本。

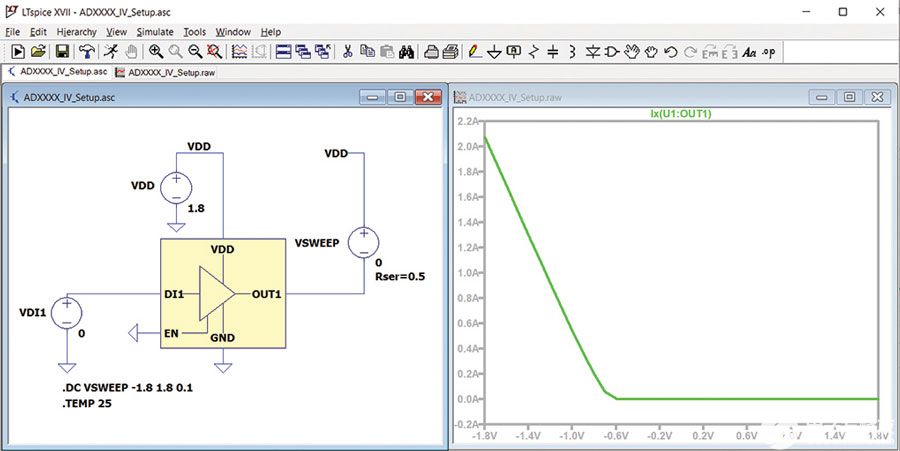

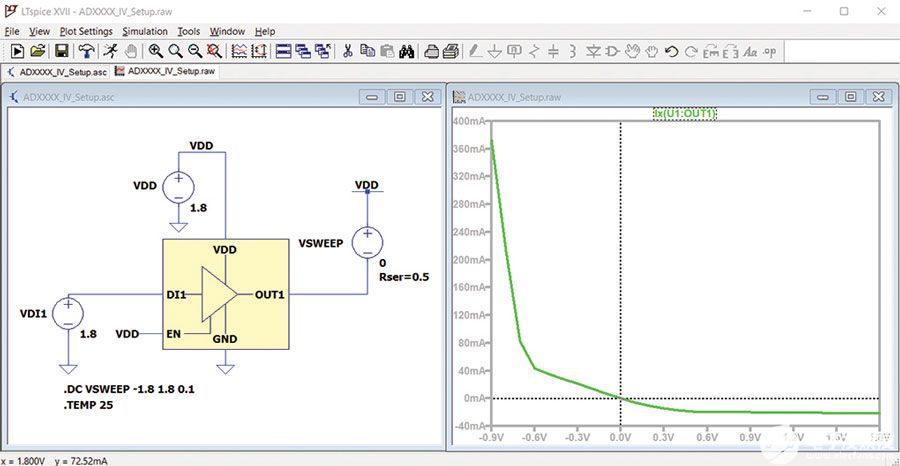

[Power_Clamp] 数据提取类似于接地钳位设置,使得扫描电压VSWEEP以VDD为参考。设置和结果如图7所示。

图7.ADxxxx OUT1电源钳位设置和结果。

[下拉] 和 [上拉]

图 8 显示了 I-V 关键字结构的概念图。[下拉] 和 [上拉] 表示缓冲区中上拉和下拉元素的行为。在图形形式中,它们看起来像MOSFET的I-V特性曲线。在提取[下拉]和[上拉]的数据时,重要的是要知道如何通过器件的真值表操纵从输出引脚发出的信号。提取[下拉]和[上拉]数据的设置类似于[GND_Clamp]和[Power_Clamp],只是DOUT1引脚使能而不是高阻态模式。

图8.I-V 关键字结构的概念图。

要提取[下拉]的数据,DOUT1引脚应设置为逻辑0输出或0 V。因此,必须设置适当的电源电压,如图9所示。在EN引脚上施加相当于1.8 V的逻辑高压以启用DOUT1引脚,在DIN1引脚上施加相当于1.8 V的逻辑高压,将DOUT1引脚设置为逻辑0输出。这可以通过表 5 中所示的真值表得到确认。结果如图 10 所示。

图9.ADxxxx OUT1 下拉设置。

图 10.ADxxxx OUT1 下拉图。

放大[下拉]数据,它类似于MOSFET的I-V特性曲线,如图11所示。

图 11.ADxxxx DOUT1 下拉图(缩放视图)。

在保存下拉数据时,请注意它构成了来自[GND_Clamp]和[下拉]的总电流。这可以在图 12 中的图表中更好地解释。要删除[GND_Clamp]组件,只需从[下拉]保存的数据中逐点减去它。为了更轻松地做到这一点,[GND_Clamp] 和 [下拉] 的直流分析的电压增量、起始电压和结束电压必须相同。

图 12.下拉保存数据的实际电流。

获取上拉数据的设置如图 13 所示。放置适当的电源电压以将DOUT1设置为逻辑1(1.8 V)。这可确保上拉元件处于活动状态/打开状态。然后,VSWEEP也从–1.8 V扫描至+1.8 V,并以VDD为基准。以这种方式连接VSWEEP可防止用户格式化数据以符合IBIS规范。

图 13.ADxxxx DOUT1 上拉设置和结果。

就像[下拉]一样,保存的[上拉]数据是总[Power_钳]和[上拉]电流的结果。因此,用户需要通过从保存的[上拉]数据中逐点减去[Power_Clamp]组件来删除它,如果他们的直流扫描参数相同,则可以轻松完成此操作。一般提醒一下,对所有 I-V 数据测量使用相同的直流扫描参数。

图 14.来自[上拉]保存数据的实际电流。

[C_comp]

[C_comp] 关键字表示缓冲区的电容,它具有不同的最小值、典型角和最大角值。它是晶体管和芯片的电容,它与封装电容不同。[C_comp]可以通过两种方式提取。可以使用公式1中的公式进行近似计算,也可以使用公式2中的公式在引脚由交流电压供电时计算。

哪里:

我艾克:测量电流的虚值

F:交流电源的频率

V交流:交流电源的振幅

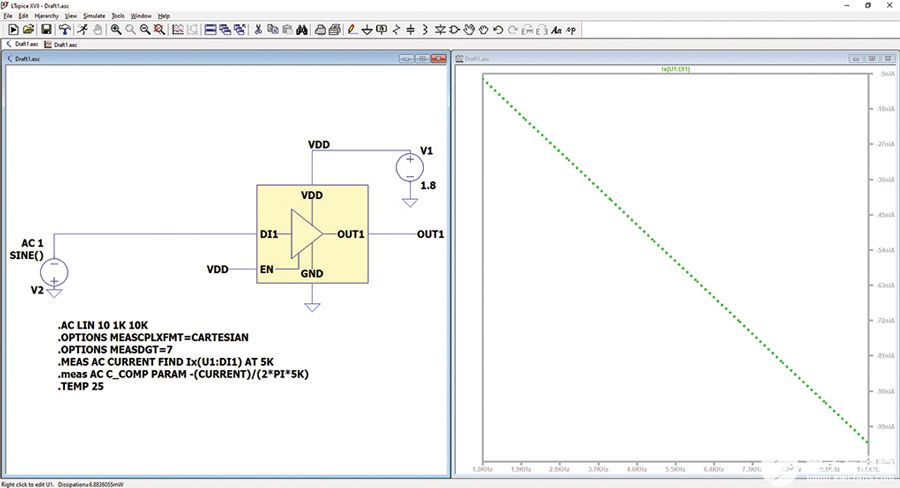

使用LTspice进行C_Comp萃取

缓冲电容可以通过提供具有频率扫描的交流电压来提取,如图15所示。由于提供交流电压,因此将测量电流的实部和虚部。电流的极性必须反转,以测量流入缓冲器的电流值,同时用交流电压供电。测量输出缓冲电容时,必须从图15中做出的唯一改变是,交流电源必须连接在输出引脚中。

图 15.ADxxxx C_comp提取设置。

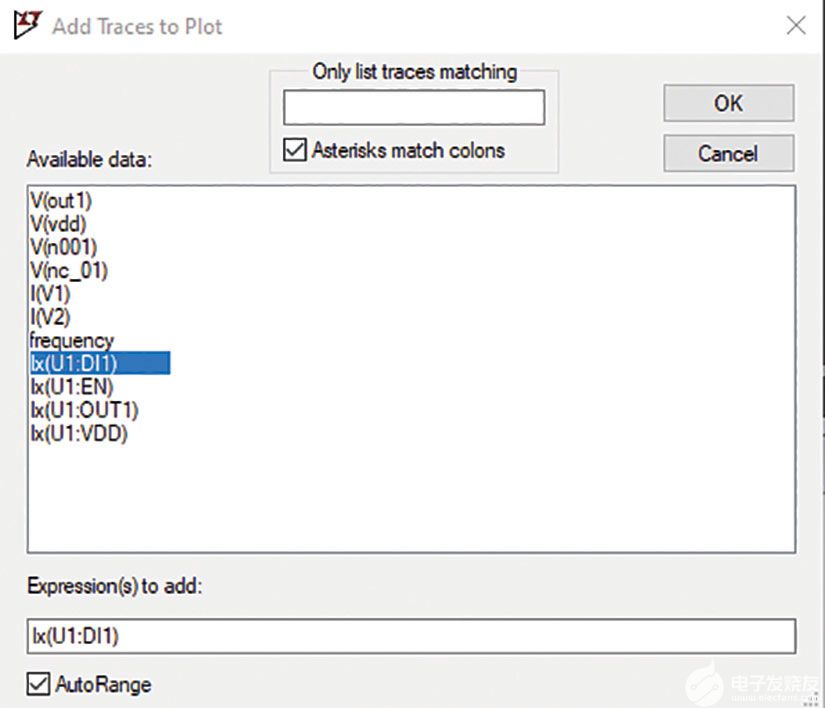

将提供具有任何幅度值的交流电压,但通常设置为1 V。它将按照SPICE指令的规定通过频率扫描进行处理。使用 .AC 命令,默认情况下设置为以波特模式显示,该模式使用 dB 单位。必须将其设置为笛卡尔模式才能看到电流的数值,以便可以直接将其处理为缓冲电容的公式。要查看缓冲电容的波形,用户必须首先右键单击“波形”窗口并单击“添加迹线”,然后选择要测量的引脚。波形图窗口将显示两条线。

实线表示测量电流的实际值,虚线表示测量电流的虚值。

图 16.“将迹线添加到打印”对话框。

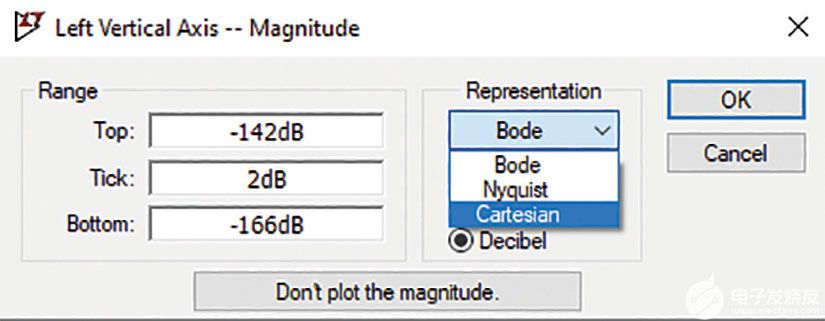

要将绘图设置从波特图更改为笛卡尔,请右键单击波形窗口左侧的 y 轴,它应打开左纵轴 - 幅度对话框。然后将绘图表示从波特更改为笛卡尔。

图 17.将情节设置从波特更改为笛卡尔。

LTspice 指令用于C_Comp设置

LTspice指令用于设置电路的工作模式、测量变量和过程参数,以计算C_comp。以下是用于测量缓冲器C_comp值的LTspice指令:

.AC Lin 10 1k 10k:将电路的工作模式设置为从1 kHz到10 kHz的交流线性频率扫描。

.Options meascplxfmt:将 .meas 命令的默认结果更改为波特模式、奈奎斯特模式或笛卡尔模式。

.选项 measdgt:设置 .meas 语句的有效数字数。

.meas语句:这些指令用于查找电路中某些参数的值。

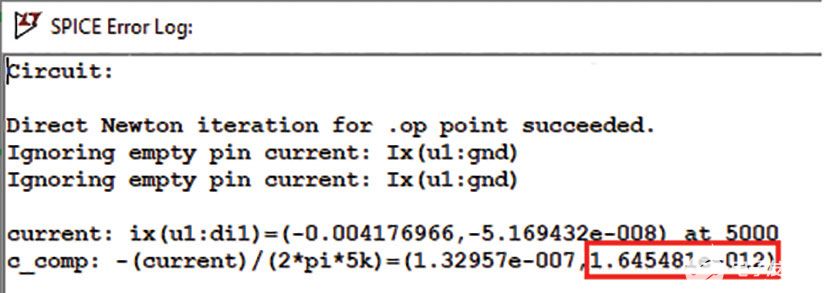

可以根据用户要显示的参数修改这些 SPICE 指令。有关可在LTspice中使用的指令的详细说明,请参见LTspice帮助。可以在工具> SPICE 错误日志中查看测量语句的结果。

SPICE错误日志中显示的结果将以笛卡尔形式出现。x坐标是电流和缓冲电容的实部,而y坐标是电流和缓冲电容的虚部。如上所述,在测量缓冲电容时,电流的虚部是缓冲电容所需的部分,因此C_comp的实际值是图18中突出显示的值。

图 18.测量语句导致 SPICE 错误日志。

[上升波形]和[下降波形]

什么是上升和下降波形?

[上升波形]和[下降波形]关键字对输出缓冲器的开关行为进行建模。建议在输出模型中包含四个 V-T 数据集:负载以接地为参考的上升和下降波形,以及负载以 VDD 为参考的上升和下降波形。

提取上升和下降的 V-T 数据

为了提取LTspice中OUT1的上升或下降波形,将分段线性(PWL)信号或脉冲电压电源形式的上升沿或下降沿输入激励发送到输入引脚。仿真中使用的输入激励的转换需要快速,以便为模型提取最快的输出转换。瞬态分析将使用 .TRAN 命令,同时测量输出引脚上的电压。50 Ω电阻用作负载,用于提取3态输出缓冲器的四个V-T波形的数据,但可能会因缓冲器设计和驱动能力而异,以实现输出转换。50 Ω是 V-T 数据提取的默认负载值,因为它是 PCB 走线阻抗的典型值。50 Ω负载相对于接地(负载对地)或VDD(负载对VDD)连接到缓冲器的输出引脚。

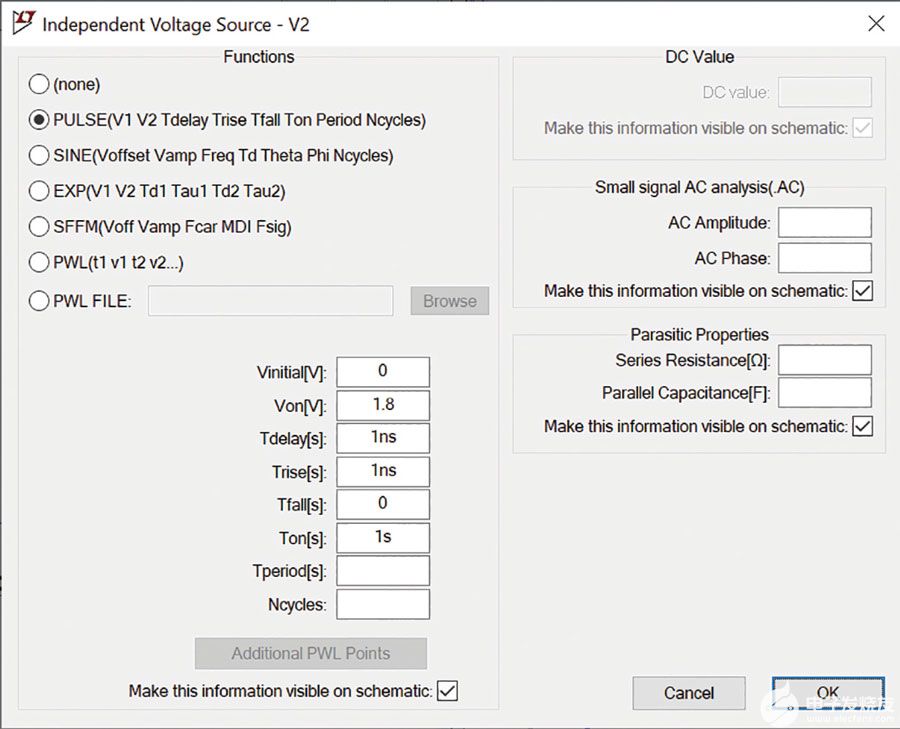

图 19.使用脉冲电压电源对上升沿输入激励进行采样。

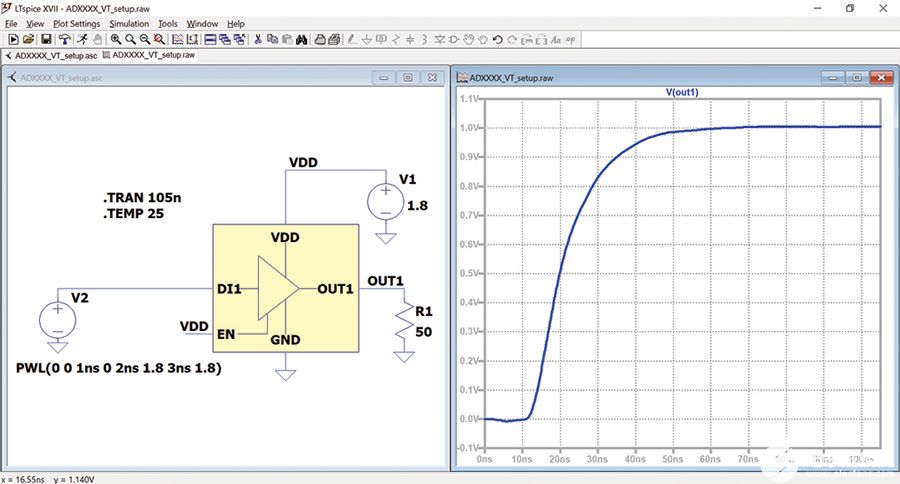

以地为参考的 50 Ω负载下的下降波形

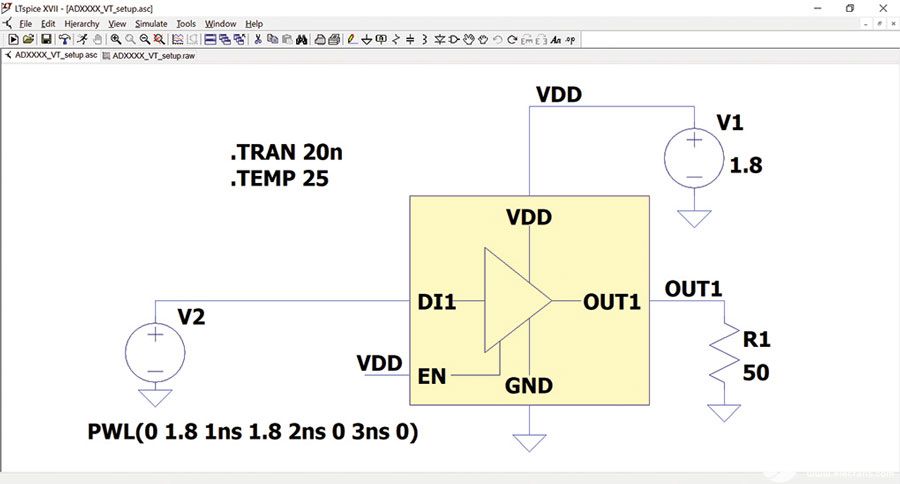

为了产生以地为参考的下降输出波形,需要一个下降沿输入,并且需要将50 Ω负载以GND为基准,如图20所示。得到的V-T波形如图21所示,其中输出建立于约16 ns至20 ns。需要注意的是,瞬态分析时间应该足以捕获下降波形的稳定。

图 20.ADxxxx设置,用于以地为参考的50 Ω负载的下降波形。

图 21.ADxxxx下降波形的结果,以地为参考50 Ω负载。

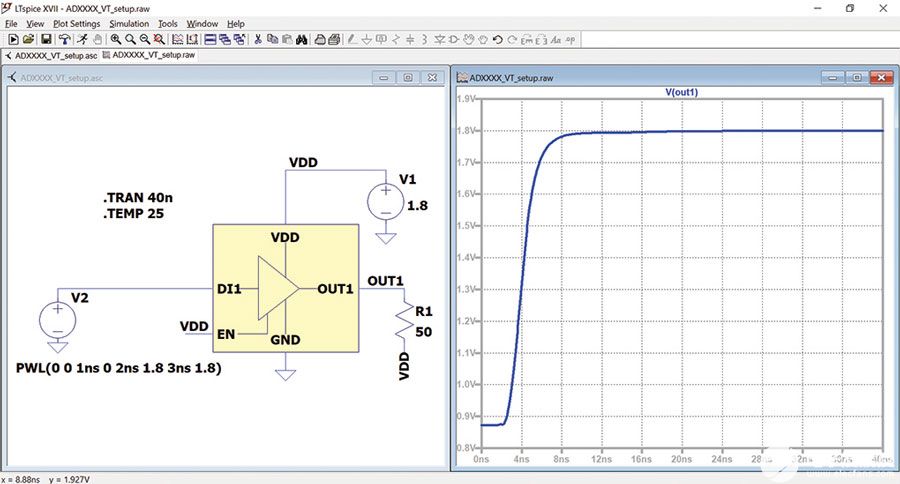

VDD 参考 50 Ω负载时的下降波形

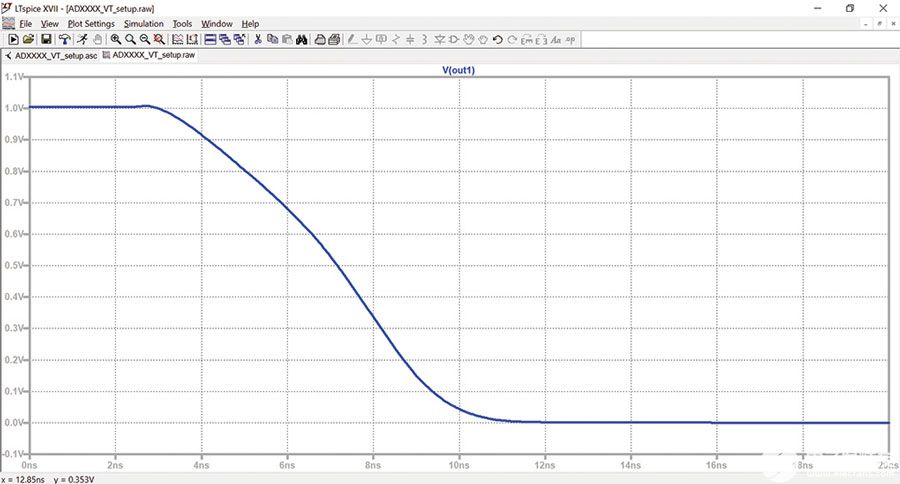

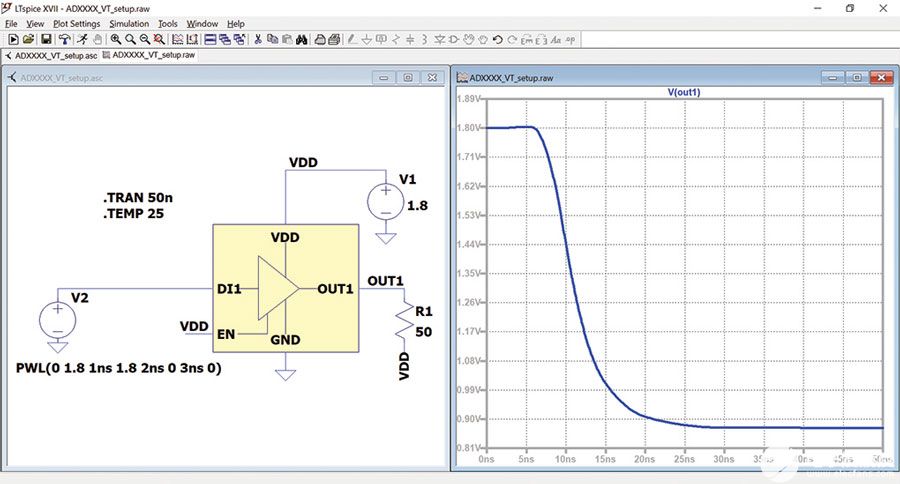

图22显示了VDD参考50 Ω负载的下降波形的设置和结果。如图所示,完全捕获输出的下降转换所需的瞬态时间为50 ns。

图 22.ADxxxx设置和DOUT1下降波形的曲线图,VDD参考50 Ω负载。

以地为参考的 50 Ω负载下的上升波形

对于上升波形,使用了PWL信号形式的上升沿输入激励。在图23中,设置显示了相对于地连接到输出引脚的负载电阻,这将产生对地负载上升的V-T数据。

图 23.ADxxxx设置和DOUT1上升波形的曲线图,以地为参考50 Ω负载。

以地为参考的 50 Ω负载下的上升波形

使用了相同的上升沿输入激励,但需要以VDD为基准的50 Ω。

检查V-T数据正确性的一种方法是查看逻辑低电压和逻辑高电压。VDD参考波形应具有相同的逻辑低电平和逻辑高电压电平,逻辑高压应与VDD相同。另一方面,以GND为参考的波形也应具有相同的逻辑低电压和逻辑高电压,逻辑低电压电平应约为0 V。

图 24.ADxxxx设置和DOUT1上升波形的曲线图,VDD参考50 Ω负载。

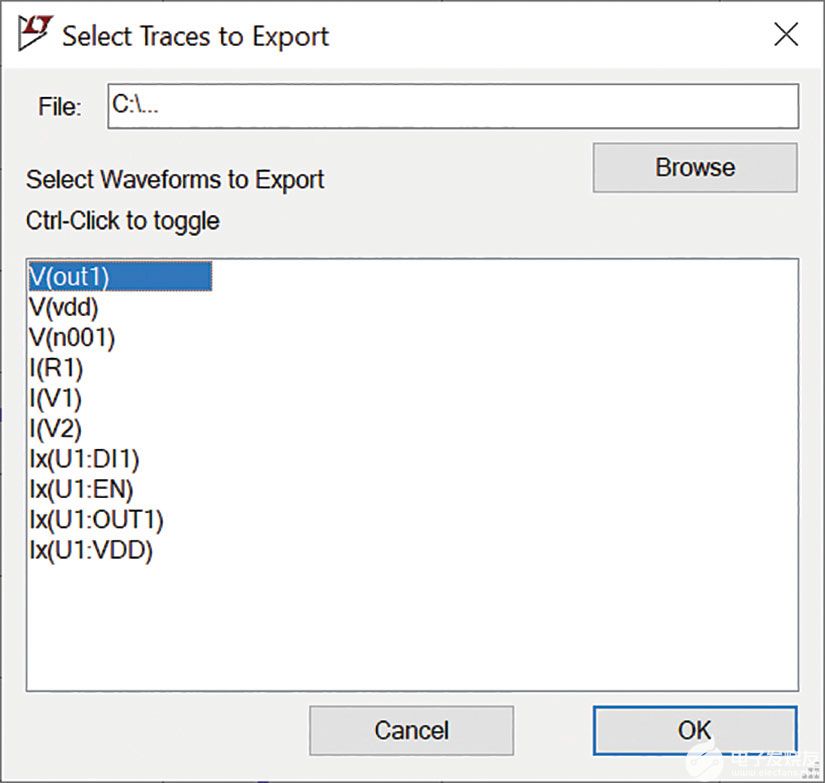

导出波形

然后,必须通过执行以下步骤来保存从四个设置中提取的V-T波形:

右键单击绘图。

将鼠标悬停到文件,然后单击将数据导出为文本。

图 25.将LTspice图保存为文本文件。

选择要导出的波形以及要导出的目录。

图 26.选择跟踪并设置保存目录。

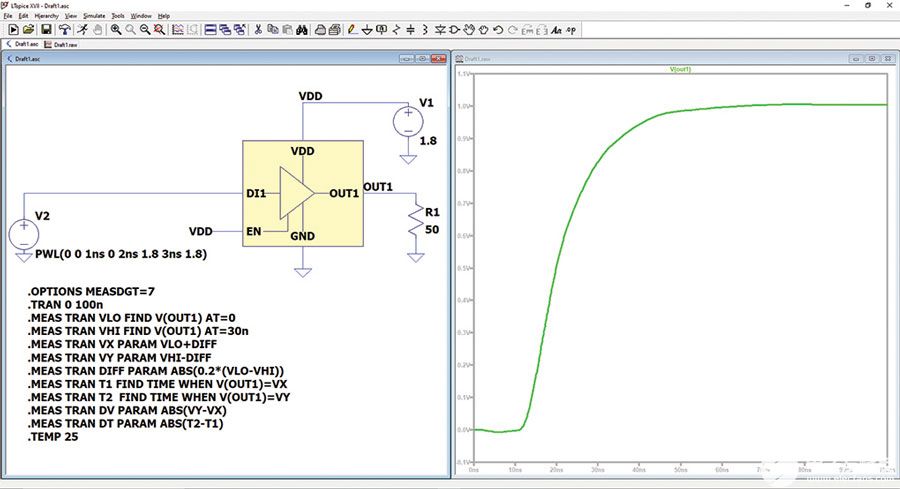

使用LTspice的斜坡数据提取

[Ramp] 关键字是在上升或下降过渡边沿的 20% 到 80% 处采集的上升和下降 VT 数据的斜坡速率 (dV/dt) 表示。这种方法可以在LTspice上实现,因为它能够使用.MEAS 和 .参数指令。斜坡提取过程可以通过在VT波形设置上添加SPICE指令来完成。这意味着可以同时提取斜坡和VT波形。

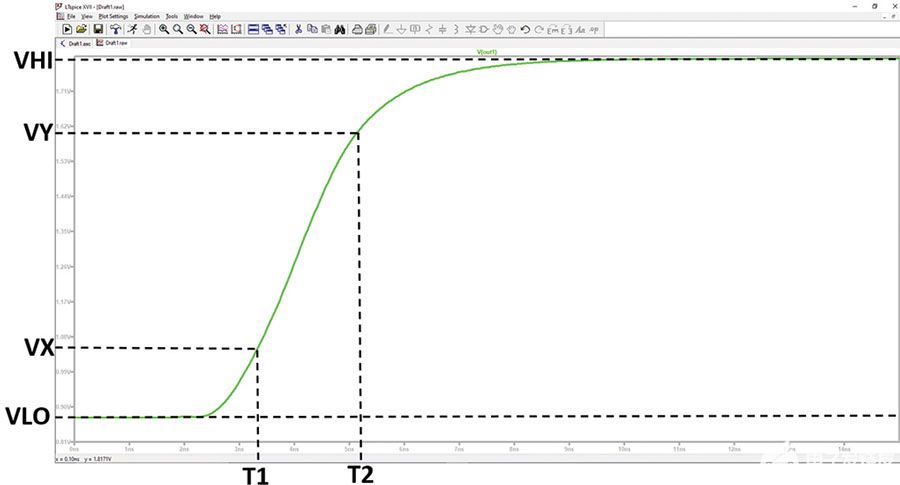

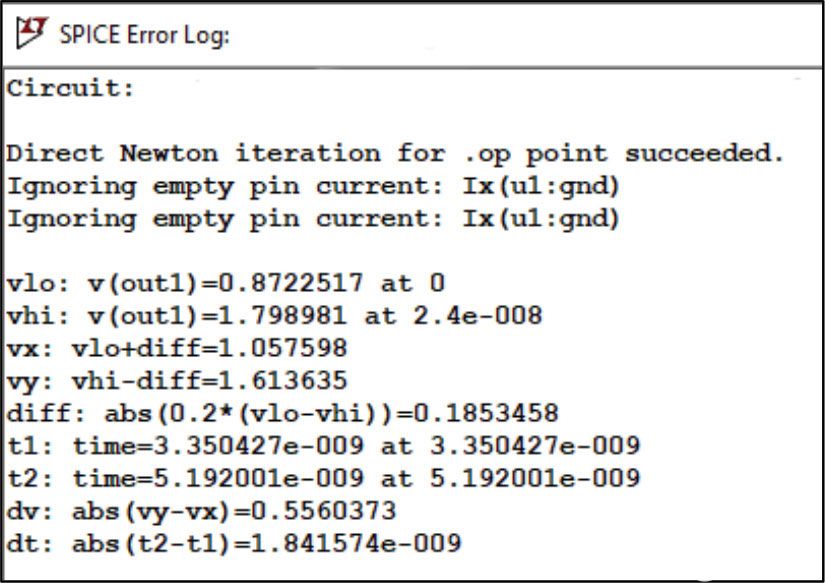

图27显示了上升波形斜坡计算的设置。为了计算下降波形的斜坡,VLO和VHI的时间值应该互换,因为下降斜坡的输出波形从缓冲器的逻辑高电平开始,然后过渡到逻辑低电平。

图 27.ADxxxx VT设置,带有用于上升波形斜坡提取的附加指令。

用于斜坡提取的LTspice指令

用于斜坡提取的 SPICE 指令是: 。TRAN,这是用于VT上升/下降波形的SPICE指令;选项,将将显示在 SPICE 错误日志上的输出设置为笛卡尔模式,并将其限制为所需的有效位数;和。MEAS,用于斜坡的实际计算。

VLO:表示逻辑低电压。

VHI:表示逻辑高压。

Diff:表示跃迁的20%点处的电压,该电压将分别与VLO和VHI参数相加和相减,以获得跃迁的20%和80%点。

VX 和 VY:表示上升/下降过渡沿 20% 和 80% 点处的电压。

dV 和 dT:这些是 IBIS 模型的 [Ramp] 关键字的计算值。

图 28.上升斜坡波形说明。

图 29.用于斜坡速率计算的 SPICE 错误日志。

构建IBIS模型

所有提取的I-V和V-T数据都被编译到IBIS模型(.ibs)文件中。下面是IBIS文件的实际模板,用户可以将其用作构建IBIS模型的参考。

一个.ibs文件以[IBIS Ver]关键字开头,后跟其文件名和修订号。IBIS 版本 3.2 将在 [IBIS Ver] 关键字中使用,因为它是建模 3 态输出缓冲区所需的最低版本。.ibs 文件的文件名和 [文件名] 关键字中的文件名应相同;否则,解析器会将其检测为错误。此外,文件名不应包含任何大写字母,因为分析器只允许在文件名中使用小写字母。其他重要的关键字将在本节的后半部分讨论。

.ibs 文件的下一部分包括 [组件]、[制造商]、[包] 和 [Pin] 关键字。ADxxxx有两个输入缓冲器(DIN1和EN)和一个输出缓冲器(DOUT1),因此其IBIS模型总共有三个缓冲器模型。[Package] 关键字通过 RLC 封装寄生值用作器件的封装模型。所有设备缓冲区的型号名称都在 [Pin] 关键字下定义,该关键字类似于命名变量,并在 [Model] 关键字下定义。

在 .ibs 文件的下一部分,使用测量的 I-V 和 V-T 数据对器件的数字缓冲器进行建模。缓冲区模型的内容因 Model_type 变量中指定的缓冲区类型而异。由于模型cmos_di1是输入缓冲区,因此其缓冲区模型仅包含C_comp、[Power_Clamp] 和 [GND_Clamp] 数据。输入缓冲器模型还包括其VINH和VINL值,这两个值都可以在器件数据手册中找到。鉴于DIN1和EN都是输入缓冲器,它们的缓冲器模型具有相同的结构。

另一方面,3 态缓冲区模型包含一些类似于输入缓冲区模型但具有附加 I-V 和 V-T 数据的关键字。cmos_out1的缓冲模型包括一个额外的子级仪表Cref(代表输出容性负载)和Vmeas(表示参考电压电平)。通常,使用的 Vmeas 是 VDD 值的一半。

除了C_comp、[Power_Clamp] 和 [GND_Clamp] 之外,三态缓冲区还有其他 I-V 数据:[上拉] 和 [下拉]。

最后,所有IBIS模型都应使用[结束]关键字关闭。

IBIS模型验证

如本系列文章的第一部分所述,IBIS模型验证由解析器测试和关联过程组成。这些是确保IBIS文件符合IBIS规范并且模型性能接近参考SPICE模型的必要步骤。

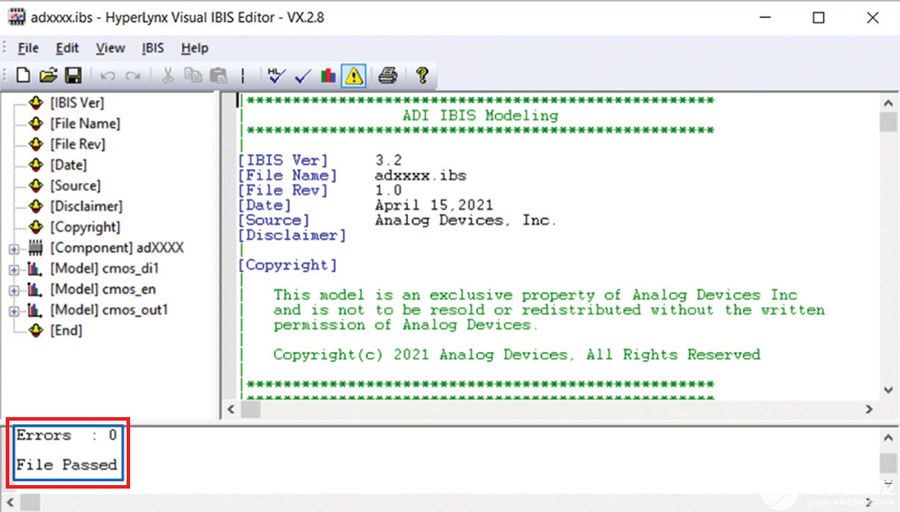

解析器测试

在上一节中创建的IBIS文件应首先经过解析器测试,然后再进入关联过程。ibischk是用于检查IBIS文件的黄金解析器。这将检查IBIS文件是否符合IBIS协会设定的规范。更多详细信息可在 ibis.org 在撰写本文时,使用的最新解析器是 ibischk 版本 7。

在执行解析器测试时,最好使用集成了ibischk的IBIS模型编辑软件,例如Cadence模型完整性和Hyperlynx可视化IBIS编辑器。这些工具便于检查语法。但是,如果用户没有其中任何一个,则可执行代码在 ibis.org 是免费的。它是在各种操作系统上编译的,因此用户不必担心使用哪种操作系统。

关联程序

在此验证阶段,需要检查IBIS模型的性能是否与参考(在本例中为SPICE模型)相似。表7显示了从0级到3级的不同IBIS质量等级。它描述了IBIS模型对参考的准确性,具体取决于它所经历的测试。在这种情况下,由于参考是ADxxxx SPICE模型,因此生成的IBIS模型可以符合2a级。这意味着它通过了解析器测试,具有数据手册中描述的正确且完整的参数集,并且通过了相关过程。

| 质量水平 | 描述 |

| 级别 0 | 通过黄金解析器(伊比施克) |

| 级别 1 | 按照清单文档中的定义完成且正确 |

| 2a 级 | 与仿真相关 |

| 2b 级 | 与测量相关 |

| 级别 3 | 以上所有内容 |

要将IBIS模型与参考SPICE模型相关联,可以遵循一些常规步骤。图 30 的流程图总结了这些内容。

图 30.IBIS到SPICE模型相关性的流程图。

设定品质因数

相关性的基础是,在相同的加载条件和输入激励下,IBIS模型的行为应与SPICE模型数字接口相同。这意味着它们的输出理论上应该直接位于彼此之上。一般来说,有两种方法可以描述IBIS模型输出与SPICE模型参考的接近程度:定性和定量方法。用户可以采用这两种方法来确定IBIS模型与SPICE模型的关联关系。

定性FOM测试利用用户的观察结果。它涉及对两个输出的目视检查,以确定相关性是否通过。这可以通过叠加IBIS和SPICE的输出结果来完成,并使用工程判断来确定图形是否相关。它可以作为相关性的初步测试,然后再进行定量FOM测试。当接口以相对较低的频率或比特率运行时,此测试就足够了。

另一个定性FOM测试在IBIS IO缓冲器精度手册中介绍,即曲线包络指标。它使用由过程电压温度极端值定义的最小和最大曲线。最小曲线和最大曲线用作相关性的边界。为了达到及格分数,IBIS结果上的所有点都应落在最小和最大曲线内。此方法不适用于本文,因为这仅限于典型条件。

定量FOM测试使用数学运算来衡量IBIS与SPICE的相关性。曲线叠加指标也出现在IBIS IO缓冲精度手册中,它使用IBIS和SPICE输出的数据点。它计算IBIS和参考数据点之间x轴或y轴差异的绝对值之和除以轴中使用的总范围与点数的乘积。公式3对此进行了说明,适合作为本文用例中的相关方法。但是,还有其他因素需要考虑。公式3中给出的FOM要求IBIS和SPICE的结果应映射到公共x-y网格上,这将使用数值算法和插值方法。如果用户想要进行快速定量FOM测试,本文介绍了另一种方法,即曲线面积度量,它使用曲线和x轴限定的区域。

曲线面积度量以SPICE结果为参考,比较IBIS曲线下计算面积。它的定义见公式4。但是,在进行曲线面积度量测试之前,需要创建的模型通过定性测试。这确保了IBIS和SPICE曲线同相并相互叠加。在获取曲线下的面积时,用户可以使用梯形规则或中点规则等数值方法,因为IBIS和SPICE结果使用相同的方法。在使用此方法时,建议使用尽可能多的点,以更好地近似区域。

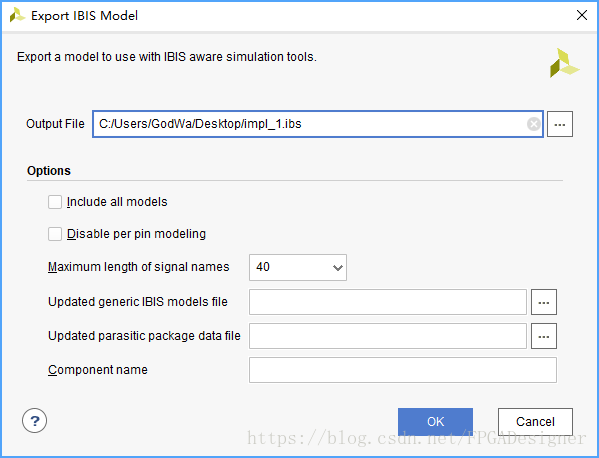

验证 ADxxxx IBIS 模型

IBIS模型验证的第一步是解析器测试。图 31 显示了使用 HyperLynx 可视化 IBIS 编辑器编写的 adxxxx.ibs IBIS 模型文件的解析器测试结果。当用户执行解析器测试时,目标是不接收任何错误。如果出现任何错误或警告提示,模型制作者需要修复它们。这保证了IBIS模型在仿真工具之间的兼容性。

图 31.ADxxxx 解析器测试结果。

下一步涉及设置 FOM 参数。本文仅限于使用定性FOM和曲线面积指标作为相关性度量。该测试将涉及IBIS和SPICE使用相同的负载条件和输入激励的瞬态响应曲线。计算出的曲线面积指标FOM应为≥95%才能通过相关性。DOUT1、DIN1 和 EN 的相关性在以下各节中显示。

杜特1

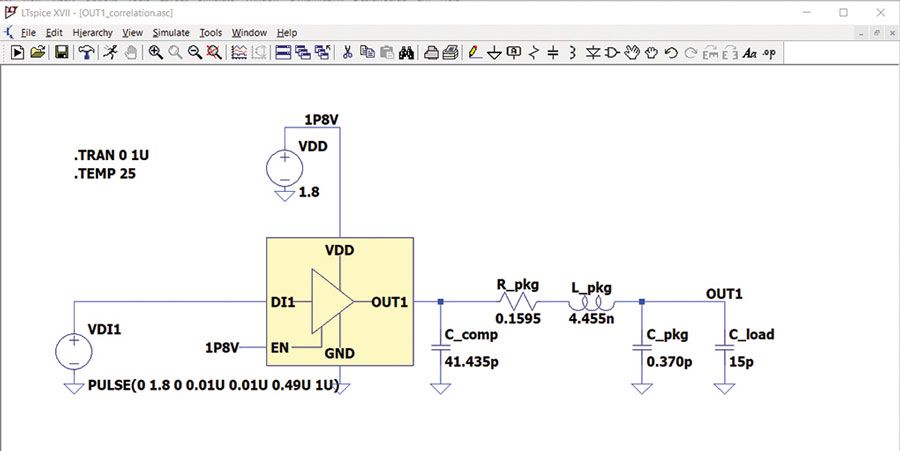

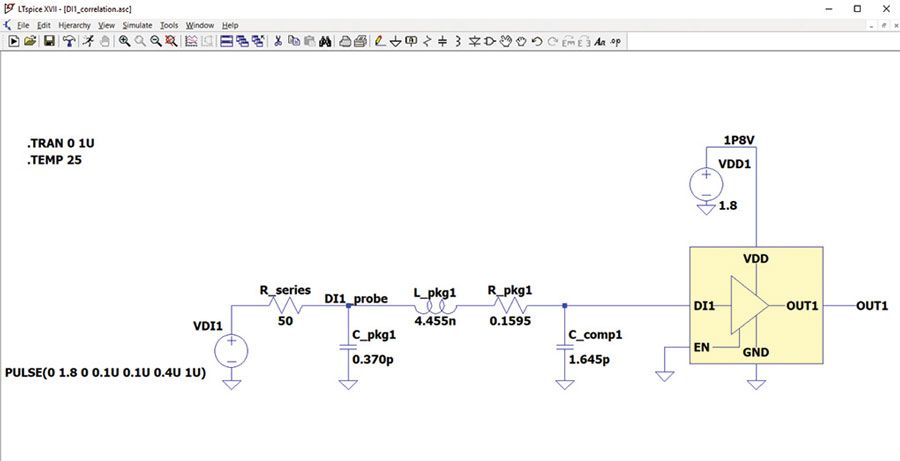

LTspice上用于DOUT1相关性的SPICE测试平台如图32所示。在原理图上放置了适当的电压电源以启用驱动器,并在DIN1引脚上放置一个脉冲信号源以驱动DOUT1。在LTspice中完成DOUT1驱动器模型需要额外的组件。C_comp代表芯片电容。将C_comp和C_load添加到LTspice模型后,放置RLC封装寄生效应(R_pkg、L_pkg、C_pkg)和C_load。

图 32.LTspice DOUT1相关测试平台。

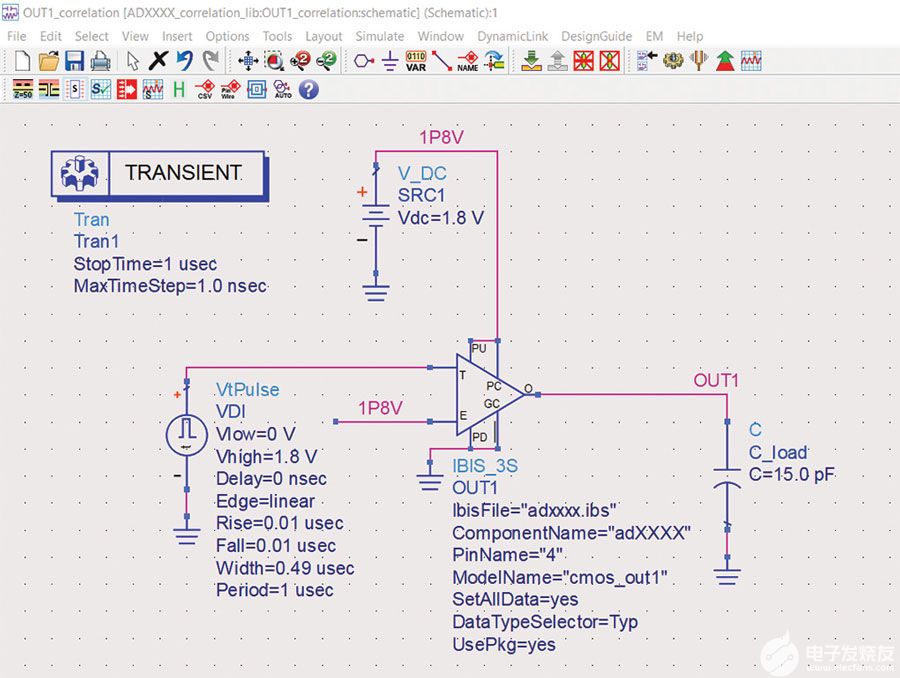

DOUT1 IBIS 模型相关性测试平台是在是德科技高级设计系统 (ADS) 上设置的,如图 33 所示。相同的输入激励、C_load、电压源和瞬态分析用作LTspice测试平台。但是,C_comp和RLC封装寄生效应未放置在ADS原理图上,因为它们已经包含在3态IBIS模块中。

图 33.ADS OUT1 相关测试平台。

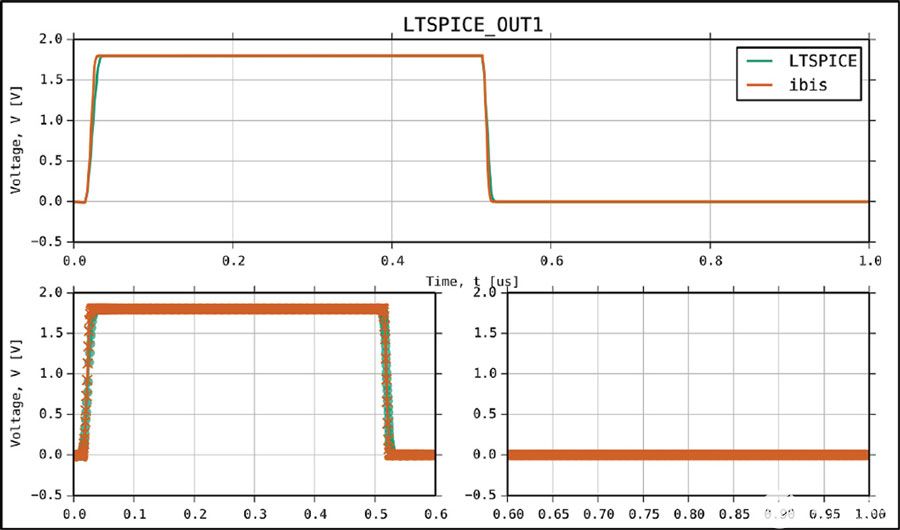

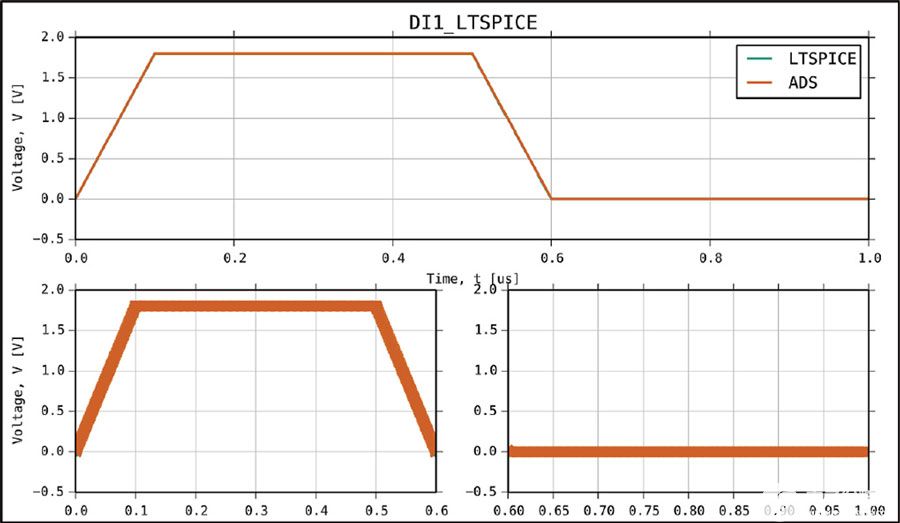

瞬态响应曲线是从C_load开始测量的。LTspice和ADS结果已被比较并相互叠加以进行定性FOM。如图34所示,LTspice和ADS DOUT1响应非常相似。差异可以用曲线面积度量来量化。曲线下的面积是在1 μs瞬态持续时间内计算的。计算出的曲线面积指标为 99.79%,满足设定的 ≥95% 通过条件。因此,DOUT1 IBIS模型与SPICE模型相关。

图 34.LTspice与IBIS模型OUT1响应。

DIN1 和 EN

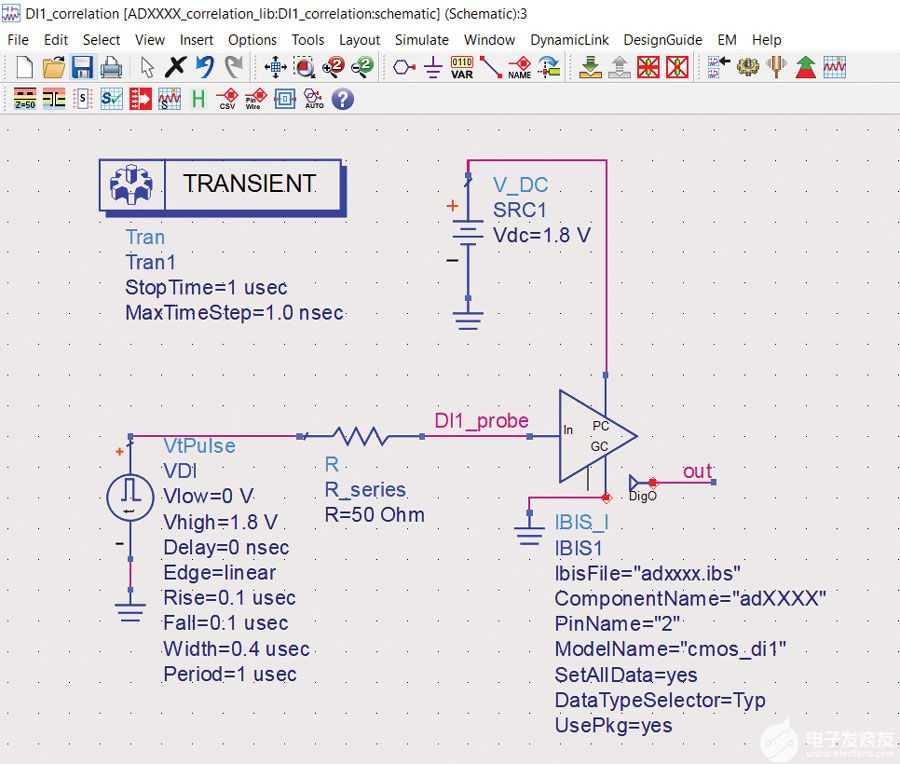

在验证输入端口时,LTspice和ADS的瞬态响应曲线将通过定性FOM和曲线面积指标相关联。LTspice中的测试平台如图35所示。这适用于 DIN1 和 EN 引脚。与DOUT1一样,提取的C_comp放置在DIN1端口,然后是RLC封装寄生效应。之后,连接一个50 Ω R_series电阻,后接一个输入激励脉冲电压电源。用于测量响应的探测点在DIN1_probe。

图 35.LTspice DI1 相关测试平台。

用于验证输入端口的是德科技 ADS 测试平台如图 36 所示。类似地,在输入端口之前放置一个R_series 50 Ω电阻,并使用相同的输入脉冲激励。未放置C_comp和RLC寄生效应,因为它们已经包含在IBIS模块中。用于测量瞬态响应的探头处于DI1_probe。

图 36.ADS DI1 相关测试平台。

LTspice和ADS的瞬态响应曲线相互叠加,用于定性FOM测试。如图37所示,曲线是相同的——LTspice曲线完全落后于ADS曲线。DI1 的计算曲线面积指标为 100%,满足设定的 ≥95% 通过条件。从EN引脚相关结果中也获得了相同的绘图和曲线面积度量。

图 37.LTspice与IBIS模型DI1响应。

结语

本文介绍了如何使用LTspice提取数据和构建IBIS模型的方法。它还提供了一种通过定性FOM和通过曲线面积度量定量FOM将IBIS模型与参考SPICE模型相关联的方法。这可以让用户确信IBIS模型的行为与SPICE模型类似。尽管本文未介绍其他类型的数字 IO,但提取C_comp、I-V 数据和 V-T 数据的过程可以作为创建其他类型的 IO 模型的垫脚石。

-

CMOS

+关注

关注

58文章

5710浏览量

235401 -

接口

+关注

关注

33文章

8574浏览量

151007 -

缓冲器

+关注

关注

6文章

1921浏览量

45473

发布评论请先 登录

相关推荐

为什么以及如何创建自己的IBIS模型

为什么以及如何创建自己的IBIS模型

评论