1:锁存器、触发器、寄存器的关联与区别

首先应该明确锁存器和触发器是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合逻辑电路的特性。

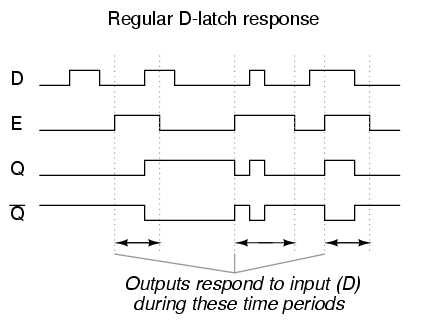

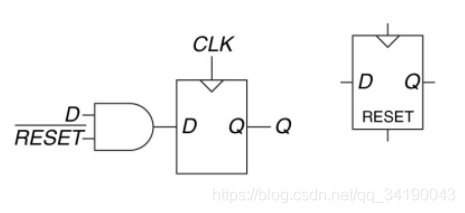

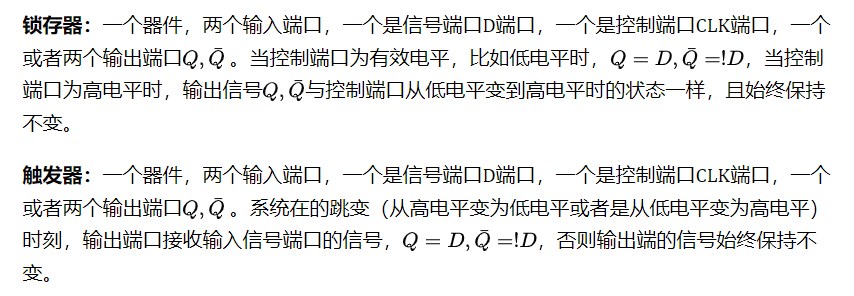

电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出

才会随着数据输入发生变化。(简单地说,它有两个输入,分别是一个有效信号EN,一个输入数据信号DATA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程)

-

-

-

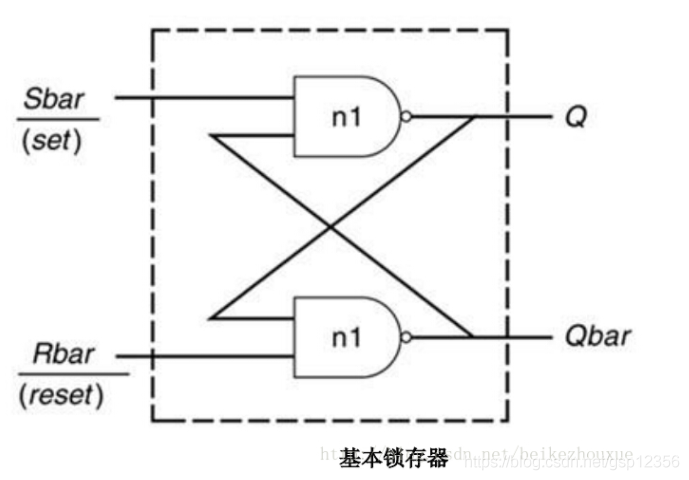

普通锁存器无控制信号:如基本RS锁存器,其无须时钟脉冲的触发。set为置数端,reset为复位端。

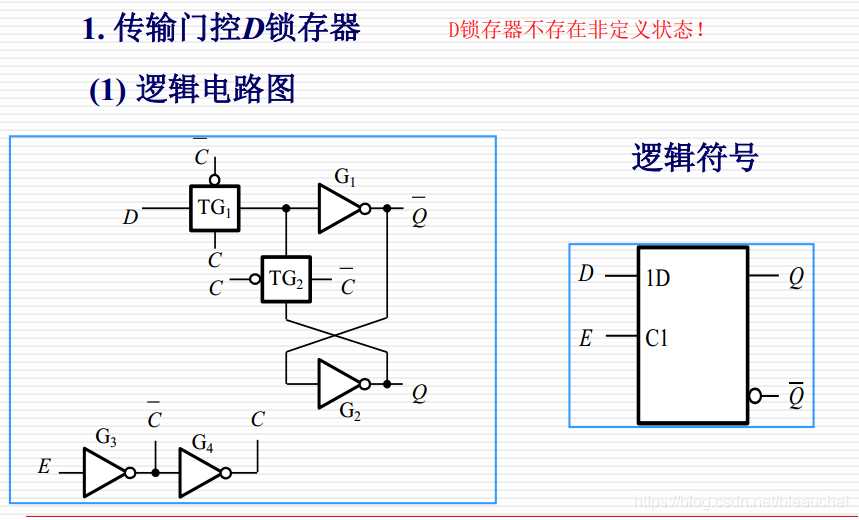

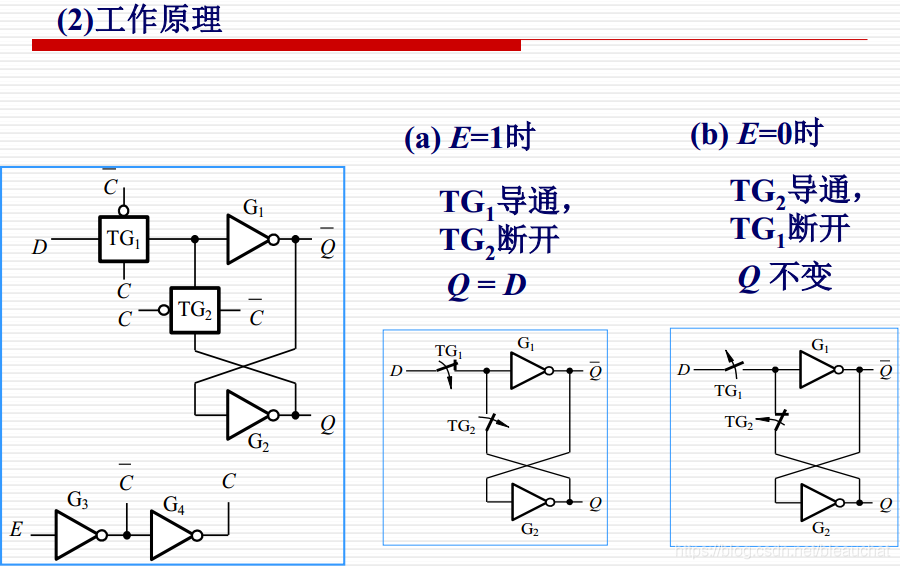

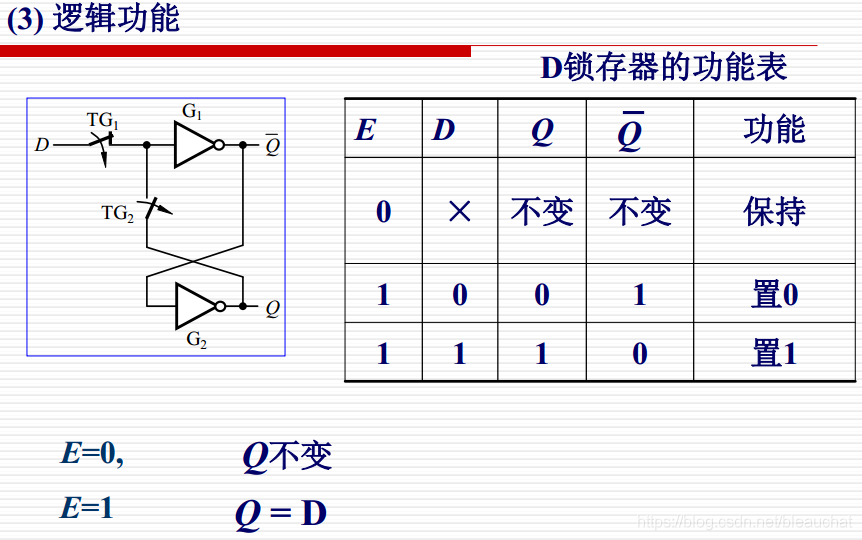

门控锁存器:门控D锁存器结构如下图所示。(E为使能信号,D为信号输入)

E为1时,C为1,TG1被1驱动导通,TG2被0驱动断开。(TG1为传输门,当C为1时,将输入端的vwin

信号整体传输之输出端,无损耗,C为0时门关闭)

应用场合:数据有效滞后于时钟信号有效,这意味着时钟信号先到,数据信号后到。在某些运算器电路中有时采用锁存器作为数据暂存器;

优点:面积小、锁存器比FF快,所以用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。

不用锁存器的原因有二:1、锁存器容易产生毛刺,2、锁存器在ASIC设计中应该说比FF要简单,但是在FPGA的资源中,大部分器件没有锁存器这个东西,所以需要用一个逻辑门和FF来组成锁存器,这样就浪费了资源;

(钟控 D 触发器其实就是 D 锁存器,边沿 D 触发器才是真正的 D 触发器)

触发器(Flip-Flop,简写为 FF)---对脉冲边沿敏感,其状态只在时钟脉冲的上升沿或下降沿的瞬间改变;

触发器也叫双稳态门,又称双稳态触发器,是一种可以在两种状态下运行的数字逻辑电路。触发器一直保持它们的状态,直到它们收到输入脉冲,又称为触发。当收到输入脉冲时,触发器输出就会根据规则改变状态,然后保持这种状态直到收到另一个触发;

-

触发器:我们把输出只在时钟某个时刻变化的玩意儿叫触发器。边沿敏感

-

-

-

这个便是一个d触发器。只在enable(一般大家都叫它clock)的上升沿q采样d,而且在每个时钟的上升沿都会采样。

主从触发器在时钟有效期内 (主触发器) 接收数据,在时钟边沿输出状态转换。

应用场合:时钟有效迟后于数据有效,这意味着数据信号先建立,时钟信号后建立,在CP有效沿时刻打入到寄存器;

边沿触发器在时钟边沿期间, 触发器才接收数据并使输出状态转换。

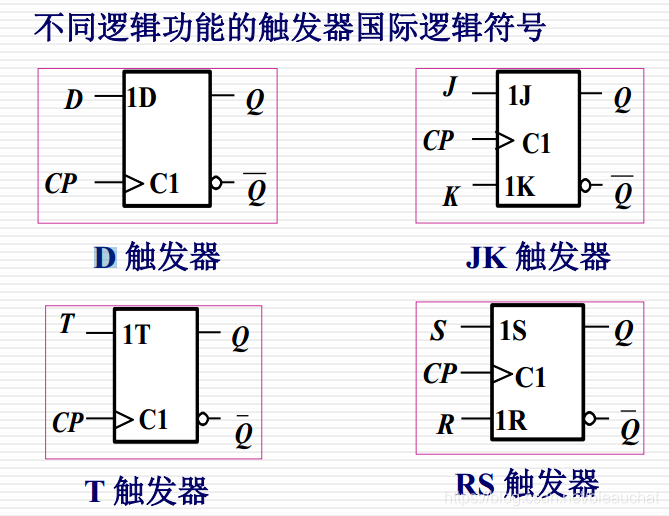

下面为常见的几种边沿触发器(符号中的“>”代表边沿触发,单是这个符号代表上升沿触发,如果在CP信号输入与边框的交界处还有空心则代表下降沿触发)

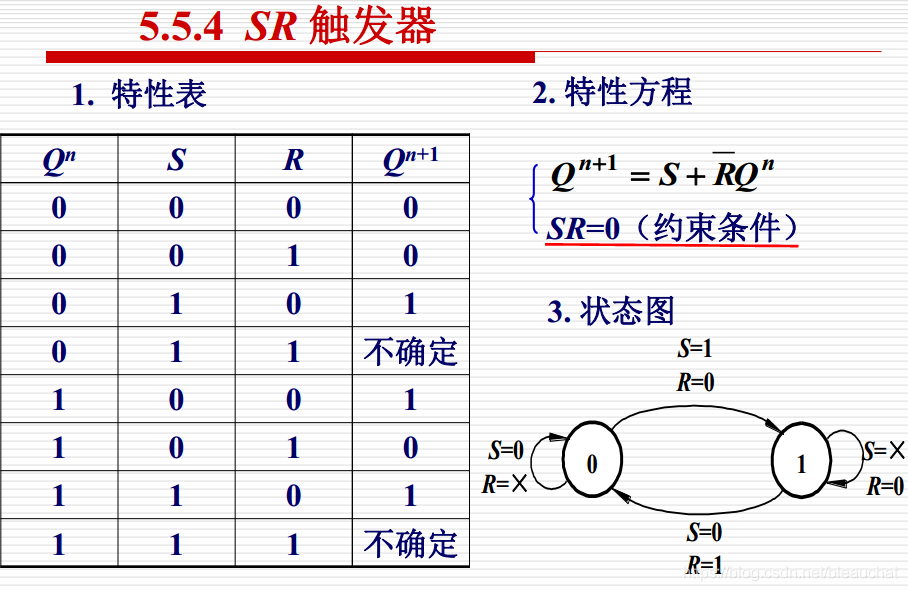

S为1时置1;R为1时清0;R与S都为0时,保持状态;R、S不能同时为1

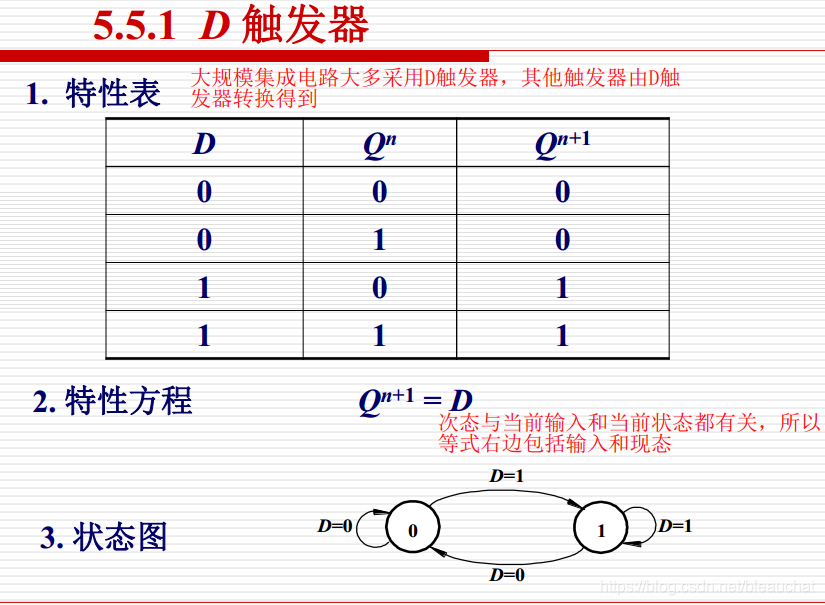

JK触发器的功能基本与RS触发器相同:J=1 K=0时,置1;J=0 K=1时,清零;J=0 K=0时,保持;J=1 K=1时,翻转(初态为0,次态为1;初态为1,次态为0)。

总结下锁存器的主要缺点:

(1)对毛刺敏感,不能异步复位,因此在上电后处于不确定的状态。

(2)锁存器会使静态时序分析变得非常复杂,不具备可重用性。(首先, 锁存器没有时钟参与信号传递,无法做 STA;其次,综合工具会将 latch 优化掉,造成前后仿真结果不一致)

(3)在 PLD芯片中,基本的单元是由查找表和触发器组成的,若生成锁存器反而需要更多的资源。根据锁存器的特点可以看出,在电路设计中,要对锁存器特别谨慎,如果设计经过综合后产生出和设计意图不一致的锁存器,则将导致设计错误,包括仿真和综合。因此,在设计中需要避免产生意想不到的锁存器。

总结一下避免生成锁存器的一些方法:

1)组合逻辑尽量使用assign语句描述组合逻辑电路。

2)时序逻辑电路不用担心生成锁存器,但也要尽量规避一些if-else 或者case不完整的情况,养成好的coding style.

3)如果采用case或者if结构描述组合逻辑时,应确保全部写全,不能遗漏。或者在组合逻辑块中先给输出变量赋初值。

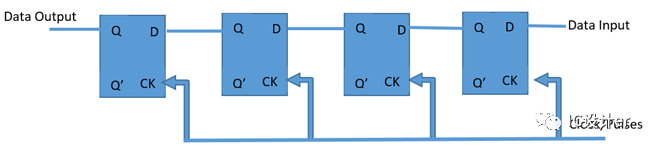

寄存器(register):用来暂时存放参与运算的数据和运算结果。在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。

区别与联系:由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。由于一个触发器能够存储一位二进制码,所以把 n 个触发器的时钟端口连接起来就能构成一个存储 n 位二进制码的寄存器。

从寄存数据的角度来讲,寄存器和锁存器的功能是相同的;它们的区别在于寄存器是同步时钟控制,而锁存器是电位信号控制。

寄存器一般是边沿触发的触发器,电路里叫register,而触发器就是楼上所说的各种逻辑门构成的包含电平触发和边沿触发的两种,而锁存器则是电平触发的。所以一般说来,我们只叫寄存器和锁存器两种,在时序电路中寄存器的作用就是只在时钟的边沿有效传输data(setuptime和hold time满足),而锁存器则在有效电平器件都可以传输data

寄存器(register):用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。工程中的寄存器一般按计算机中字节的位数设计,所以一般有8位寄存器、16位寄存器等;

-

寄存器这个玩意儿是一个概念层次的东西,1个寄存器就是能存1bit数据的东西。既可以用触发器实现也可以用锁存器实现。以触发器为例,由于触发器每个时钟上升沿都会采样,所以触发器会有一个反馈逻辑,当load有效的时候才会采样d,否则保持不变。

-

always @ (posedge clkornegedge rst_n)

-

-

-

-

-

2:RS锁存器、D锁存器、D触发器等边沿触发器的电路结构及其相应Verilog的描述(行为级、门级)

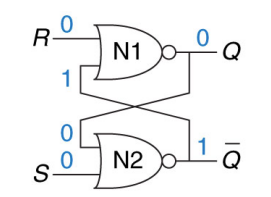

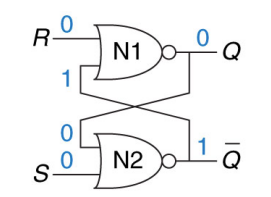

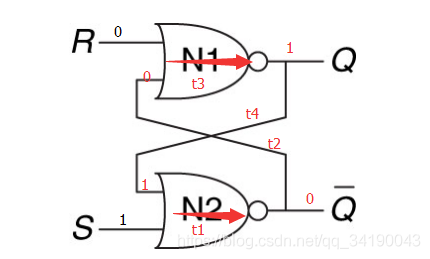

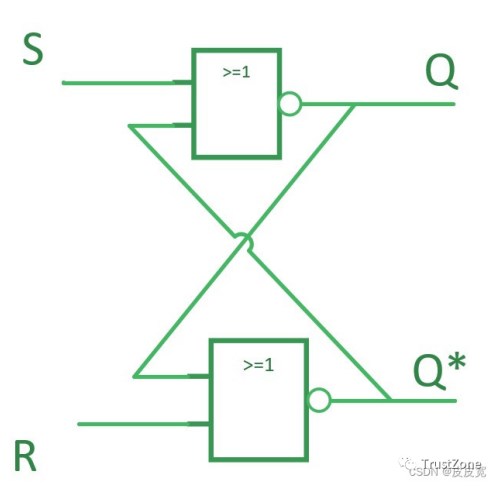

在数字电路里面,SR锁存器是最简单的时序单元,它由一对交叉耦合的或非门构成,如下所示:

主要功能就是通过输入的S、R端分别控制Q进行置位(set)和复位(reset)。下面我们就对这个电路的分析:

二输入或非门的功能是,只要有一个输入为1,输出就为了0。这SR锁存电路在正常情况下,输入RS的组合之一4种可能,即00、01、10和11,下面我们就来看看这4种输入对输出Q的影响:

A,假设原来的状态Q=0时,对应的原来状态就是Q’=1;那么N2的输入就是0和0,输出Q’=1,这样子就巩固了原来的状态Q’=1;Q’=1,对于N2,输入就是0和1,输出Q=0,也巩固了原来的状态,也就是与原来的假设一致。所以这个状态可以稳定下来,也就是当输入SR=00时,输出Q=1,Q’=0是可以存在的,如下图所示:

B,假设原来的状态Q=1时,对应的原来状态就是Q’=0;那么N2的输入就是0和1,输出Q’=0,这样子就巩固了原来的状态Q’=0;Q’=0,对于N2,输入就是0和0,输出Q=1,也巩固了原来的状态,也就是与原来的假设一致。所以这个状态可以稳定下来,也就是当输入SR=00时,输出Q=0,Q’=1是也是可以存在的,如下图所示:

由此可见,只要原来的状态一定了,那么输入SR=00时,输出也就是原来的状态。

根据或非门的功能,由于S=1,N2的输出Q’= 0;于是N1的输入就是00,输出Q就等于1;然后Q=1反馈回N2的输入,让N2的输出稳定为0,从而让Q的输出稳定为1;输入SR=10时,输出Q=1,称为置位功能。

(这里我们看一下,在SR=10时,S的信号稳定多久输出Q和Q’才稳定下来:S=1到来,首先经过N2的门延时t1,然后是Q’反馈回N1的线延时t2,接着是N1的门延时t3,再然后是Q反馈回N2的门延时t4,也就是有2个门延时和两个线延时,这是对于Q’的;对于Q还有增加一个N2门延时和一个Q’反馈回N1输入的线延时)如下图所示:

从上面的分析中,我们知道输入S=1,R=0时,输出Q=1,也就是置位的功能。

1.·当S=0,R=1时,这种情况跟SR=10类似,只不过是输出Q=0,也就是复位的功能。

2.·当S=1,R=1时,根据或非门的功能知道,输出Q=0,Q’=0。很显然这时候Q=Q’了,这跟我们给输出取值的字面意义是相反的,我们把这种状态称为错误输出,这是要注意的。这里需要说明的是,S和R都有效是没有意义的,锁存器不能同时被复位和置位,这样会引起输出都是0的混乱电路反应。

通过上面的分析,我们知道,SR锁存器可以具有锁存数据的功能:在S有效时,复位输出Q=1;在R有效时,输出复位Q=0;当S和R都无效时,就会保持前一个状态的输出。

同步RS锁存器:有r(复位),s(置位)。它的缺点在于会有不确定状态x。

-

moduleRS_Flip(clk,r,s,q,qb);

-

-

-

-

-

-

-

-

-

-

-

-

-

-

module RS_latch(r,s,q,qn);

-

-

-

-

-

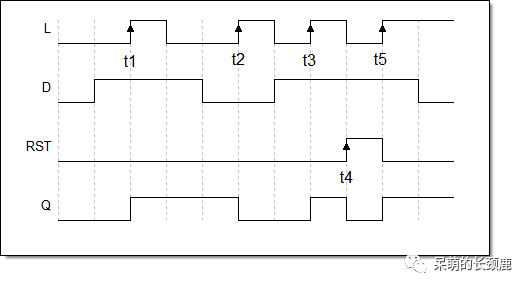

D锁存的功能是在时钟高/低电平的时候通过数据,在时钟低/高电平的时候锁存数据(这样就明确地说明了什么时候锁存什么数据,而不是像SR锁存器一样,不知道锁存什么数据),具体的结构图和分析如下所示:

D锁存器常见结构和电路符号图如下所示:

可以看到,D锁存器可以分为前级门电路(两个与门和一个非门)和后级SR锁存器组成,(PS:反相器2个晶体管,两个与门共12个晶体管,两个或非门共8个晶体管,D锁存器一个22个晶体管)下面我们就来分析一下它的功能:

输入是Clk(相当于第一节所展示电路图中的E)和D,也就是输入有四种可能:

·当clk=0时,红S红R都为0,也就是SR锁存器的输入为00,根据SR锁存器的功能,输出Q和Q’将保持原来的状态;因此clk=0时,不管D是什么,输出Q和Q’都不随D变化,只与原来的状态有关,也就是保持。

·当clk=1时,R=(1·D’)=D’;S=(1·D)=D。

也就是说,当clk=1的时候,SR锁存的输入是互补的,不会出现S和R同时有效的情况。当D=1时,S=1,置位有效,输出Q=1;当D=0时,R=1,复位有效,输出Q=0;因此就可以知道,在clk=1时,输出Q=D,也就是输出等于输入。

通过上面的分析,上面的D锁存器结构功能为:在clk=1时,数据通过D锁存器流到了Q;在Clk=0时,Q保持原来的值不变。这样的锁存器也称为透明锁存器或者电平敏感锁存器(这里需要注意的是,上面结构中电平敏感锁存器是高电平敏感,也是就是高电平有效,这里的有效不是指“锁存”的这个功能有效,而是指输出发生变化即输入信号得以传送到输出,方便后面的锁存操作)。然后低电平敏感的D锁存器的电路结构这里就不介绍了。

可以看到,D锁存器可以分为前级门电路(两个与门和一个非门)和后级SR锁存器组成,(PS:反相器2个晶体管,两个与门共12个晶体管,两个或非门共8个晶体管,D锁存器一个22个晶体管)下面我们就来分析一下它的功能:

输入是Clk(相当于第一节所展示电路图中的E)和D,也就是输入有四种可能:

·当clk=0时,红S红R都为0,也就是SR锁存器的输入为00,根据SR锁存器的功能,输出Q和Q’将保持原来的状态;因此clk=0时,不管D是什么,输出Q和Q’都不随D变化,只与原来的状态有关,也就是保持。

·当clk=1时,R=(1·D’)=D’;S=(1·D)=D。

也就是说,当clk=1的时候,SR锁存的输入是互补的,不会出现S和R同时有效的情况。当D=1时,S=1,置位有效,输出Q=1;当D=0时,R=1,复位有效,输出Q=0;因此就可以知道,在clk=1时,输出Q=D,也就是输出等于输入。

通过上面的分析,上面的D锁存器结构功能为:在clk=1时,数据通过D锁存器流到了Q;在Clk=0时,Q保持原来的值不变。这样的锁存器也称为透明锁存器或者电平敏感锁存器(这里需要注意的是,上面结构中电平敏感锁存器是高电平敏感,也是就是高电平有效,这里的有效不是指“锁存”的这个功能有效,而是指输出发生变化即输入信号得以传送到输出,方便后面的锁存操作)。然后低电平敏感的D锁存器的电路结构这里就不介绍了。

-

module d_latch(clk,d,q,qn);

-

-

-

-

-

-

RS_latch rs (s,r,q,qn);//RS锁存器中的所展示的门级描述

-

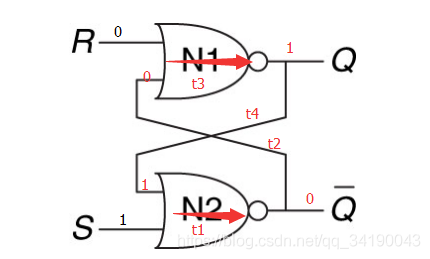

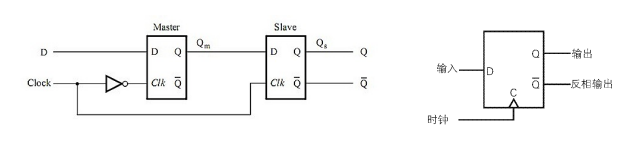

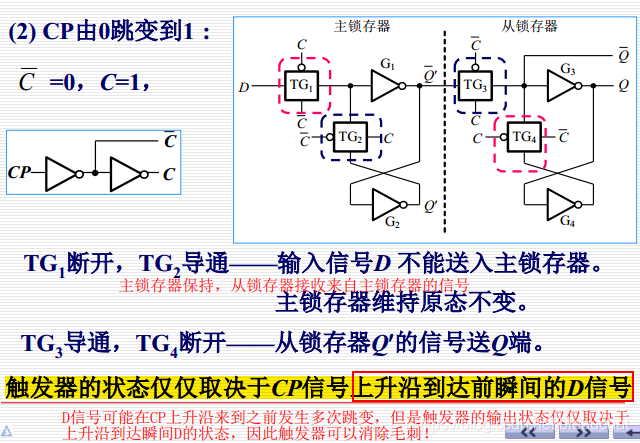

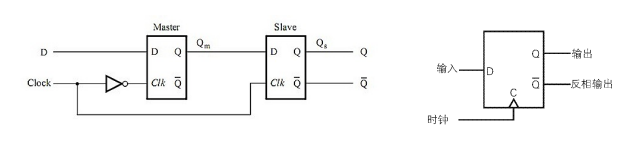

触发器有很多类型,比如J-K触发器、T触发器、D触发。前面我们也说了,锁存器的应用之一就是构成触发器,这里我们只聊最简单的触发器——D触发器,D触发器的结构和电路符号图如下所示:

D触发器可以由两个D锁存器构成,驱动时钟的相位相反(也就是),前面的D锁存器称为主锁存器,后面的D锁存器称为从锁存器,因此D触发器也可以称为主从触发器(PS:两个D锁存器共44个晶体管,非门2个晶体管,因此D触发器46个晶体管)。下面我们分析一下D触发的功能:

假设要传输的数据D=D1:在(clock简称clk)clk=0的时候,主锁存打开进行传输数据,把输入传送到从到从锁存器的输入端,即Qm = D1。然后clk从0→1的时候,主锁存器准备关闭,保持原来的值D1,与此同时从锁存器准备打开,把Qm的值传输到输出Qs,也就是Qs=Qm=D1。在clk=1的时候,主锁存器是关闭的,Qm保持D1不变,即Qm=D1;从锁存器是打开的,Qs=Qm=D1。接着clk从1→0的时候,主锁存器准备打开,准备传输数据;而从锁存器准备关闭。在clk=0的时候,主锁存打开进行传输数据,把输入传送到从到从锁存器的输入端,即Qm = D2;与此同时,从锁存器关闭,由于新的Qm即Qm还没有到达从锁存器的D端,因此在从锁存器关闭的时候,从锁存器锁存的是原来的值即D1,因此输出Qs =D1。然后接下来上升沿就传输D2…

从上面的分析可以找到,D触发器在时钟上升沿的时候锁存在时钟上升沿采到的值,并且保持一个时钟周期。这种在时钟上升沿锁存数据的触发器称为正边沿触发器,与此对应的还有负边沿触发的触发器,这里就不进行介绍了。

由D触发器延伸出去的知识点还有很多,比如寄存器,寄存器由多个D触发器构成(一个D触发器可以看做1位的寄存器);

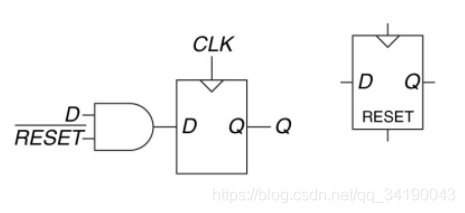

比如带使能的触发器:

D触发器可以由两个D锁存器构成,驱动时钟的相位相反(也就是),前面的D锁存器称为主锁存器,后面的D锁存器称为从锁存器,因此D触发器也可以称为主从触发器(PS:两个D锁存器共44个晶体管,非门2个晶体管,因此D触发器46个晶体管)。下面我们分析一下D触发的功能:

假设要传输的数据D=D1:在(clock简称clk)clk=0的时候,主锁存打开进行传输数据,把输入传送到从到从锁存器的输入端,即Qm = D1。然后clk从0→1的时候,主锁存器准备关闭,保持原来的值D1,与此同时从锁存器准备打开,把Qm的值传输到输出Qs,也就是Qs=Qm=D1。在clk=1的时候,主锁存器是关闭的,Qm保持D1不变,即Qm=D1;从锁存器是打开的,Qs=Qm=D1。接着clk从1→0的时候,主锁存器准备打开,准备传输数据;而从锁存器准备关闭。在clk=0的时候,主锁存打开进行传输数据,把输入传送到从到从锁存器的输入端,即Qm = D2;与此同时,从锁存器关闭,由于新的Qm即Qm还没有到达从锁存器的D端,因此在从锁存器关闭的时候,从锁存器锁存的是原来的值即D1,因此输出Qs =D1。然后接下来上升沿就传输D2…

从上面的分析可以找到,D触发器在时钟上升沿的时候锁存在时钟上升沿采到的值,并且保持一个时钟周期。这种在时钟上升沿锁存数据的触发器称为正边沿触发器,与此对应的还有负边沿触发的触发器,这里就不进行介绍了。

由D触发器延伸出去的知识点还有很多,比如寄存器,寄存器由多个D触发器构成(一个D触发器可以看做1位的寄存器);

比如带使能的触发器:

带复位的触发器:

-

module D_flip_flop(clk,d,q,qn);

-

-

-

-

d_latch dlatch1(~clk,d,q0,qn0);//d_latch来源于上节

-

d_latch dlatch2(clk,q0,q,qn);

-

其他边沿触发器的行为级描述

-

-

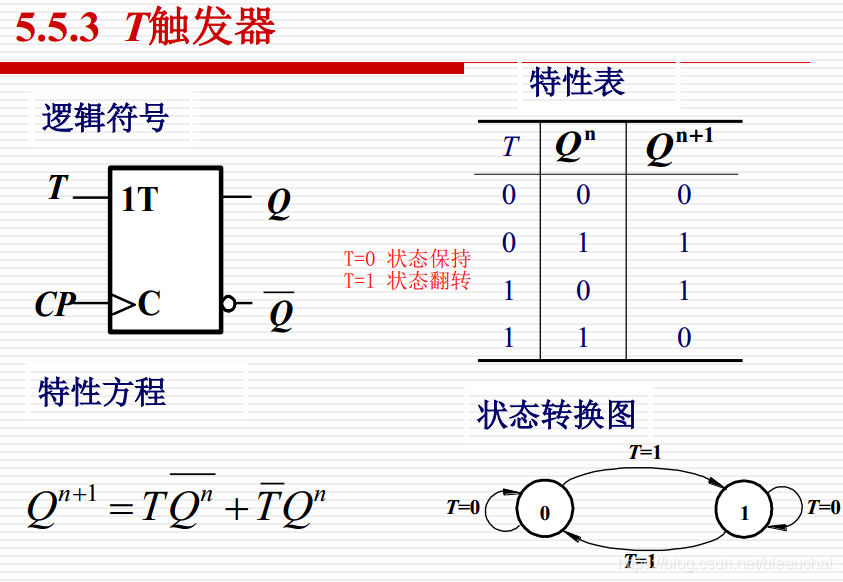

在时钟沿到来的时候若T为0,那么触发器输出不变。如果为1,则输出反转。

-

moduleT_Flip(clk,rst,t,q,qb);

-

-

-

-

-

-

-

-

-

-

else;//本来应该有保持与翻转两种,但q不变其实就不需要给出?

-

-

-

-

moduleD_Flip(clk,rst,d,q,qb);

-

-

-

-

-

-

-

-

-

-

-

-

-

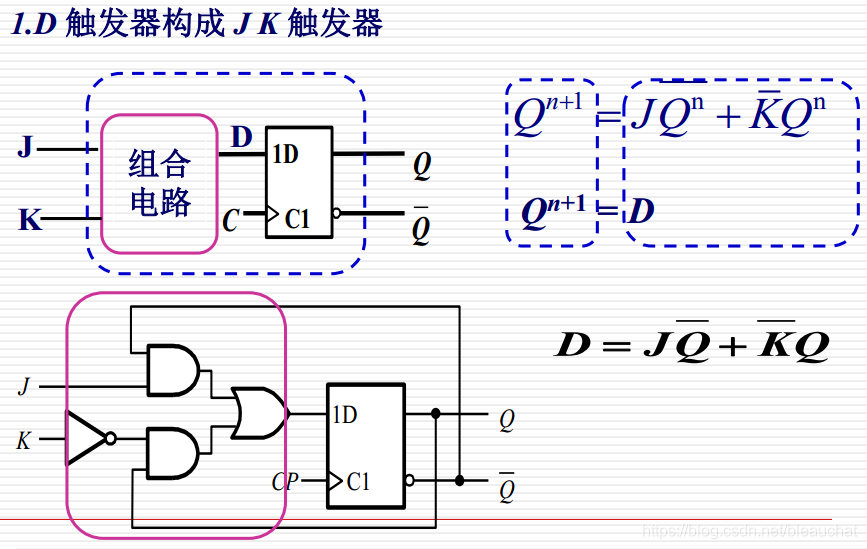

处于时钟沿触发时当JK为00,01,10时和RS触发器一样,当为11时和T触发器一样。

moduleJK_Flip(clk,j,k,q,qb);

inputwireclk,j,k;

outputwireqb;

outputregq;

assignqb=~q;

always@(posedgeclk)begin

case({j,k})

2'b00:

q<= q;

2'b01:

q<= 0;

2'b10:

q<= 1;

2'b11:

q<= ~q;

endcase

end

endmodule

至芯科技12年不忘初心、再度起航12月17日北京

中心FPGA

工程师就业班开课、线上线下多维教学、欢迎咨询!

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

锁存器、触发器、寄存器的关联与区别及其相应的verilog描述

锁存器、触发器、寄存器的关联与区别及其相应的verilog描述

评论