作者:Ian Collins and David Mailloux

多年来,微波频率生成给工程师带来了重大挑战,需要深入了解模拟、数字和射频 (RF) 以及微波电子学,特别是锁相环 (PLL) 和压控振荡器 (VCO) 集成电路 (IC) 组件,同时还需要可调谐滤波、宽带放大和增益均衡。

本文重点介绍了近年来微波电路设计的进步,这意味着硅技术的低相位噪声VCO可以覆盖一个倍频程范围。同一 IC 上的集成输出分频器允许几个倍频程的较低频率覆盖,而乘法器允许使用单个 IC 产生高达 32 GHz 的频率。小数N分频PLL频率合成器的进步意味着微波频率下的整体均方根抖动可以低至60 fs,具有极小的频率分辨率和最小的杂散音。低插入损耗宽带滤波器可与这些集成的PLL/VCO IC配合使用,以改善整个系统的频谱性能,从而大大简化微波和毫米波本振生成的挑战。

介绍

本振 (LO) 是现代通信、汽车、工业和仪器仪表应用中的重要组成部分。无论是从基带到RF的上变频或下变频频率,反之亦然,为汽车雷达应用生成斜坡频率,材料检测,还是开发仪器来构建和测试这些应用的电路,LO都存在于我们生活的许多方面。电路和工艺技术的进步有助于降低此类电路的成本、复杂性和面积,与过去相比,现代集成电路大大简化了LO的设计工作,因为过去需要更多样化的有源和无源技术组合。

过去,GSM等2G通信应用的大多数LO使用类似于ADI公司ADF4106的整数N分频PLL,以及窄带T封装VCO(例如VCO190-1846T)。在大多数情况下,这些VCO的高质量因数(Q)使其非常适合满足该标准苛刻的相位噪声规格。当时的手机通常只支持一种无线标准,而该标准本身的数据速率有限(尽管2G网络实现的出色覆盖范围帮助手机赢得了广泛的市场认可)。基站LO往往是使用各种IC和VCO子模块组装的模块。

对无线数据速率和与不同全球无线标准的兼容性的更大需求推动了宽带VCO的发展,这将促进更广泛的频率覆盖范围,并支持比使用窄带VCO更多的新可用频谱。支持这种数据吞吐量的微波回程网络也面临着支持更高阶调制速率的压力,并且针对不同的范围和标准进行了更多的配置,以使网络提供商能够减少工程工作并提高投资回报率。为了支持这些网络的发展,典型的信号分析仪使用大而重的钇铁石榴石(YIG)振荡器和滤波,采用类似的笨重技术。

VCO 改进

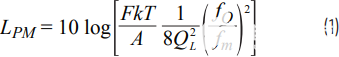

开发集成硅微波VCO的最大技术挑战是可用晶圆制造工艺的Q值有限。在许多情况下,Q值会从绕线电感器(用于T型封装VCO)的典型值100s下降到略高于10,由于Leeson方程施加的限制,严重影响相位噪声,其中相位噪声L下午(公式1)与较高的VCO Q值和较低的频率范围呈平方反比关系。

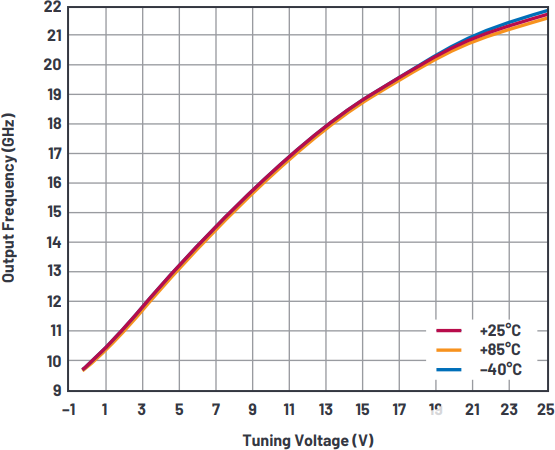

基于砷化镓(GaAs)或硅锗(SiGe)制造的宽带单核VCO通过将VCO的调谐端口范围从5 V(通常可从大多数硅基PLL电荷泵获得)扩展到15 V甚至30 V,解决了范围与噪声的问题。这意味着谐振器Q可以保持不变,但扩展的变容二极管可调谐性提供了更宽的调谐范围,而不会降低相位噪声。这种更高的调谐范围带来了一个挑战,即使用有源低通滤波器将电荷泵电压(通常为5 V)转换为15 V或30 V(参见图2中HMC733的调谐范围)。这些有源滤波器需要高电压、低噪声运算放大器。因此,典型的微波LO由PLL(ADF4106)和运算放大器、GaAs VCO组成,在许多情况下,还包括一个额外的外部分频器,用于将VCO信号分频到PLL的最大允许输入频率(ADF4106为6 GHz)。砷化镓VCO通常在S波段及更高频段工作,因为谐振器电路通常在2 GHz以上提供最佳性能。在设计电路板时需要非常小心和关注, 这需要电源方面的高度专业知识, vwin , 射频和微波领域.设计PLL滤波器并仿真其性能需要大量的控制理论和噪声建模经验,并且熟悉每个单独的组件。完成这组任务所需的经验并不容易获得,并且往往由具有数十年硬件设计经验的资深人士获得。

图2.HMC733调谐范围。

有许多技术可以解决低Q值问题。在ADF4360等器件系列中,芯片顶部的焊线(连接到焊盘)的Q因数为~30。厚金属电感器也改善了Q值,变容二极管Q的改进极大地提高了谐振器Q值,并进一步改善了相位噪声。用于高频VCO和N分压器电路的BiCMOS工艺,以及用于切换各种电容器的各种CMOS逻辑电路,意味着宽带PLL和VCO IC是可行的,其更小的尺寸和更宽的频率范围导致它们在无线市场上迅速采用。

许多宽带LO都采用了这种方法。覆盖整个倍频程范围的VCO是非常有利的,因为一组分频器允许产生仅受最低可用VCO频率和最高可用分频器比限制的频率。硅工艺VCO设计的一个重大突破是将VCO范围分解为子带,通过切换不同的电容器组来实现。这允许覆盖更宽的频率范围,而无需通过降低振荡器谐振器Q来牺牲相位噪声,同时还允许使用较低电压的电荷泵,无需使用额外的运算放大器,这也需要更高的电源电压轨。进一步的增强功能将VCO频段的数量从数十个增加到数百个,甚至在单芯片IC上开发了额外的独立重叠VCO内核,根据需要切换,从而可以进一步优化相位噪声,如ADF4371(图3)。图2中HMC733的单核VCO与ADF4371的多频段VCO之间形成了鲜明的对比。

图3.ADF4371频率与V的关系调整.

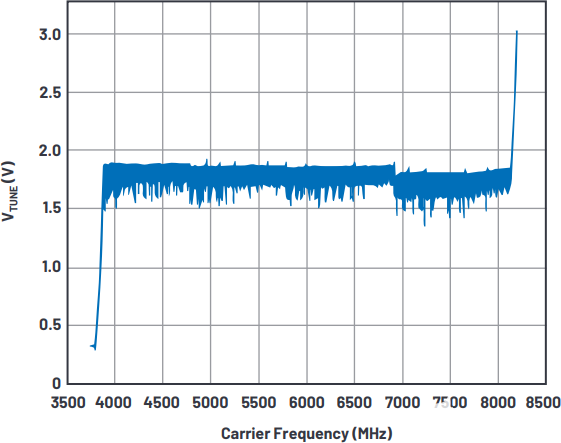

在频率与 V 上调整图中,HMC733调谐电压与输出频率成正比,而在图3中,调谐电压基本上在目标V的几百毫伏以内调整1.65 V。 智能频段选择逻辑或自动校准电路意味着用户不需要开发频率频段查找表,并且有足够的裕量来保证在电源范围内,特别是温度电压范围内可靠运行。

锁相环改进

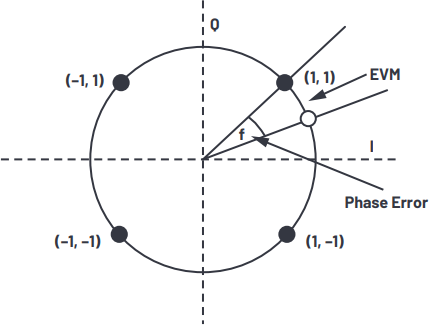

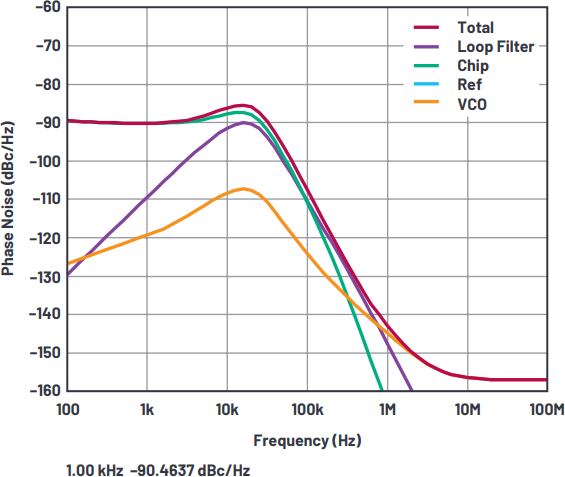

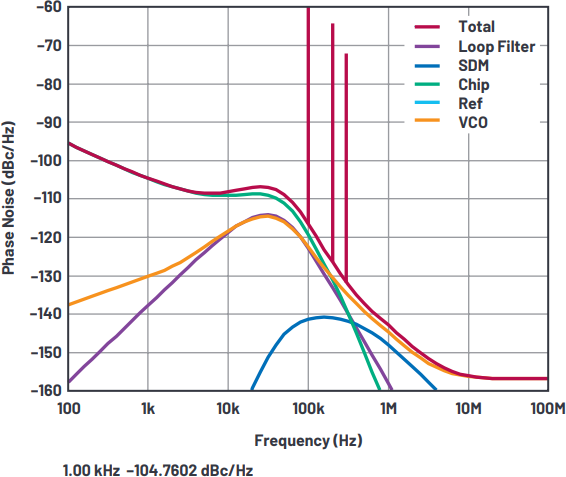

对更高数据速率的需求需要更低的误差矢量调制(EVM)速率(图4),这主要是由窄带无线应用中PLL频率合成器的带内相位噪声贡献决定的,使用200 kHz信道光栅的1.8 GHz输出所需的高N(9000)意味着由于N分频器的20log(N)贡献而导致严重的带内损失。64 QAM等更高阶调制速率需要更低的EVM,这推动了ADF4153A和ADF4193等小数N分频频率合成器的开发、采用和部署,这些频率合成器将通道光栅与PFD频率解耦,这意味着带内噪声显著降低。在ADF4106与ADF4153A的比较中可以看到这种优势(图5和图6比较),其中1 kHz时的带内噪声从–90 dBc/Hz改善至–105 dBc/Hz。此计算使用ADIsimPLL执行™,模拟ADI公司的所有PLL产品。

图4.相位误差 QPSK。

图5.整数 N,ADF4106 和 VCO-1901846T。

图6.小数N分频,ADF4153A和VCO-1901846T。

小数N分频还具有更快的采集时间,这是由于更高的PFD频率允许的允许环路带宽更宽。小数N分频杂散通过各种电荷泵失调电流和Σ-Δ抖动函数降至可接受的水平。ADF4193和ADF4153A分别支持26 MHz和32 MHz的PFD频率,更高的PFD频率允许用户进一步降低N,这进一步改善了EVM,并简化了频率规划,因为整数边界杂散(IBS)的发生率和影响较低。ADF4371上最新的PLL拓扑支持高达160 MHz的PFD频率。 分数调制器分辨率从12位分辨率提高到39位,提高了小数N分频分辨率,这也意味着PLL可用于生成几乎任何频率,具有毫赫兹(mHz)的分辨率和精确的频率精度。

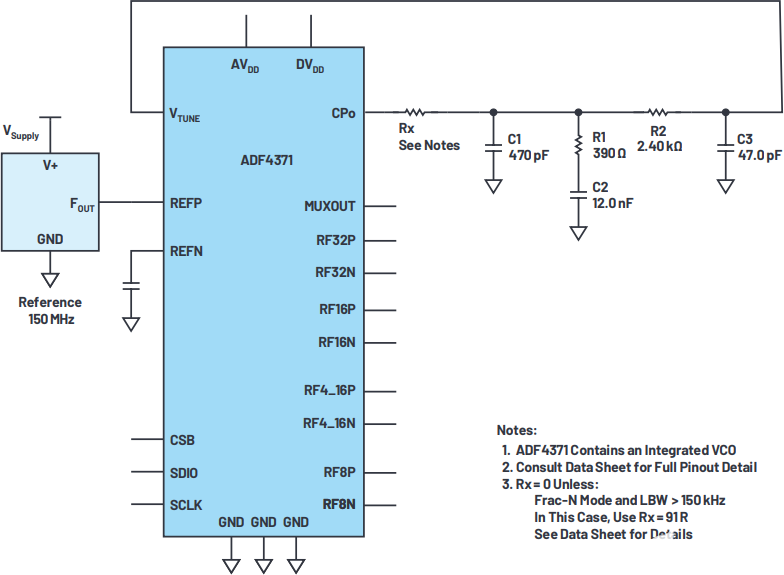

图7.ADF4371.

过去使用小数N分频的一个重大障碍是存在由Σ-Δ调制器产生的大分数杂散,这会降低频谱纯度,其影响需要代表用户进行额外的工程工作来减少或减轻。由于ADF4371上的分数杂散水平较低,没有整数边界,因此频谱干净意味着花在调查、调试或以某种方式减轻这些麻烦的频率生成伪像的影响上的时间更少。带内整数边界杂散(–55 dBc)水平较低,这意味着一旦被PLL滤波器滤波,杂散就会衰减良好。例如,如果 40 kHz 滤波器与 400 kHz 通道栅格一起使用,则滤波器提供的 35 dB 衰减意味着离整数边界最近的通道处的杂散显示为 –90 dBc。能够使用高达 160 MHz 的高 PFD 频率意味着整数边界的出现次数更少,160 MHz PFD 频率比 32 MHz PFD 频率少五倍。

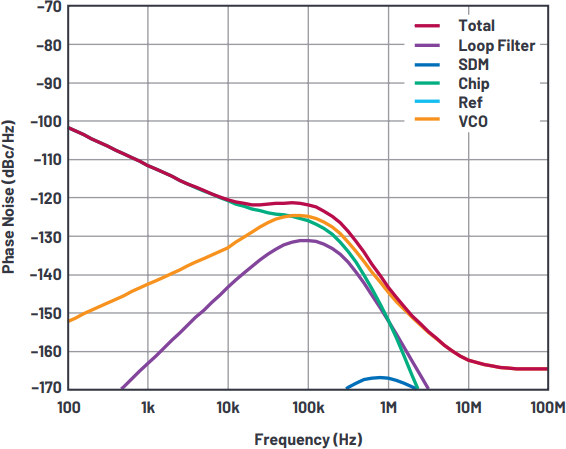

在提高PFD频率和频率分辨率的同时,PLL品质因数(FOM)也有所改进,从ADF4153的–216 dBc/Hz发展到ADF4371的–233 dBc/Hz(压裂模式)。图5中的ADIsimPLL图比较,显示ADF4106产生1.85 GHz输出,在整数模式下设置为200 kHz PFD频率,环路带宽为10 kHz,而ADF4371设置的PFD为160 MHz,环路带宽为150 kHz。在1 kHz偏移时观察到20 dB的差异,突出了PLL频率合成器技术的进步。

还显示了从1 ps到51 fs的积分均方根相位抖动的差异。值得注意的观察结果是,与过去电感Q主导均方根噪声性能相比,通过较低的FOM和小数N分频实现的带内噪声大幅改善,允许用户将环路滤波器带宽增加到150 kHz,抑制该带宽内的任何VCO噪声,并减少10 kHz至100 kHz范围内的性能下降。 这通常主导均方根噪声。更高规格的PLL基准电压源对于实现这种改进的带内相位噪声至关重要,但这种方法的性能和灵活性改进意味着大多数用户可以接受这种权衡。在某些情况下,新型小数N分频PLL的较低带内噪声可与偏移或转换环路PLL的带内噪声相媲美,其中混频器用于从VCO到PFD的反馈路径,从而大大简化了除最苛刻应用之外的所有应用的频率生成。

ADF4371 VCO的基本范围为4 GHz至8 GHz,这是用于制造该器件的SiGe工艺VCO相位噪声性能的最佳点。为了产生更高的频率,使用乘法器。重新设计VCO以将频率范围提高一倍有些问题,因为噪声的降低幅度超过了扩大VCO频率范围的预期6 dB。因此,包括一个倍频器,可将VCO范围扩展到8 GHz至16 GHz,以及一个四倍频器,可将4 GHz至8 GHz VCO范围扩展到16 GHz至32 GHz。在每种情况下,乘法器都会产生一些不需要的产物,包括VCO馈通,以及2×、3×和5×的VCO频率。为了简化滤波要求,每个乘法器电路都包含跟踪滤波器,用于调谐输出,从而最大限度地提高所需频率的功率而不是不需要的产品的功率。次谐波抑制通常低至双倍输出的45 dB和四倍输出的35 dB。

宽带操作

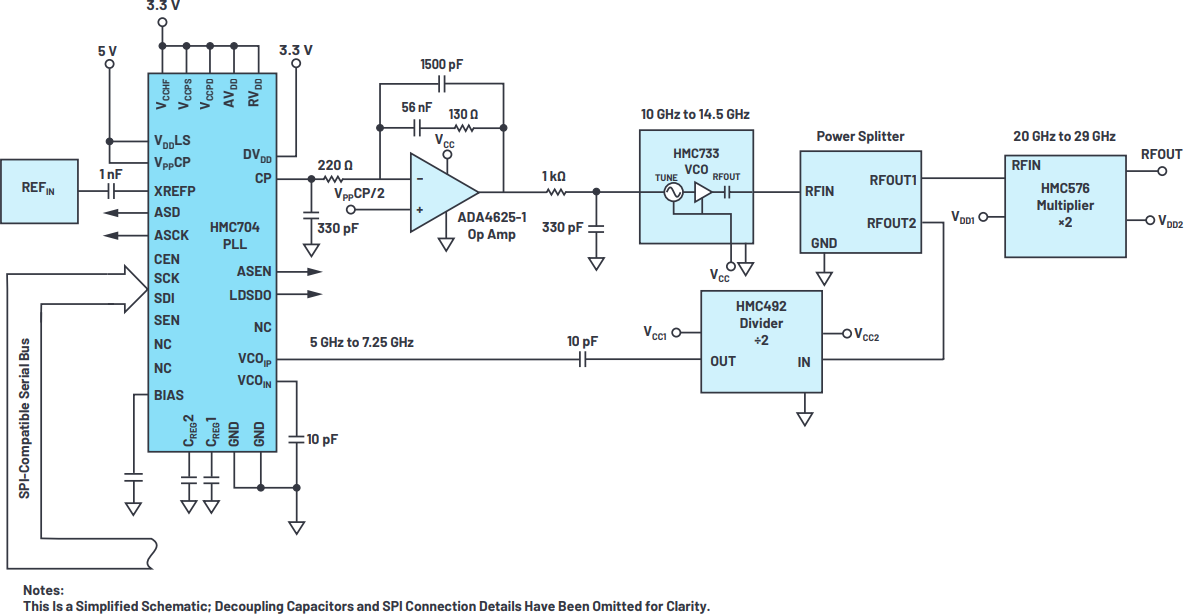

从前面所示的窄带示例中,新型PLL/VCO技术的优越性显而易见,但使用ADF4371生成宽带频率,并将其与使用HMC704 PLL与HMC733 VCO进行比较,也可以看到更显著的改进。用户在分立解决方案中面临许多挑战,其中目标是生成从20 GHz到29 GHz的干净可变LO。

首先,HMC733 VCO输出功率必须在板上分离并分频至适合HMC704的频率,因此必须使用外部分频器(HMC492)将HMC704允许的10 GHz至14.5 GHz范围缩小到5 GHz至7.25 GHz。

然后必须使用倍频器(HMC576)将10 GHz至15 GHz范围(最高20 GHz)乘以30 GHz范围。

需要一个有源低通滤波器来产生HMC733所需的调谐电压。本示例使用ADA4625-1。这还要求运算放大器的电源电压产生足够的调谐电压范围(本例中为15 V)。

调谐灵敏度的变化必须在VCO范围内进行补偿。通常,这是通过调节电荷泵电流以维持电荷泵增益和VCO增益的乘积来完成的。

HMC576乘法器后的VCO馈通约为–20 dBc。ADF4371上的调谐滤波器可将不需要的乘法器产物抑制35 dBc。这大大简化了任何后续过滤。

图8.分立式锁相环/VCO 乘法器解决方案。

相比之下,ADF4371 PLL/VCO开箱即用即可产生此频率范围,仅需外部高质量基准电压源。布局可以从 EV-ADF4371SD2Z 复制,并复制随附的电源管理解决方案。环路滤波器设计也大大简化,因为灵敏度kV的变化不需要最终用户的补偿,也不需要有源滤波器元件。用户无需花费数周时间选择器件和花费大量时间为每个分立元件开发仿真模型,而是可以使用ADIsimPLL来设计和仿真预期性能,并通过评估ADF4371的评估板来准确了解预期性能,该评估板将与仿真性能非常匹配。较低的元件数量和较高的集成度对系统的尺寸和重量有明显的好处,但也注意到性能显著提高,因为ADF4371的计算积分均方根抖动为60 fs,而分立解决方案的计算积分均方根抖动为160 fs。从图9的框图中可以明显看出元件和面积的节省,有源器件和功率分配器的总面积等于96 mm2—省略必要的去耦电容和其他所需的无源器件—与 49 mm 相比2适用于ADF4371。如果需要,用户还可以选择为VCO提供3.3 V电源以节省功耗。

图9.ADF4371原理框图

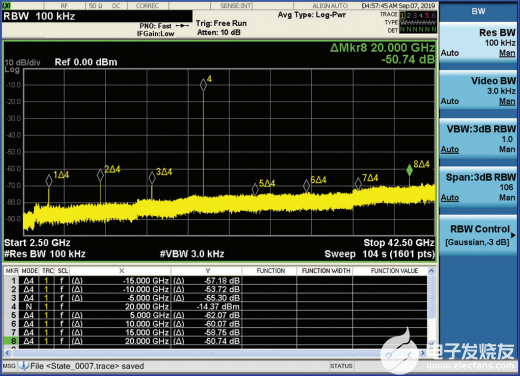

对于基波VCO模式,ADF4371的频谱纯度最高,无用杂散(非带内)仅限于VCO的谐波。对于许多转换器时钟应用,方波特性没有问题,可能确实是可取的,但对于仪器仪表应用,宽带杂散频率通常必须低于50 dBc。可调谐谐波滤波器有助于消除这些谐波,专门设计的ADMV8416/ADMV8432非常适合滤除ADF4371的输出。

ADMV8432是一款可调谐带通滤波器,额定工作中心频率范围为16 GHz至32 GHz,典型3 dB带宽为18%,典型插入损耗为9 dB,宽带抑制大于30 dB。该器件专为与ADF4371四通道输出配合使用而设计。同样,ADMV8416是一款可调谐带通滤波器,工作频率范围为7 GHz至16 GHz,典型带宽为3 dB,典型带宽为16%,典型插入损耗为8 dB,宽带抑制大于30 dB,适用于ADF4371倍增器输出。

图 10.ADF4371 20 GHz输出。

图 11.ADF4371 采用ADMV8432滤波器的20 GHz输出。

ADMV8416/ADMV8432均采用双通道重叠频段架构和内部RF开关,可实现更宽的频率覆盖范围,同时保持出色的抑制能力。频段的选择是通过数字逻辑控制进入必要的电平转换器。电平转换器确保内部RF开关相应地偏置,以实现大于+34 dBm的最佳输入三阶交调截点(IIP3)。

在每个工作频段内,可调谐滤波器通过0 V至15 V的模拟控制电压进行控制,该电压消耗的电流小于1 μA。该控制电压的产生通常通过DAC和运算放大器驱动器电路。这方面的一个例子是AD5760 DAC和运算放大器ADA4898,它为滤波器提供相对较快的调谐速度和低噪声驱动电压。如果调谐速度不重要,则可以将DAC直接驱动到滤波器的调谐端口。

考虑到这些模拟可调谐滤波器的性能指标,它们可以去除ADF4371频率合成器倍增器和四倍频器输出中不需要的谐波成分,但输出功率略有下降。虽然可能需要额外的放大级来克服插入损耗,但滤波器通常小于分立开关组解决方案,特别是在需要宽带可调谐性的情况下。此外,频率合成器的杂散电平通常从滤波前的–35 dBc提高到滤波后的–55 dBc。未滤波未使用输出的耦合会对馈通产生影响,应仔细建模以获得滤波器IC的全阻带抑制。

结论

频率生成的发展涉及工艺、电路和封装技术方面的各种创新,与以前的分立式解决方案相比,用户能够以更小的外形尺寸为用户提供更强大的功能和性能。宽带频率操作的趋势为开发覆盖多个倍频程的IC提供了必要的动力,频率范围高达32 GHz。宽带PLL/VCO带来的灵活性和简单性大大缩短了最终客户的设计时间和上市时间。

对频谱纯度的需求推动了滤波IC的创新,这些IC与这些新开发的合成器IC配对,为现代无线应用的需求提供低相位噪声、高频谱纯度的毫米波信号源。免费的仿真工具ADIsimPLL使用户能够评估和比较PLL性能,通过易于使用的直观界面和快速行为模型帮助选择元件。该工具为设计工程师节省了大量时间,否则他们需要在许多不同的领域开发许多不同的数学模型来预测性能。

审核编辑:郭婷

-

微波

+关注

关注

16文章

1043浏览量

83682 -

pll

+关注

关注

6文章

776浏览量

135130 -

RF

+关注

关注

65文章

3050浏览量

166963

发布评论请先 登录

相关推荐

新ESD技术减小芯片的I/O尺寸

用于无线应用的集成PLL和VCO

VCO底部,中间或顶部是最佳PLL性能吗?

基于高压VCO的高性能PLL设计

集成低噪声VCO的ADF4350系列PLL之特性和应用

ADI公司集成VCO的PLL频率合成器改善基站性能和无线服务质量

高性能RF PLL和PLL VCO技术的介绍

利用高压VCO设计高性能锁相环

PLL对于VCO有什么要求?如何设计VCO输出功率分配器?

PLL原理及主要技术指标

PLL/VCO技术如何提高性能、减小尺寸并简化设计周期

PLL/VCO技术如何提高性能、减小尺寸并简化设计周期

评论