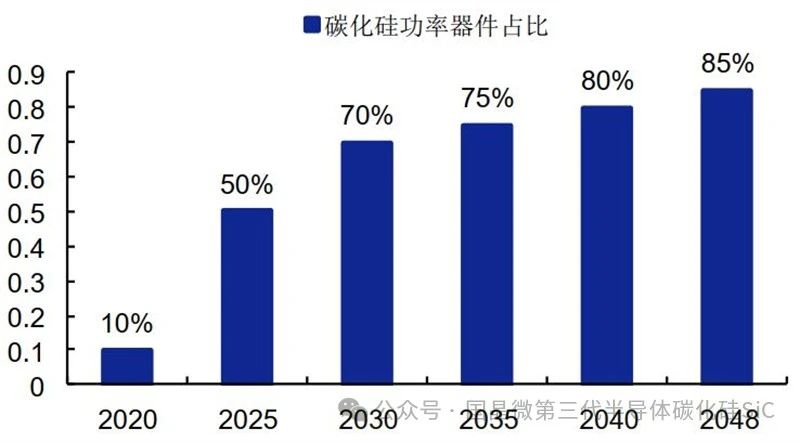

第三代半导体碳化硅是目前半导体领域最热门的话题。提到碳化硅(SiC),人们的第一反应是其性能优势,如更低损耗、更高电压、更高频率、更小尺寸和更高结温,非常适合制造大功率电子器件;如果说到应用,大多数人都会说它成本太高,推广起来需假以时日,等等。事实上,在一些有性能、效率、体积、散热,甚至系统成本有要求的应用中,典型代表行业如电源,碳化硅器件与硅器件的成本差距正在收窄。

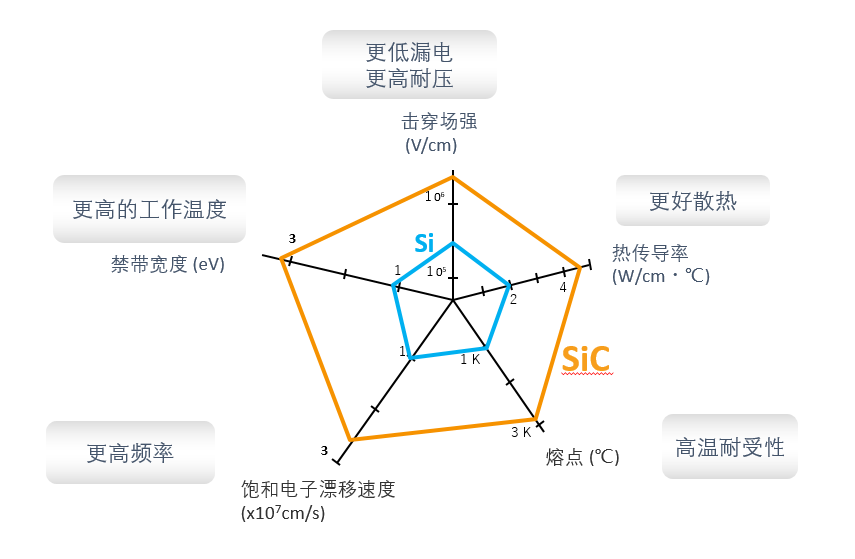

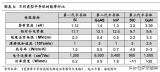

图1 硅材料和碳化硅材料参数对比

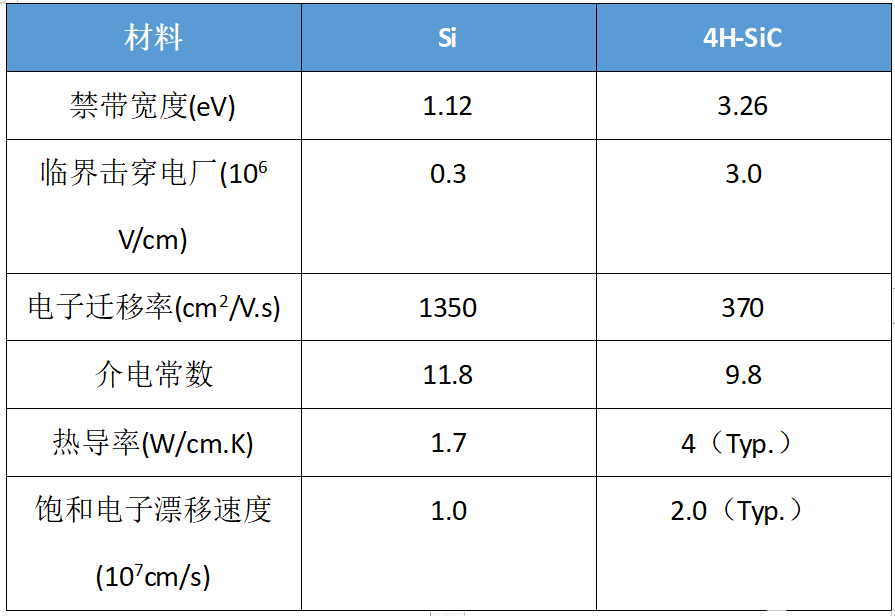

表1 硅材料和碳化硅材料参数对比

那么,基于如此明显的优势的碳化硅材料制成的碳化硅肖特基器件能带来哪些优势呢?

1、器件自身优势

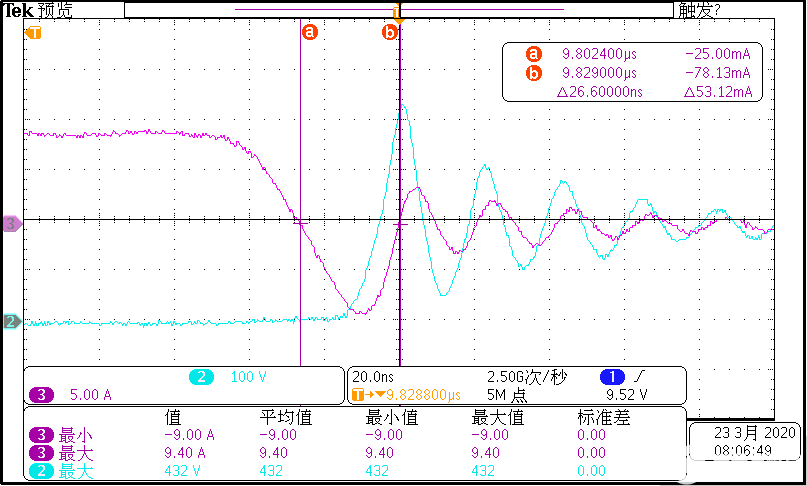

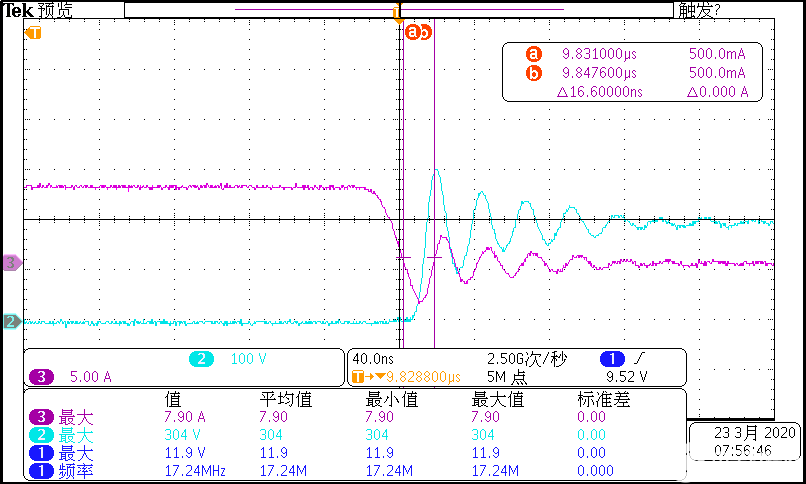

击穿电压高(常用电压有650V/1200V)、可靠性高(结温175℃ )、开关损耗小和导通损耗小、器件反向恢复时间几乎为0,且恢复电压应力较小(参考下图),有利于降低系统噪声,提高EMI裕量。

图2 Si FRD 反向恢复波形

图3 SiC SBD 反向恢复波形

2、应用优势

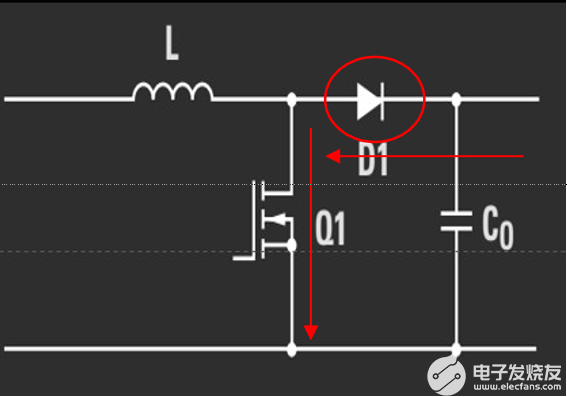

在CCM PFC电路中,碳化硅肖特基零反向恢复电流可以降低主功率MOSFET开启瞬间的电流应力,从而使它能够以较少的热损失转换电能,硅半导体必须大得多才能实现相同的性能。这体现在产品上,即碳化硅肖特基在降低电源温度提高转换效率的同时还能显著减小电源的尺寸,这将为制造商带来巨大的效益。

图4 CCM PFC 电路图

功率半导体作为电力系统的组成部分,是提升能源效率的决定性因素之一。在肖特基发展历程中,追求更低损耗是行业一直以来的共同目标,肖特基器件损耗主要由导通损耗和开关损耗导致,且无用功损耗会以发热的行式释放,使电源温度升高。

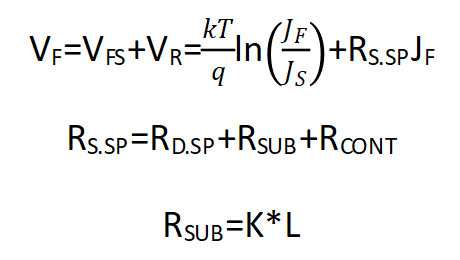

导通损耗和正向压降正相关,我们根据VF正向压降公式以及公式分解可以得到,降低芯片厚度可以有效降低VF。从而降低导通损耗。

而开关损耗和电容值正相关。根据推导公式可得,减小结面积可以有效降低电容值,从而降低开关损耗。

从设计人员的角度来看,正向压降与电容二者之间的平衡至关重要,而使用新工艺可以带来更优的综合性能。目前碳化硅肖特基产品工艺节点大致可以分为4个:

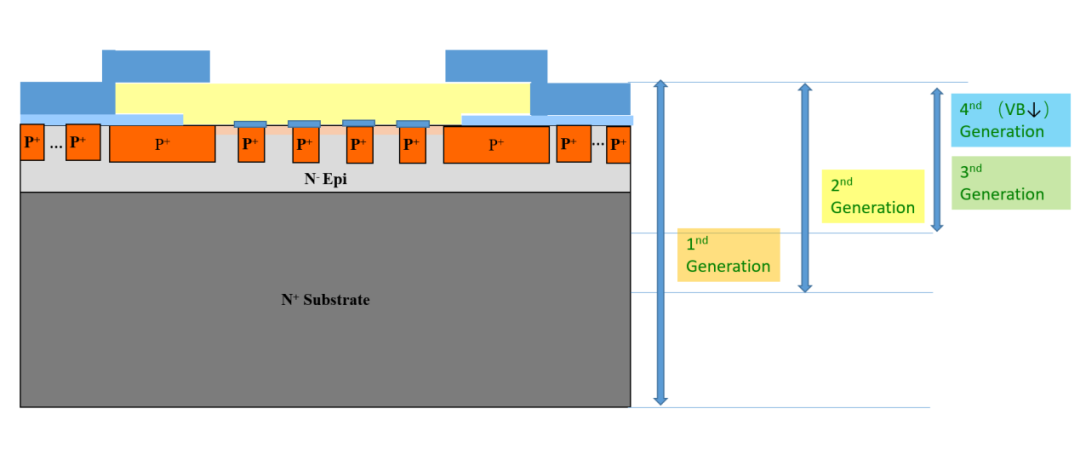

第一代产品芯片厚度以300μm以上为工艺节点,常见厚度为300μm、350μm、390μm厚度。此工艺制造的芯片厚度较厚,对加工过程中减划、金属化等等工艺要求较低,但是缺点也是显而易见的,由于芯片较厚故很难在正向压降和电容之间得到一个较优的综合性能,目前国内少部分厂家还沿用此工艺。

第二代产品以芯片厚度为250μm为代表。目前国内厂家量产产品大多采用此节点工艺,维安第一代产品也是基于此节点工艺进行开发(目前已经更新到第三代),但是此工艺较国际一线大厂还有一定差距。

第三代产品以芯片厚度150μm为代表。这个工艺节点也是国内大多数厂家在21年底到22年初推出的新工艺平台,大部分厂家目前还正在处于研发阶段,部分国际一线大厂量产产品采用150μm工艺节点,例如CREE C6系列在此节点工艺进行开发,但此工艺具国际最优水平还有一定差距。

第四代产品以100μm厚度为代表。此工艺水平为目前国际最优量产水平,国际上英飞凌C6等产品采用此节点工艺进行开发,得到VF和电容性能的综合优势,维安目前量产主推工艺也是采用此节点,工艺水平领先国内主流1代~1.5代水平。

3年的潜心研发,加之在开发过程中不断自我优化迭代,维安碳化硅肖特基产品历经250μm、150μm、100μm三次更新,目前量产产品全部采用100μm节点(维安第三代)薄片工艺,通过降低芯片厚度降低导通损耗和使用缩小有效结面积的方法降低电容,使器件电流密度,导通损耗和开关损耗等器件参数性能优于同行业水平。

图5 维安碳化硅肖特基结构迭代示意图

手机等消费类电源、太阳能逆变电源、新能源电动汽车及充电桩、工业控制特种电源……作为一个重要的快速发展的应用领域,电源行业的发展受益于功率器件技术进步,反过来又推动了功率器件的研发制造活动。在电源模块中使用碳化硅肖特基器件,具有以下优势:

开关损耗极低;

较高的开关频率;

结温高,从而降低了冷却要求和散热要求;

更小封装,适合更紧凑的方案。

政府产业鼓励政策固然重要,但是,真正的市场需求,更好的用户体验,以及产品优势,才是引爆市场的关键。

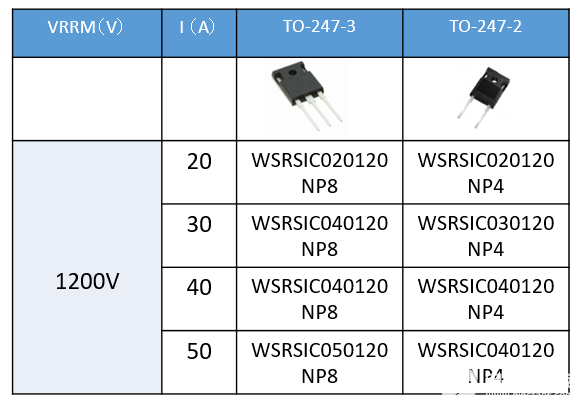

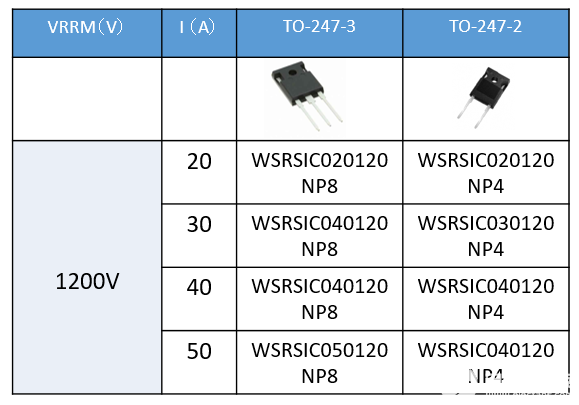

维安碳化硅肖特基推出以下系列产品:

表2 维安650V系列碳化硅肖特基二极管

表3 维安1200V系列碳化硅肖特基二极管

维安产品仍在不断自我优化,正在开发第四代产品,持续推出损耗更小,开关速度更高的碳化硅肖特基器件。

审核编辑黄宇

-

电源

+关注

关注

184文章

17704浏览量

249949 -

半导体

+关注

关注

334文章

27286浏览量

218025 -

SiC

+关注

关注

29文章

2804浏览量

62601 -

碳化硅

+关注

关注

25文章

2748浏览量

49014

发布评论请先 登录

相关推荐

碳化硅在半导体产业中的发展

碳化硅SiC制造工艺详解 碳化硅SiC与传统半导体对比

碳化硅SiC材料应用 碳化硅SiC的优势与性能

碳化硅功率器件有哪些优势

国内碳化硅功率半导体元件市场迎来高速增长

碳化硅器件的类型及应用

碳化硅压敏电阻 - 氧化锌 MOV

半导体碳化硅(SiC)行业研究

碳化硅特色工艺模块简介

半导体届“小红人”——碳化硅肖特基,让你的电源温度低过冰墩墩

半导体届“小红人”——碳化硅肖特基,让你的电源温度低过冰墩墩

评论