微控制器、FPGA、DSP、ADC 和其他采用多个电压轨工作的器件需要电源排序。这些应用通常要求内核和vwin 模块在数字I/O轨之前上电,尽管某些设计可能需要其他序列。在任何情况下,适当的上电和关断时序都可以防止闩锁造成的直接损坏和ESD的长期损坏。此外,对电源进行排序可错开上电期间的浪涌电流,这在采用限流电源供电的应用中是一种特别有用的技术。

本文讨论使用分立元件对电源进行排序的优缺点,并介绍一种简单而有效的时序方法,该方法利用ADP5134的内部精密使能引脚实现时序控制,该引脚将两个1.2 A降压稳压器与两个300 mA LDO集成在一起。它还展示了一些时序控制器IC,它们可能对需要更准确和灵活时序控制的应用有用。

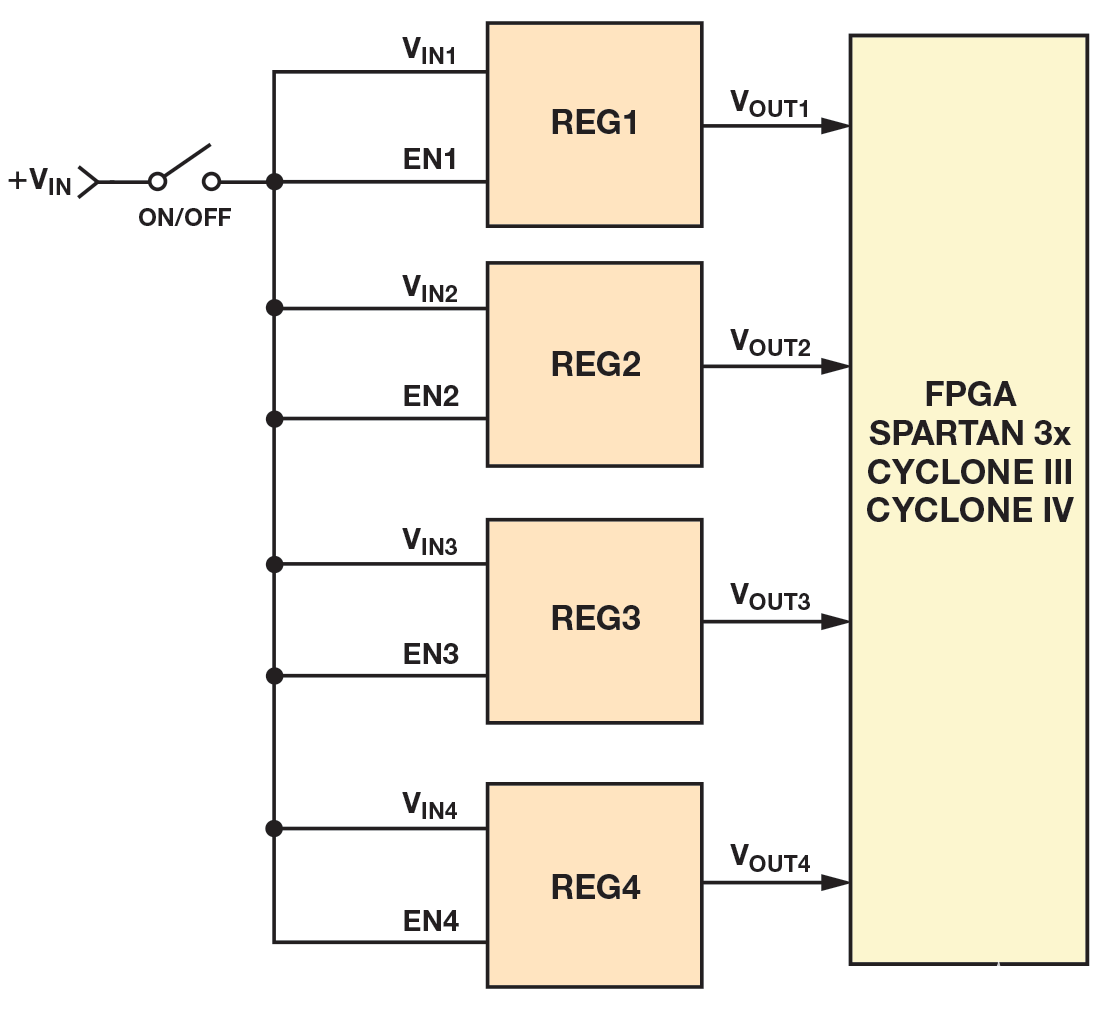

图1所示为需要多个电源轨的应用。这些电源轨是核心电源 (VCCINT)、I/O 电源 (V首席运营官)、辅助电源 (V科考),和系统内存供应。

图1.为处理器和 FPGA 供电的典型方法。

例如,Xilinx Spartan-3A FPGA 具有内置的上电复位电路,可确保在允许配置器件之前,所有电源均已达到其阈值。这降低了对电源排序的严格要求,但为了最大限度地降低浪涌电流水平并遵守连接到FPGA的电路的排序要求,电源轨应按如下方式上电:V®CC_INT→ VCC_AUX→ V首席运营官.请注意,某些应用需要特定的序列,因此请始终阅读每个数据手册的电源要求部分。

使用无源延迟网络的简单电源排序

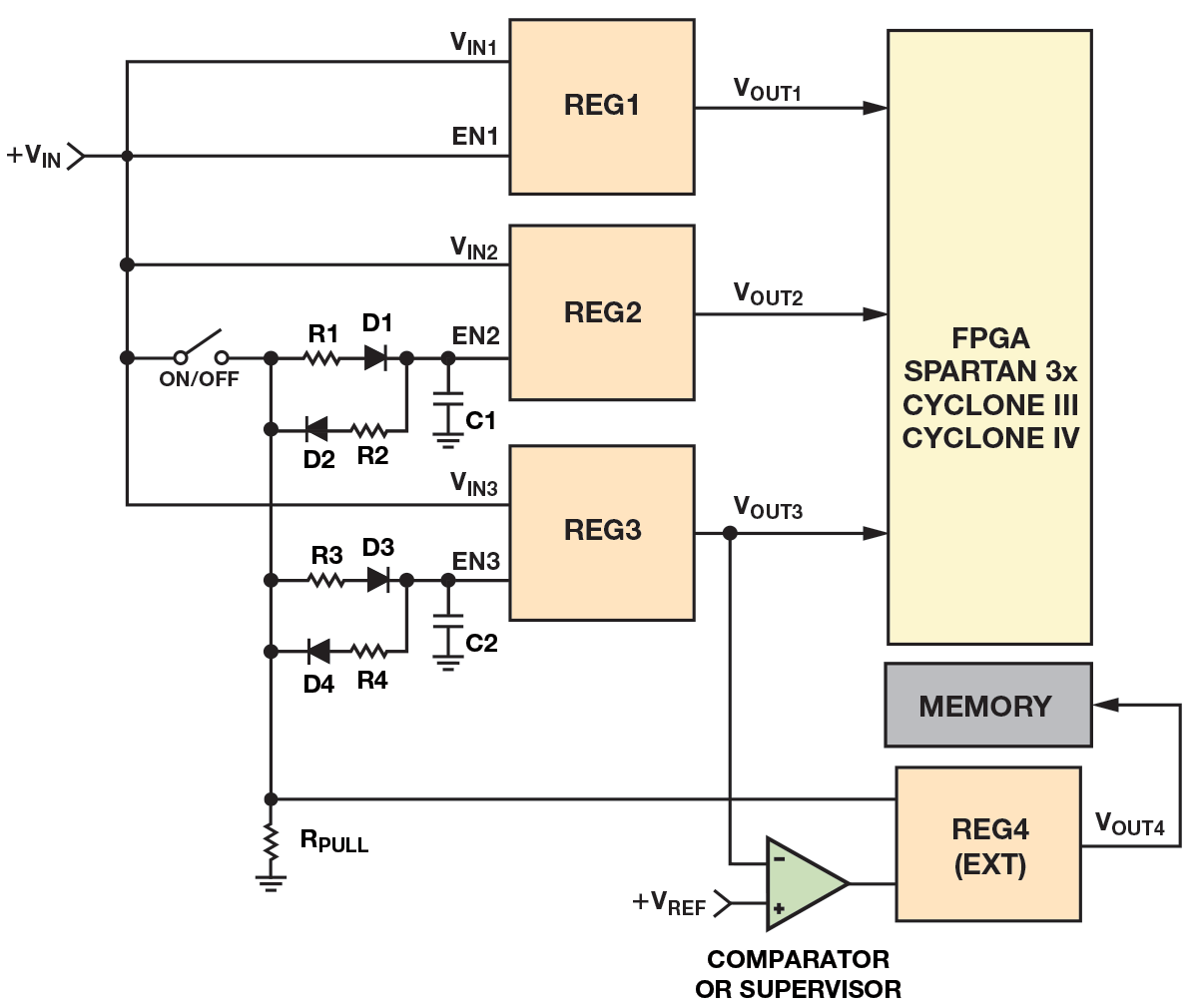

对电源进行排序的一种简单方法是使用电阻、电容和二极管等无源元件延迟信号进入稳压器的使能引脚,如图2所示。当开关闭合时,D1 导通,而 D2 保持打开状态。电容器 C1 充电,EN2 处的电压以 R1 和 C1 确定的速率上升。当开关断开时,电容C1通过R2、D2和R放电至地拉.EN2 处的电压以 R2、R 确定的速率下降拉和 C2。改变R1和R2的值会改变充电和放电时间,从而设置稳压器的导通和关断时间。

图2.简单的电源排序方法使用电阻、电容和二极管。

这种方法对于不需要精确排序的应用可能很有用,而一些应用,只需延迟信号就足够了,可能只需要外部R和C。将这种方法与标准稳压器配合使用的缺点是,使能引脚的逻辑阈值可能随电压和温度而变化很大。此外,电压斜坡的延迟取决于电阻和电容的值和容差。典型的X5R电容在–55°C至+85°C温度范围内变化约±15%,由于直流偏置效应,变化±10%,使得时序不精确,有时不可靠。

精密使能使测序变得简单

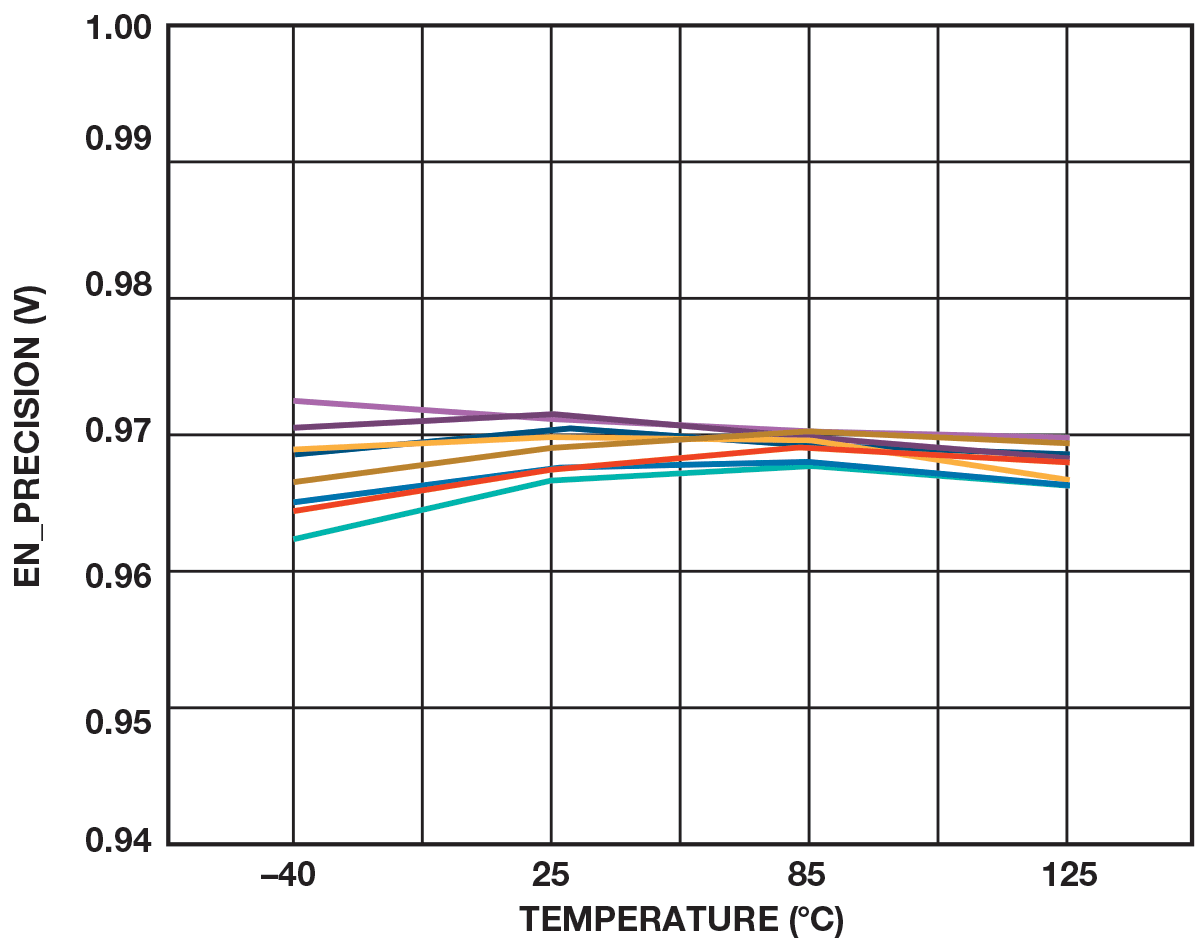

为了获得稳定的阈值电平以实现精确的时序控制,大多数稳压器需要一个外部基准电压源。ADP5134通过集成精密基准电压源克服了这一问题,节省了大量成本和PCB面积。每个稳压器都有一个单独的使能输入。当使能输入端的电压升至V以上时IH_EN(最小值为0.9 V),器件退出关断状态,内务管理模块接通,但稳压器未激活。使能输入端的电压与精确的内部基准电压(典型值为0.97 V)进行比较。一旦使能引脚上的电压超过精密使能门限,稳压器就会被激活,输出电压开始上升。基准电压源在输入电压和温度转折范围内的变化仅为 ±3%。这种小范围确保了精确的时序控制,解决了使用分立元件时出现的问题。

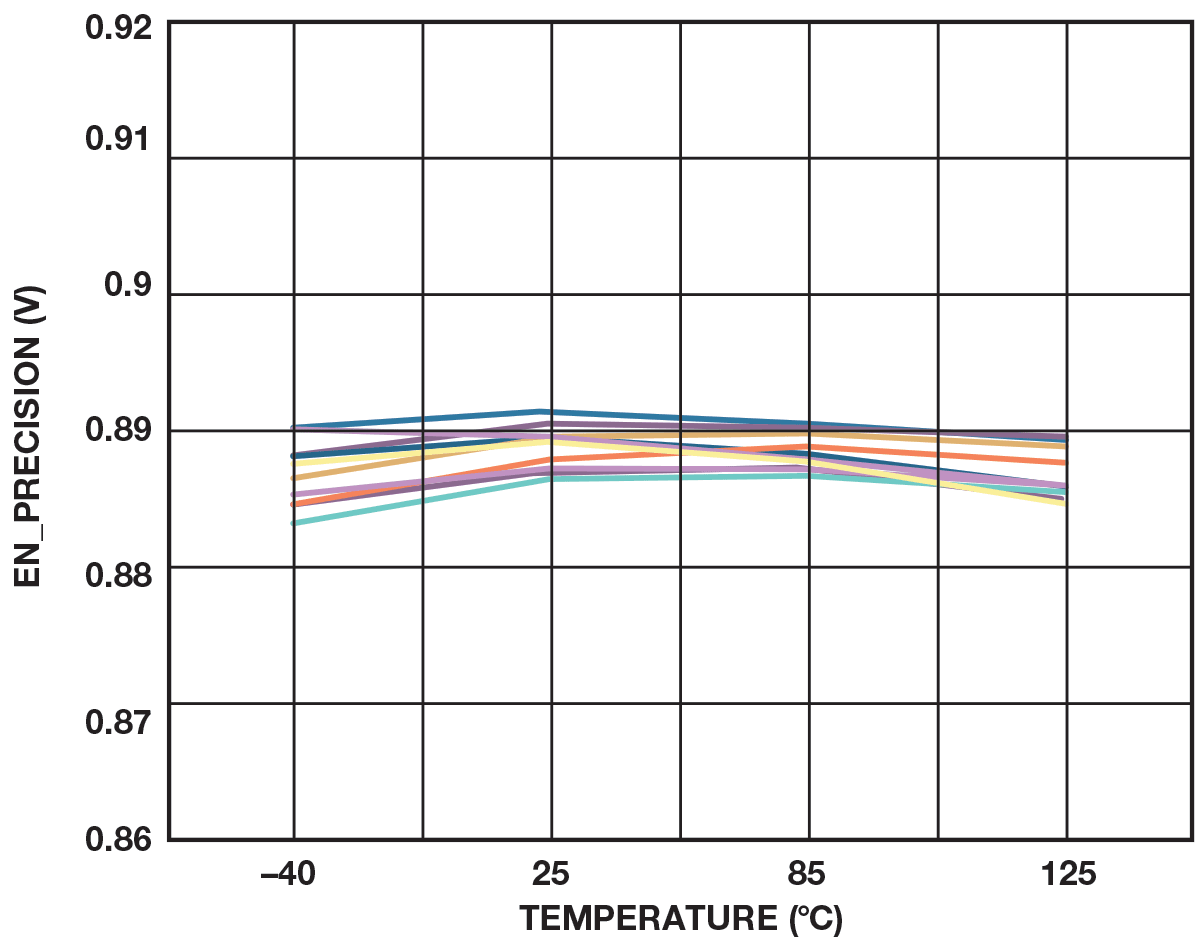

当使能输入端的电压降至基准电压以下80 mV(典型值)时,稳压器失活。当所有使能输入上的电压降至 V 以下时IL_EN(最大值为0.35 V),器件进入关断模式。在这种模式下,电流消耗降至1 μA以下。图3和图4显示了ADP5134精密使能阈值在整个温度范围内的Buck1精度。

图3.在整个温度范围内具有精密使能导通阈值,10 个样本。

图4.在整个温度范围内的精密使能关断阈值,10 个样本。

使用电阻分压器的简单电源排序

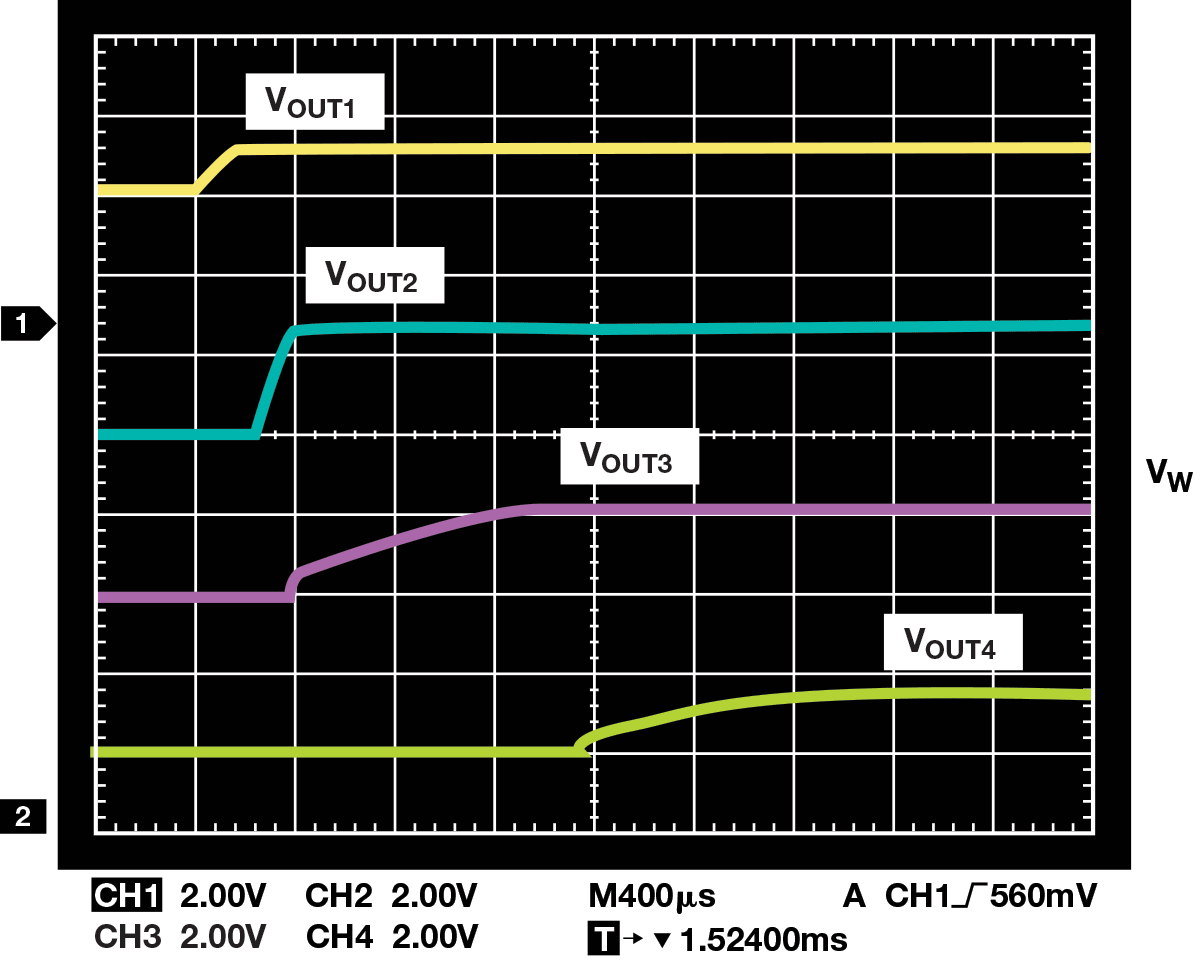

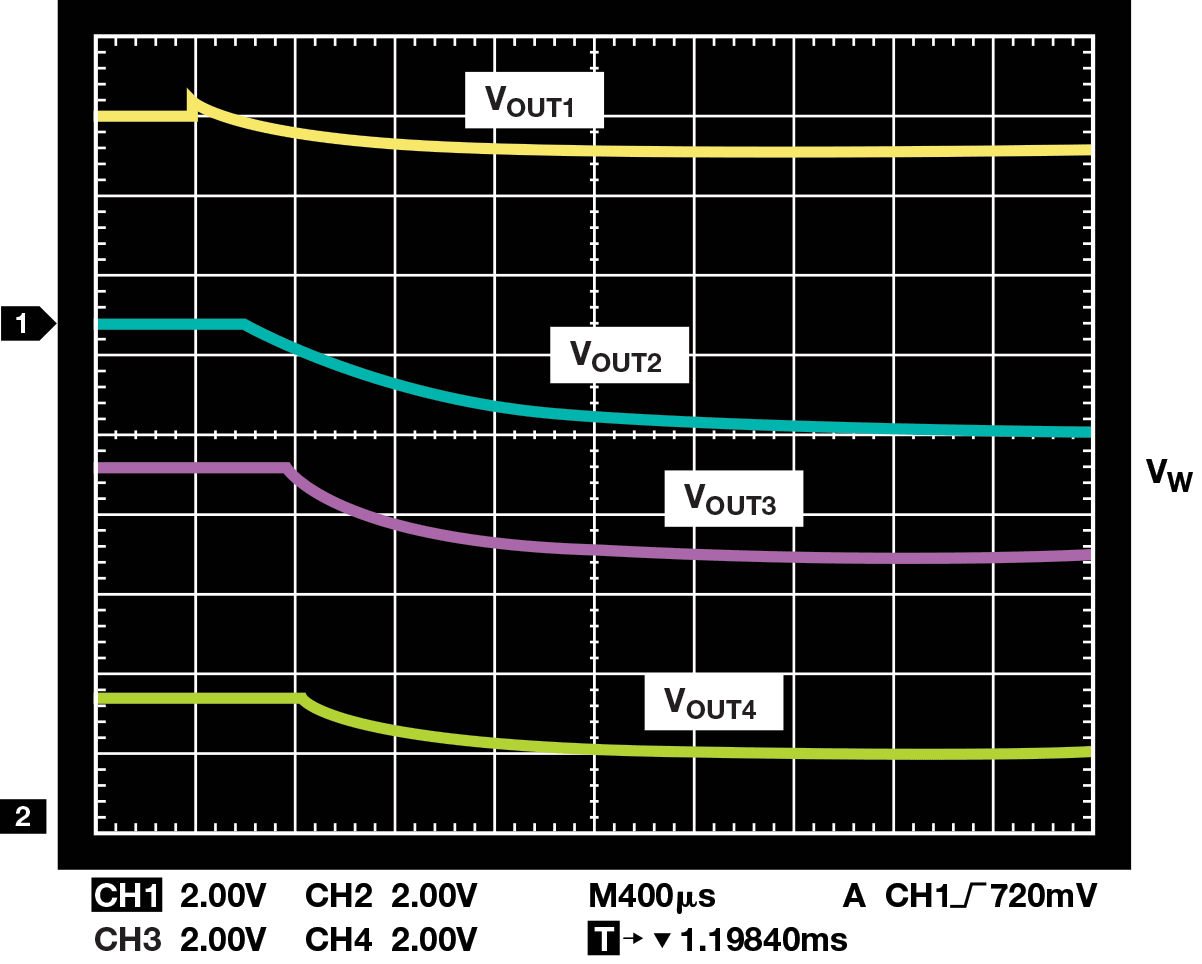

通过将一个稳压器输出的衰减版本连接到下一个上电稳压器的使能引脚,可以对多通道电源进行排序,如图5所示,其中稳压器依次导通或关断:降压1→降压2→LDO1→LDO2。图6显示了EN1连接到V后的上电顺序合1.图7显示了EN1与V断开连接后的关断序列合1.

图5.使用ADP5134进行简单排序。

图6.ADP5134启动序列

图7.ADP5134关断时序

时序控制器 IC 提高定时精度

在某些情况下,实现精确的时序比减少PCB面积和成本更重要。对于这些应用,可以使用电压监控和排序器IC,例如四通道电压监控器ADM1184,在整个电压和温度范围内提供±0.8%的精度。或者,具有可编程时序的四通道电压排序器和监视器ADM1186可能适用于需要更精细地控制上电和关断时序的应用。

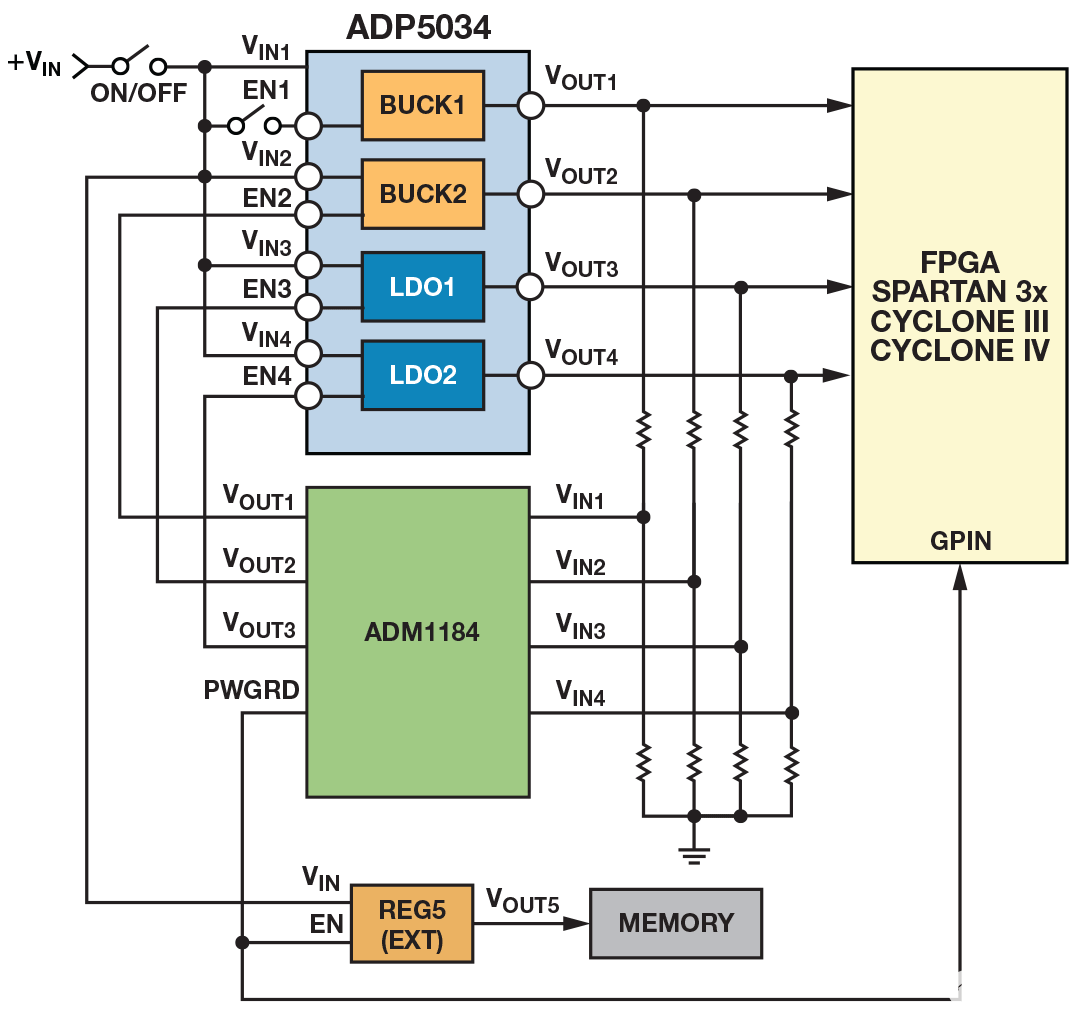

ADP5034 4通道稳压器包括两个3 MHz、1200 mA降压稳压器和两个300 mA LDO。典型的时序功能可通过使用ADM1184监控一个稳压器的输出电压来实现,并在被监控输出电压达到一定电平后向下一个稳压器的使能引脚提供逻辑高电平信号。这种方法如图8所示,可用于不提供精密使能功能的稳压器。

图8.使用四通道电压监控器ADM1184对ADP5034 4通道稳压器进行排序。

结论

使用ADP5134的精密使能输入进行时序控制简单且易于实现,每个通道仅需两个外部电阻。使用ADM1184或ADM1186电压监控器可以实现更精细的时序控制。

审核编辑:郭婷

-

微控制器

+关注

关注

48文章

7542浏览量

151306 -

电源

+关注

关注

184文章

17704浏览量

249952 -

dsp

+关注

关注

553文章

7987浏览量

348727 -

FPGA

+关注

关注

1629文章

21729浏览量

602958 -

稳压器

+关注

关注

24文章

4223浏览量

93757

发布评论请先 登录

相关推荐

通过一个6通道电源轨排序轻松解决方案

怎么实现6通道电源排序

轻松实现复杂电源时序控制

电源排序得以简化

详解 FPGA 电源排序的四种方案

四种FPGA 电源排序方案

如何选择FPGA电源排序?这几个方法交给你

关于电源排序的解决方案你了解吗

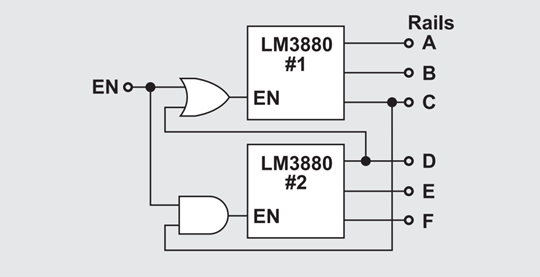

对2个LM3880进行简单排序实现6通道加电和断电排序

轻松实现复杂的电源排序

轻松实现复杂的电源排序

评论