MAX77812为四相、大电流、降压转换器,适用于高端游戏机、VR/AR耳机、数码单反相机、无人机、网络交换机和路由器,以及使用多核处理器的FPGA系统。MAX77812具有工厂可编程OTP(一次性可编程)选项,用于定制启动顺序和用于关断序列的单独寄存器设置。本文档说明如何对这些寄存器进行编程,并提供一个示例。

介绍

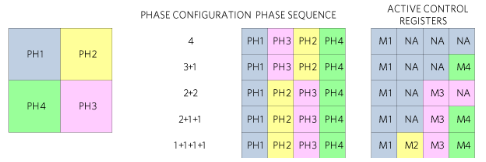

MAX77812支持主相之间的可编程启动和关断。启动和关断序列由 GPI 的 EN 引脚或GLB_EN功能启动。主相之间的启动和关断延迟时间可在0ms至62ms (32级)范围内设置,延迟时间步长为1ms/2ms。

启动和关断顺序设置

启动顺序由STUP_DLYx寄存器设置,默认值为工厂编程选项(有关详细信息,请参见数据手册中的“订购信息”部分),而关断延迟寄存器(SHDN_DLYx)的默认值是固定的,默认情况下主相之间没有延迟时间。

当CE引脚为高电平(待机模式)时,用户可以通过串行接口覆盖启动和关断寄存器。

请注意,一旦启动序列,M1(主1)始终处于打开状态,没有可编程延迟。

如果在启动或关断序列之前,GPI0/1 的 EN_Mx 位或Mx_EN功能打开了任何主相,则启动或关断事件对已打开的主相是透明的。

例如,如果我们希望在10+1+1+1相配置的主相之间有1ms的延迟时间,STUP_DLYx寄存器可以按如下方式编程(寄存器编程详细信息见表1至表7):

延迟时间步长:通过设置 DLY_STEP = 1 为 0ms

从 M1 到 M2 的延迟时间:通过设置 M10_STUP_DLY[2:4] = 0b 为 01010ms

从 M1 到 M3 的延迟时间:通过设置 M20_STUP_DLY[3:4] = 0b 为 10100ms

从 M1 到 M4 的延迟时间:通过设置 M30_STUP_DLY[4:4] = 0b 为 11110ms

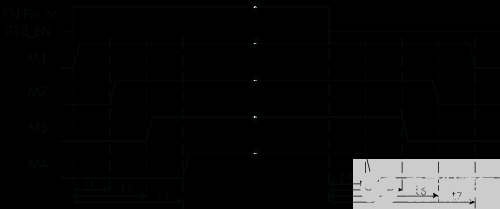

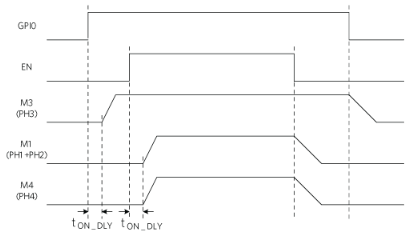

图1中的图表显示了典型的启动和关断顺序。

图1.启动和关闭顺序。

|

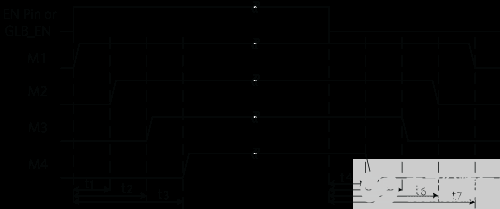

地址 0x07 |

模式 R/W |

类型: O | 复位值:0x00 (OTP) | |

|---|---|---|---|---|

| 位 | 名字 | 波尔 | 描述 | |

| 7 | DLY_STEP | 0 |

延迟时间步长选择 0: 1ms 1: 2ms |

|

| 6:5 | 保留 | 00 | ||

| 4:0 | M2_STUP_DLY[4:0] | 0 0000 |

降压稳压主控 2 启动延迟时间设置(从 EN 引脚或 GLB_EN 上升沿的延迟) 0 0000b = 0ms 0 0001b = 1 x DLY_STEP 0 0010b = 2 x DLY_STEP · · · · · · 1 1110b = 30 x DLY_STEP 1 1111b = 31 x DLY_STEP |

|

|

地址 0x08 |

模式 R/W |

类型: O | 复位值:0x00 (OTP) | |

|---|---|---|---|---|

| 位 | 名字 | 波尔 | 描述 | |

| 7:5 | 保留 | 000 | ||

| 4:0 | M3_STUP_DLY[4:0] | 0 0000 |

降压稳压主控 3 启动延迟时间设置(从 EN 引脚或 GLB_EN 上升沿的延迟) 0 0000b = 0ms 0 0001b = 1 x DLY_STEP 0 0010b = 2 x DLY_STEP · · · · · · 1 1110b = 30 x DLY_STEP 1 1111b = 31 x DLY_STEP |

|

|

地址 0x09 |

模式 R/W |

类型: O | 复位值:0x00 (OTP) | |

|---|---|---|---|---|

| 位 | 名字 | 波尔 | 描述 | |

| 7:5 | 保留 | 000 | ||

| 4:0 | M4_STUP_DLY[4:0] | 0 0000 |

降压稳压主控 4 启动延迟时间设置(从 EN 引脚或 GLB_EN 上升沿的延迟) 0 0000b = 0ms 0 0001b = 1 x DLY_STEP 0 0010b = 2 x DLY_STEP · · · · · · 1 1110b = 30 x DLY_STEP 1 1111b = 31 x DLY_STEP |

|

|

地址 0x0A |

模式 R/W |

类型: O | 复位值:0x00 (OTP) | |

|---|---|---|---|---|

| 位 | 名字 | POR | 描述 | |

| 7:5 | 保留 | 000 | ||

| 4:0 | M1_SHDN_DLY[4:0] | 0 0000 |

降压稳压主控器 1 关断延迟时间设置(来自 EN 引脚或 GLB_EN 下降沿的延迟) 0 0000b = 0ms 0 0001b = 1 x DLY_STEP 0 0010b = 2 x DLY_STEP · · · · · · 1 1110b = 30 x DLY_STEP 1 1111b = 31 x DLY_STEP |

|

|

地址 0x0B |

模式 R/W |

类型: O | 复位值:0x00 (OTP) | |

|---|---|---|---|---|

| 位 | 名字 | POR | 描述 | |

| 7:5 | 保留 | 000 | ||

| 4:0 | M2_SHDN_DLY[4:0] | 0 0000 |

降压稳压主控器 2 关断延迟时间设置(来自 EN 引脚或 GLB_EN 下降沿的延迟) 0 0000b = 0ms 0 0001b = 1 x DLY_STEP 0 0010b = 2 x DLY_STEP · · · · · · 1 1110b = 30 x DLY_STEP 1 1111b = 31 x DLY_STEP |

|

|

地址 0x0C |

模式 R/W |

类型: O | 复位值:0x00 (OTP) | |

|---|---|---|---|---|

| 位 | 名字 | POR | 描述 | |

| 7:5 | 保留 | 000 | ||

| 4:0 | M4_SHDN_DLY[4:0] | 0 0000 |

降压稳压主控器 4 关断延迟时间设置(来自 EN 引脚或 GLB_EN 下降沿的延迟) 0 0000b = 0ms 0 0001b = 1 x DLY_STEP 0 0010b = 2 x DLY_STEP · · · · · · 1 1110b = 30 x DLY_STEP 1 1111b = 31 x DLY_STEP |

|

|

地址 0x0D |

模式 R/W |

类型: O | 复位值:0x00 (OTP) | |

|---|---|---|---|---|

| 位 | 名字 | POR | 描述 | |

| 7:5 | 保留 | 000 | ||

| 4:0 | M3_SHDN_DLY[4:0] | 0 0000 |

降压稳压主控器 3 关断延迟时间设置(来自 EN 引脚或 GLB_EN 下降沿的延迟) 0 0000b = 0ms 0 0001b = 1 x DLY_STEP 0 0010b = 2 x DLY_STEP · · · · · · 1 1110b = 30 x DLY_STEP 1 1111b = 31 x DLY_STEP |

|

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19259浏览量

229642 -

FPGA

+关注

关注

1629文章

21729浏览量

602955 -

寄存器

+关注

关注

31文章

5336浏览量

120224

发布评论请先 登录

相关推荐

MAX77812四相大电流降压稳压器解析(优势、电路图、特性)

MAX16050/MAX16051多路电压排序器的特点及如何配置上电和关断顺序

嵌入式启动顺序及原理

MAX77812的工厂可编程参数

MAX77812的过流保护工作原理

使用MAX77812产生高于1.525V的输出电压

MAX77812EVKIT# 评估板 - DC/DC 与 AC/DC(离线)SMPS

使用MAX1产生高于525.77812V的输出电压

MAX77812用户可选相位配置指南及其选择方法

如何使用多功能GPI

MAX778812EVKIT:MAX77812数据表评价工具包 ADI

如何利用MAX77812设置启动和关断顺序

如何利用MAX77812设置启动和关断顺序

评论