如何建立异形板框的内缩和外扩

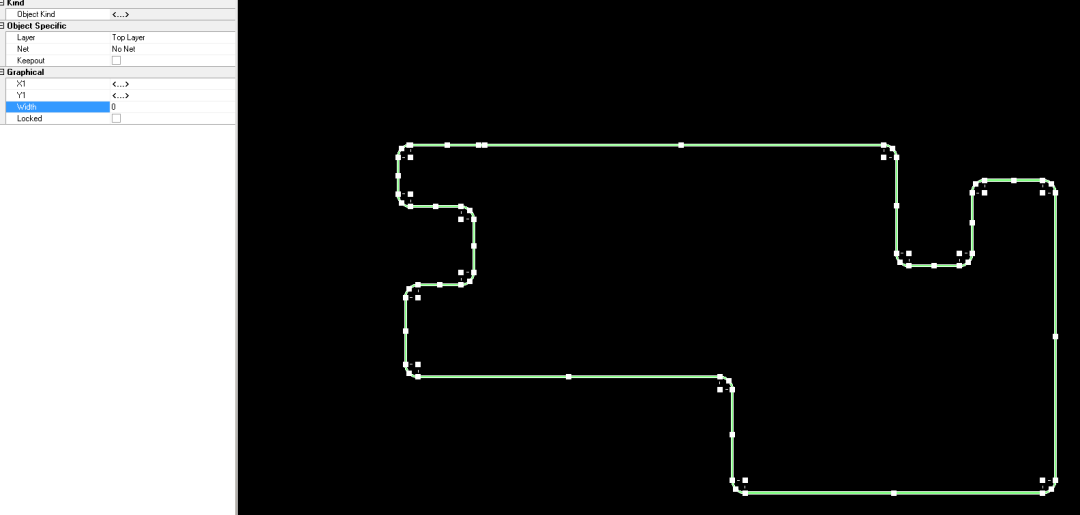

首先把需要内缩和外扩的外形图设置在信号层(比如TOP),把线宽改为0mil(方便计算)。

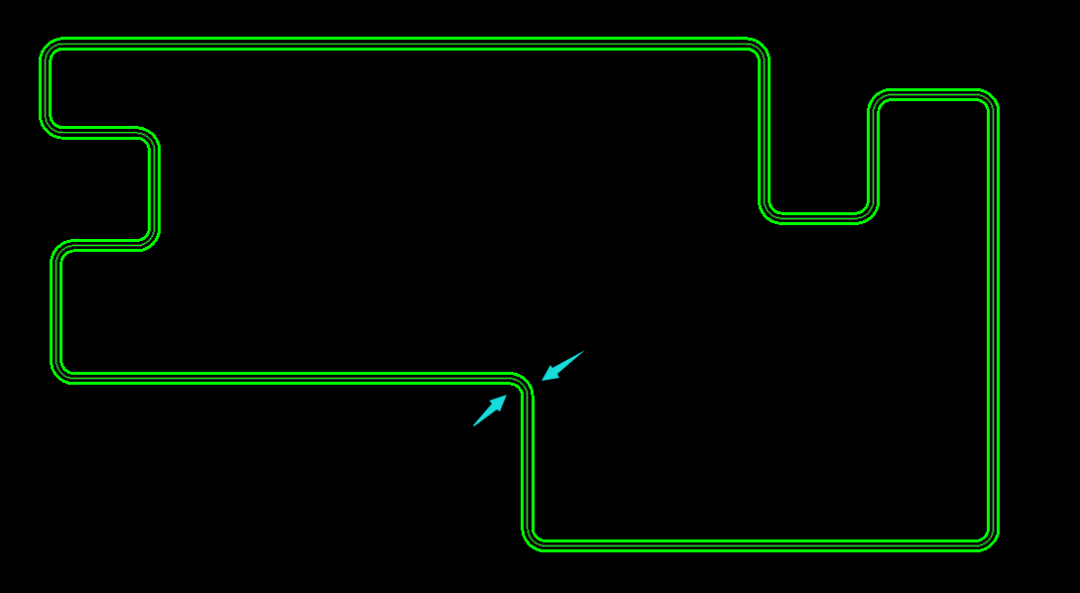

然后选择外形图,执行命令TJ,就可以得到内缩和外扩图形。

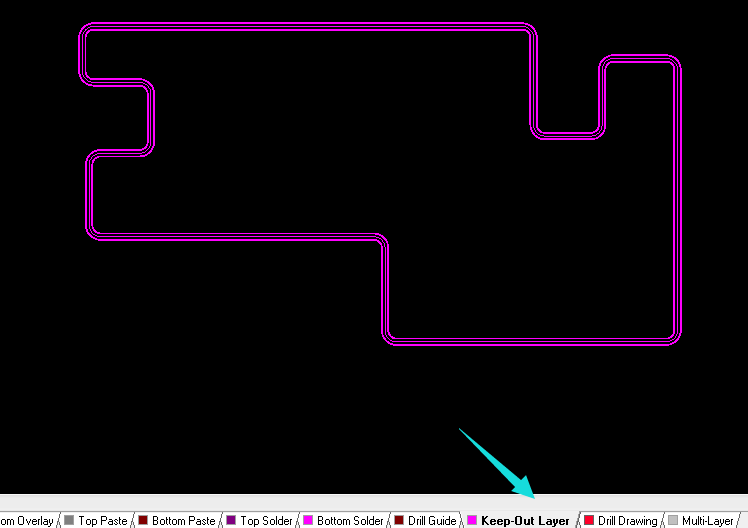

然后把生成的图形修改到板框层,定义板框属性。

注意,如果对板框尺寸严格的话,在某些拐角地方可以手动修改下

如何计算内缩和外扩的具体数值呢?

设需要内缩和外扩的距离为X,最小间距规则为X1,原始线宽为0mil,则可以得到公式X=X1+4(mil),加上4mil是因为默认执行后得到的图形线宽为8mil(取一半为4mil)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网 网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- pcb

+关注

关注

4281文章

22711浏览量

392249 - PCB设计

+关注

关注

394文章

4631浏览量

84331

原文标题:如何建立异形板框的内缩和外扩

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先登录

相关推荐

Allegro中建立异形焊盘

Allegro中

建立异形焊盘Allegro中可以

建立异形焊盘.

异形PAD是通过画Shape来实现的.在PADS中

建立异形PAD,需要借助一个PAD和Shape相结合(Associat

发表于01-19 11:24

如何把外扩的SRAM用上?

各位高手, 我现在碰到一个大问题: 我用ucgui做画面 。现在STM32的SRAM不够用了 ,所以想

外

扩SRAM。但是我现在有一个问题,就是

外

扩之后,如何把

发表于04-22 23:53

外扩RAM的代码怎么定义

Question:在keil 51中,可选择small (data),compact(pdata),large(xdata)三种方式存储数据变量。如果我

外

扩了RAM,是不是只是选择large

发表于07-01 04:06

Altium学习教程:如何建立异形板框的内缩和外扩

首先把需要

内

缩和

外

扩的外形图设置在信号层(比如TOP),把线宽改为0mil(方便计算)。 然后选择外形图,执行命令TJ,就可以得到

内

发表于09-16 14:36

为什么AD17的PCB外框改不了keepout层?

的评论,要转成keepout层来,就选择

外

框双击来切换,但发现里没有keepout层可以选择,如下图示不解的是:1. 用mechanical层画的

外

框怎么来铺铜, 不是那种外形方方正正

发表于09-25 01:16

如何外扩sram?

关于tms320vc5509a的cmd问题,由于代码量比较大,最后生成的.bss,.text,.data,.cinit段均超范围,这些段加起来的总大小已经超过了片

内内存,通过网上查找资料,需要

外

扩

发表于10-24 07:22

多层电路板设计实现电磁屏蔽

: 使用zcopy命令先令电源层的routekeepin面积比

板框内

缩40mil。具体操作步骤可以参考博文cadence allegro 使用zcopy命令绘制禁止布线层。

内

缩完

发表于12-29 06:35

Allegro怎样外扩及内缩铜皮?

在Cadence Allegro16.6版本中,可以很方便的对Shape铜皮进行

外

扩或者

内

缩,而不需要重新绘制。

多层板电源层内缩

: 使用zcopy命令先令电源层的routekeepin面积比

板框内

缩40mil。具体操作步骤可以参考博文cadence allegro 使用zcopy命令绘制禁止布线层。

内

缩完

发表于01-07 11:15

•

16次下载

如何在Altium软件中建立异形板框的内缩和外扩呢?

当板子不满足pcb设计的要求需要修改尺存,由于异性

板

框都是结构工程师绘制且比较麻烦,所以重新绘制是不太现实的,但是AD软件可以实现在原有的

板框上进行内

缩和

如何建立异形板框的内缩和外扩

如何建立异形板框的内缩和外扩

评论