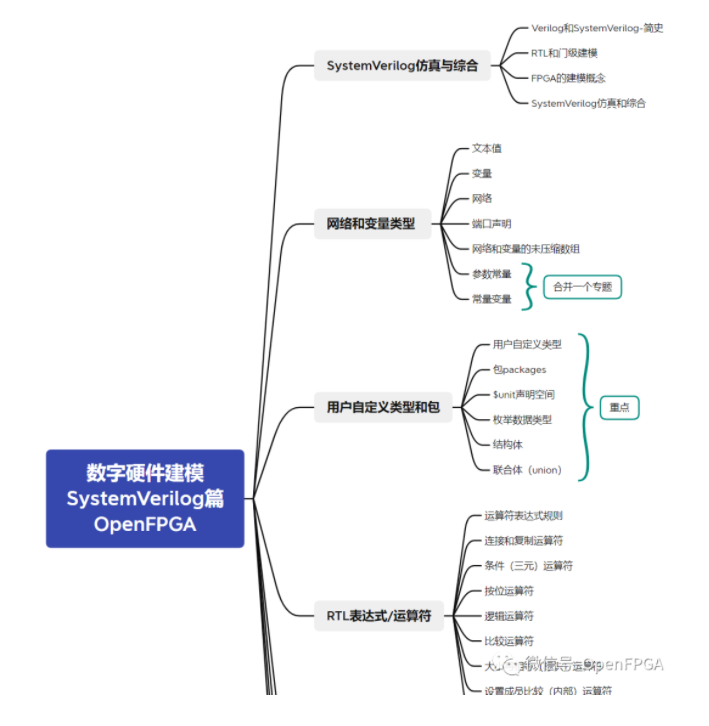

数字硬件建模SystemVerilog-运算符/表达式规则

经过几周的更新,SV核心部分用户自定义类型和包内容已更新完毕,接下来就是RTL表达式和运算符。

马上HDLBits-SystemVerilog版本也开始准备了,基本这一部分完成后就开始更新~

介绍

运算符对操作数执行操作。大多数运算符都有两个操作数。例如,在运算a+b中,+(加法)运算的操作数是a和b。每个操作数都被称为表达式,表达式可以是文字值、变量、网络;函数调用的返回,或另一个操作的结果。表达式有许多影响操作执行方式的特征。这些特征在后面章节中讨论。

4-state(4态)和2-state(2态)操作

表达式可以是2态或4态。2态表达式的每个位只能有0或1的值。2态表达式不能具有高阻抗值(由字母Z表示)、未知值(由字母X表示)或不关心值(也由X表示)。4态表达式可以在表达式的任何位中包含0、l、Z或X的值。

对2态和4态表达式进行运算的规则很简单——当任何操作数都是4态表达式时,运算的结果将是4态表达式。所有操作数都必须是2态表达式才能得到2态结果。如果结果被用作另一个操作的操作数,或在编程语句(如if-else)中求值,则此规则可能会影响其他操作。

该章中建议的编码准则是,RTL建模只使用4态类型。一个主要原因是,运算结果中任何一位的X都可以很好地表明其中一个操作数有问题。当使用2态类型时,设计问题可能会被隐藏,因为操作结果中没有X值指示潜在的错误(之前的文章有详细讨论这部分)。

X-OPTIMISM和X-PESSIMISM

大多数SystemVerilog运算符都是X-optimism,这意味着即使操作数中有X或Z值,该操作也可能产生已知结果。一些SystemVerilog运算符,如算术运算符和关系运算符,是X-pessimism,这意味着,如果任何操作数的任何位具有X或Z值,则结果的所有位将自动为X。

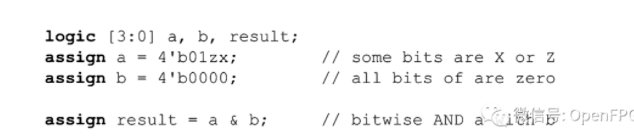

X-OPTIMISM。即使一个或两个操作数的位具有X或Z值,X-optimism也可以产生有效的结果。考虑下面的示例和所示的逻辑值:

该运算的结果是值4’b0000。这是因为&运算符为其操作数的每一位建模一个数字and逻辑门。在数字逻辑中,0与任何值的AND运算将产生0,操作数a中的高阻抗位(由Z表示)和未知位(由X表示)在result中变为0,因为这些位与b中对应的位进行AND运算,b的值为0。这种行为被称为X-OPTIMISM。仿真将有一个已知的结果,即使操作数的位具有X或Z值。

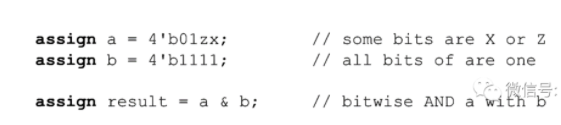

X-OPTIMISM仅适用于仿真可以准确预测实际逻辑门行为的值。在下面的示例中,b操作数是全1而不是全0。

运算的结果是值4’b01xx。对于这些操作数值,X-optimism不适用于最右边的两个位。在实际逻辑门中,高阻抗AND (与)X,可能会产生0或1,其值取决于一系列条件,例如用于构建与门的晶体管类型、晶体管电路的阻抗和电容、工作电压,甚至环境温度。抽象RTL和运算符没有此详细信息。如果没有这些细节,数字仿真无法预测0或1是否会由1与Z相加产生。类似地,X代表未知值,这意味着实际逻辑门值可能是0、1或Z,如果存在这种模糊性,数字仿真无法预测0或1是否会由1与X相加产生。

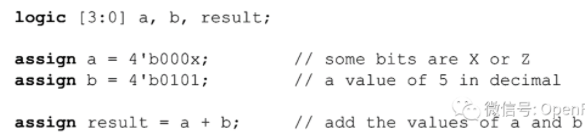

**X-pessimistic。少数SystemVerilog运算符更"悲观"**。如果任何操作数的任何位具有X或Z值,则该操作会自动返回一个值,其中所有位都为X。X-pessimistic如算术运算符(如加法运算符)和关系运算符(如小于运算符)。

运算的结果是4’bxxxx。出现这种X是因为算术加法运算符执行基于数字的加法,而不是按位加法。操作数a的值为4’b000x,这不是一个数字,因此运算结果是一个未知值。

后面会更详细地研究SystemVerilog RTL运算符,以及每个运算符是X-optimistic or X-pessimistic。为了编写能够正确表示的RTL模型,理解这些影响硬件行为至关重要。

运算向量大小和自动向量扩展

运算符的每个操作数可以是任意大小的向量;包括标量(1位)。操作数的向量大小可能会影响操作的执行方式。一个重要的考虑因素是当运算符的操作数是不同的向量大小时。

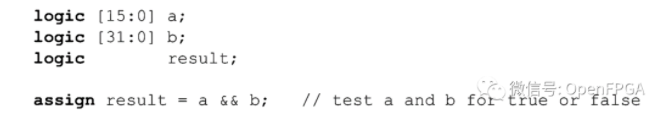

自定义操作数Self-determined operands。有些运算符独立处理每个操作数。操作数是否为不同的向量大小并不重要。这些运算符的操作数称为自定数self-determined。在下面的示例中,运算符执行逻辑“&&”运算,测试两个操作数是否都为真。如果是,则该操作返回的结果为true,否则,该操作返回的结果为false:

操作数a和b是自定数。每个操作数的计算结果可以是真或假,与另一个操作数的向量大小无关。

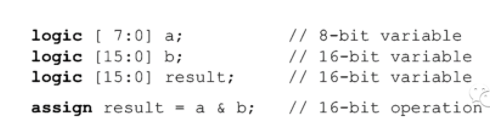

上下文确定的操作数。许多运算符需要将操作数展开为相同的向量大小,然后才能执行操作。这些运算符的操作数被称为上下文确定的操作数(context-determined)。该操作将使最短的操作数向左扩展,使其与最大的操作数的向量大小相同。在下面的示例中,&运算符执行按位AND运算,将每个操作数的每一位相加,并返回布尔结果。

为了将a的每一位与b的每一位进行AND,该操作将两个操作数调整为相同的向量宽度。该操作将检查操作的上下文以确定最大的操作数,然后左扩展较短的操作数以匹配最大操作数的大小。扩展规则如下:

- 如果最左边的位为0或l,且操作数为无符号类型,则操作数为零扩展(每个附加位的值为0)。

- 如果最左边的位是0或l,并且操作数是有符号类型,则操作数是符号扩展的(每个额外的位被赋予最左边位的值或原始值。最左边的位被称为符号位)。

- 如果最左边的位是Z,则操作数是Z扩展的(每个额外的位都有Z的值)。

- 如果最左边的位是X,则操作数是X扩展的(每个附加位的值为X)。

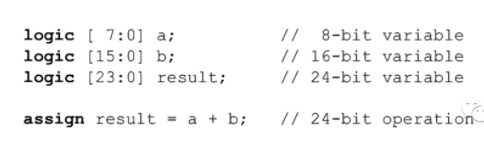

算术运算的上下文推断大小比其他运算符的上下文推断大小更复杂,上下文推断大小不仅考虑运算符的操作数,还考虑赋值语句右侧和左侧所有表达式的向量大小,如以下代码所示:

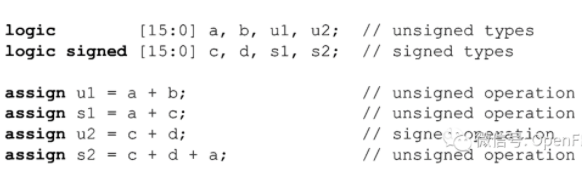

有符号和无符号表达式

算术、比较和移位运算符可以执行有符号或无符号运算。规则很简单——如果执行运算的所有操作数都是有符号的,则执行有符号运算。如果任何受影响的操作数是无符号的,则执行无符号操作——以下代码段说明了这些规则。注释中注明了操作类型。

运算符的符号性完全由操作运算符的操作数决定。它不受赋值语句左侧的符号性影响。

整数(向量)和实数(浮点)表达式

所有SystemVerilog运算符都可以对整数值执行操作。IEEE SystemVerilog标准将整数值称为整数表达式——由一个或多个连续位组成的值。工程师通常将这些整数或整数值称为向量。

SystemVerilog将定点和浮点表达式称为实数表达式。大多数类型的运算都可以在实数表达式上执行,包括:赋值运算、算术运算、逻辑(真/假)运算、比较运算和递增/递减运算。有一些操作无法在实数表达式上执行。这些操作主要包括向量的位处理,例如位和部分选择操作、按位操作、移位操作、连接操作和流操作。

可以对整数和实数表达式的混合执行操作。混合类型运算的规则是,如果任何操作数是实数表达式,则另一个操作数将转换为实数表达式,并执行浮点运算。

| 笔记 |

|---|

| RTL综合编译器通常不支持实数(浮点)表达式。高级综合(HLS)工具可用于复杂的算法设计。浮点和定点设计不在本系列文章的范围之内。 |

-

函数

+关注

关注

3文章

4327浏览量

62567 -

变量

+关注

关注

0文章

613浏览量

28359 -

运算符

+关注

关注

0文章

172浏览量

11078

发布评论请先 登录

相关推荐

JAVA语言的运算符及表达式

关于C语言的运算符和表达式--笔记1

基于运算符信息的数学表达式检索技术

运算符/表达式规则

运算符/表达式规则

评论