今天还是更新状态机,状态机基本是整个HDL中的核心,合理、高效地使用状态机,是数字电路中的重要技能。

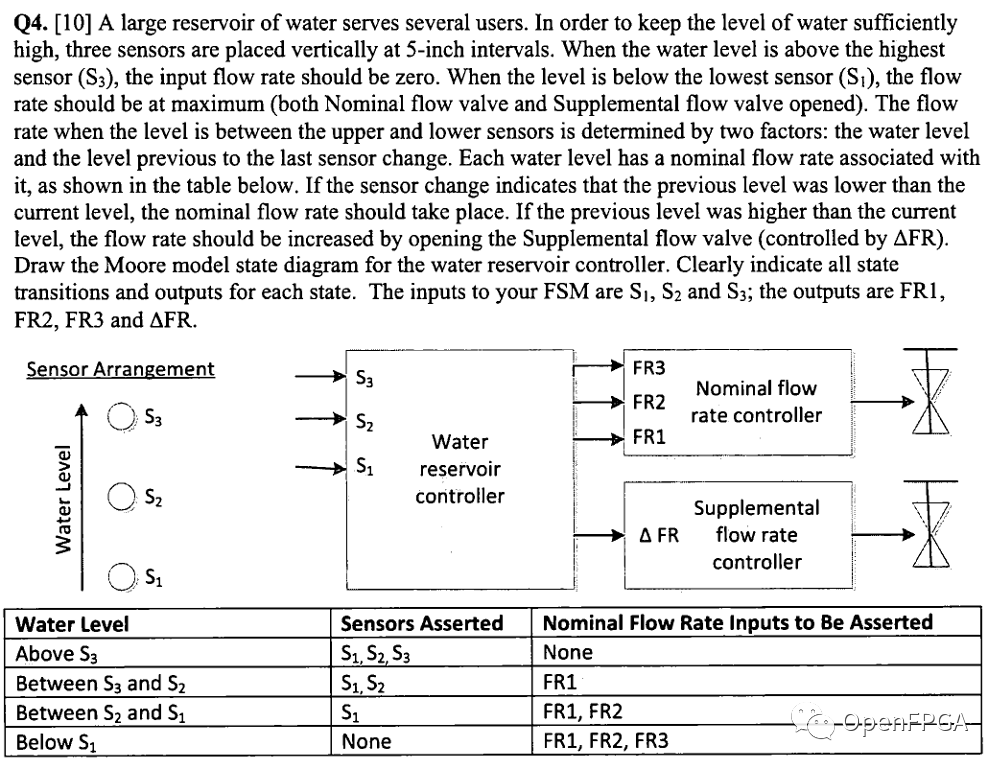

题目说明

图片来自HDLBits

模块端口声明

moduletop_module( inputclk, inputreset, input[3:1]s, outputfr3, outputfr2, outputfr1, outputdfr );

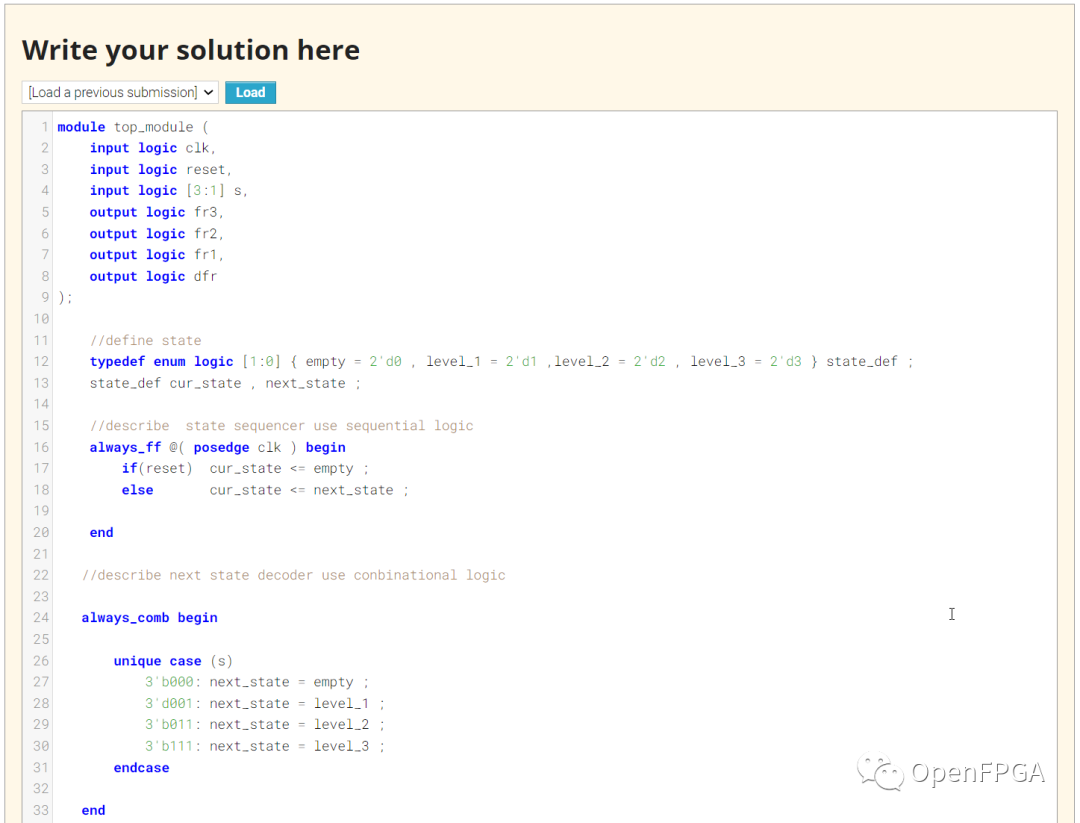

题目解析

moduletop_module( inputlogicclk, inputlogicreset, inputlogic[3:1]s, outputlogicfr3, outputlogicfr2, outputlogicfr1, outputlogicdfr ); //definestate typedefenumlogic[1:0]{empty=2'd0,level_1=2'd1,level_2=2'd2,level_3=2'd3}state_def; state_defcur_state,next_state; //describestatesequencerusesequentiallogic always_ff@(posedgeclk)begin if(reset)cur_state<= empty ; else cur_state <= next_state ; end //describe next state decoder use conbinational logic always_comb begin unique case (s) 3'b000: next_state = empty ; 3'd001: next_state = level_1 ; 3'b011: next_state = level_2 ; 3'b111: next_state = level_3 ; endcase end //describe output decoder use conbinational and sequential logic // decoder output fr1~fr3 assign fr3 = (cur_state == empty) ; assign fr2 = (cur_state == empty) || (cur_state == level_1) ; assign fr1 = (cur_state == empty) || (cur_state == level_1) || (cur_state == level_2) ; // decoder output dfr var logic set_dfr , reset_dfr ; assign set_dfr = ((next_state == empty) && (cur_state != empty)) || ((next_state == level_1) && (cur_state != level_1) && (cur_state != empty)) || ((next_state == level_2) && (cur_state == level_3)) ; assign reset_dfr = ((next_state == level_3) && (cur_state != level_3)) || ((next_state == level_2) && (cur_state != level_2) && (cur_state != level_3)) || ((next_state == level_1) && (cur_state == empty)) ; always_ff @( posedge clk ) begin if (reset) begin dfr <= 1'd1 ; end else if (set_dfr) begin dfr <= 1'd1 ; end else if (reset_dfr) begin dfr <= 1'd0 ; end else begin dfr <= dfr ; end end endmodule

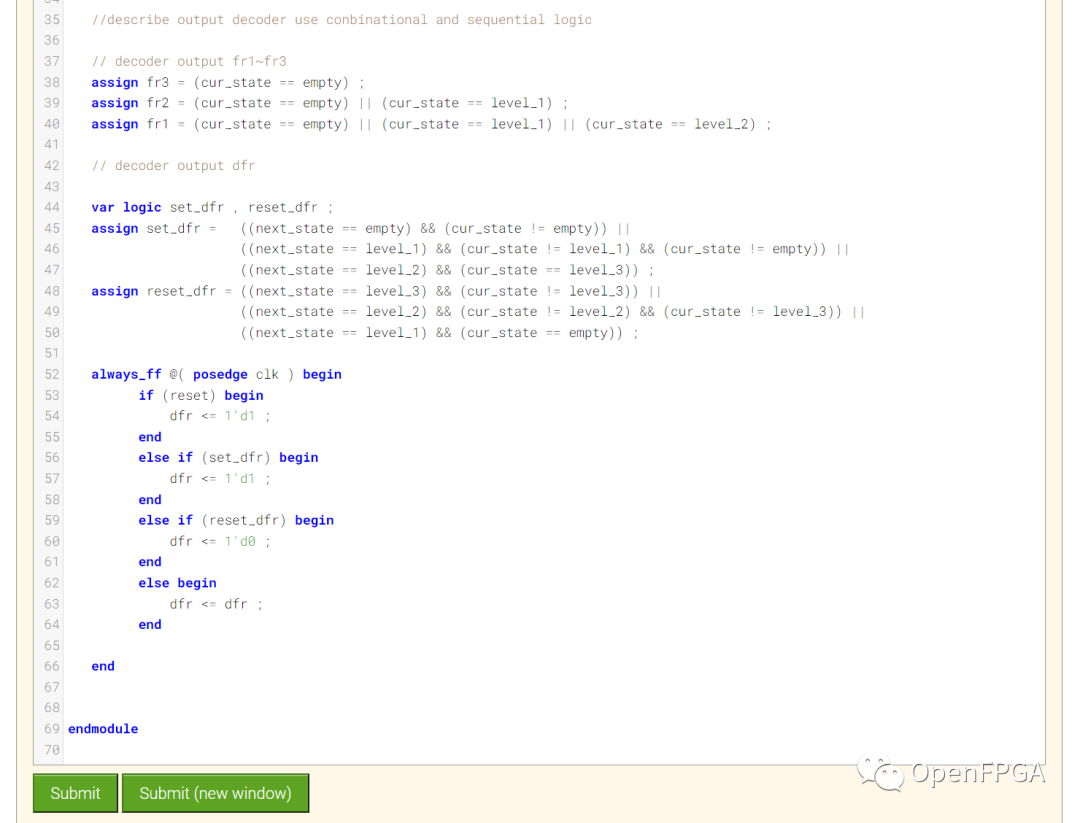

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 127-Lemmings1

题目说明

旅鼠(Lemmings)游戏涉及相当简单的小动物。所以我们将使用有限状态机对其进行建模。

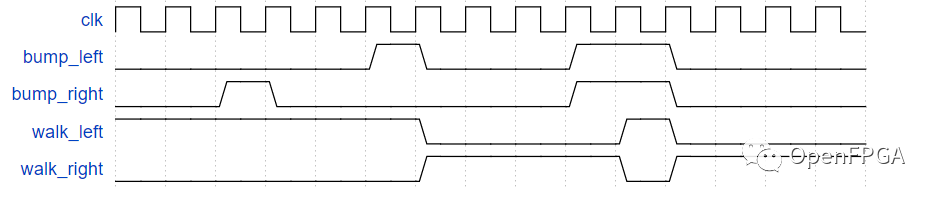

在 Lemmings 的 2D 世界中,Lemmings 可以处于两种状态之一:向左行走或向右行走。如果遇到障碍物,它会改变方向。

特别是,如果旅鼠在左边被撞到,它就会向右走。

如果它被撞到右边,它就会向左走。

如果它的两侧同时受到碰撞,它仍然会切换方向。

实现具有两个状态、两个输入和一个输出的 Moore 状态机来vwin 此行为。

图片来自HDLBits

模块端口声明

moduletop_module( inputclk, inputareset,//FreshlybrainwashedLemmingswalkleft. inputbump_left, inputbump_right, outputwalk_left, outputwalk_right);

题目解析

我们首先需要找出状态转移规则。具体如下图所示:

找到转移关系后,后续的解答就和之前题目相同。

moduletop_module(

inputlogicclk,

inputlogicareset,//FreshlybrainwashedLemmingswalkleft.

inputlogicbump_left,

inputlogicbump_right,

outputlogicwalk_left,

outputlogicwalk_right);

//definestate

typedefenumlogic{left=1'b0,right=1'b1}state_def;

state_defstate,next_state;

//Statetransitionlogic

always_combbegin

case(state)

left:begin

if(bump_left)next_state=right;

elsenext_state=left;

end

right:begin

if(bump_right)next_state=left;

elsenext_state=right;

end

endcase

end

//Stateflip-flopswithasynchronousreset

always@(posedgeclk,posedgeareset)begin

if(areset)state<= left ;

else state <= next_state ;

end

// Output logic

assign walk_left = (state == left );

assign walk_right = (state == right );

endmodule

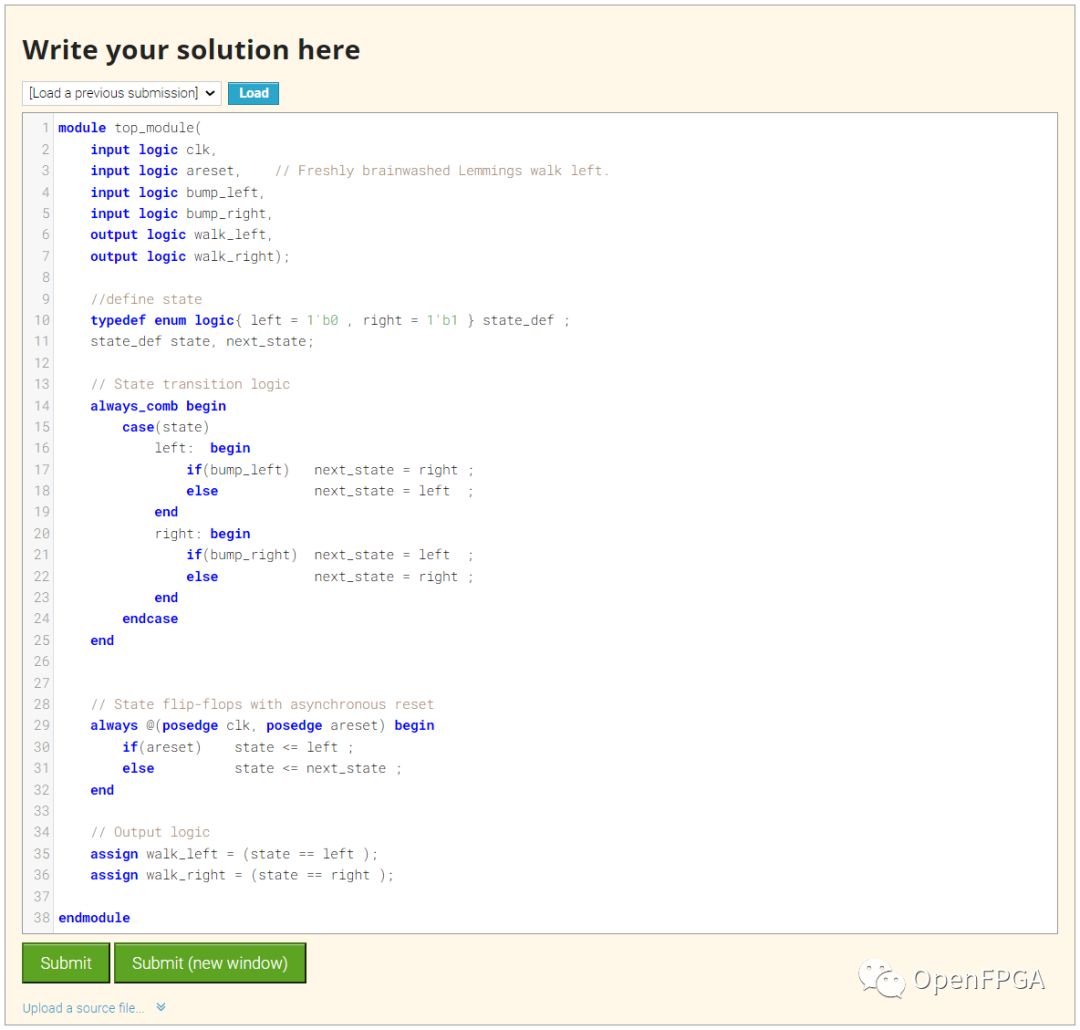

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

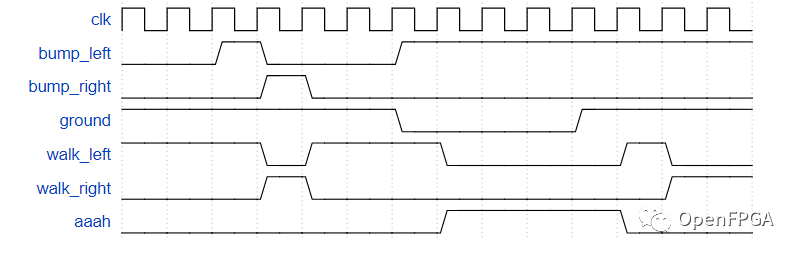

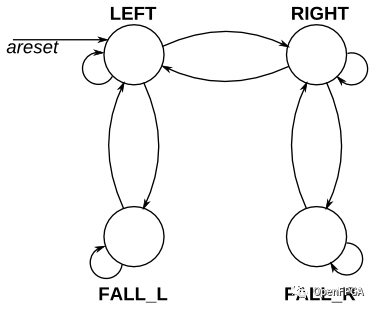

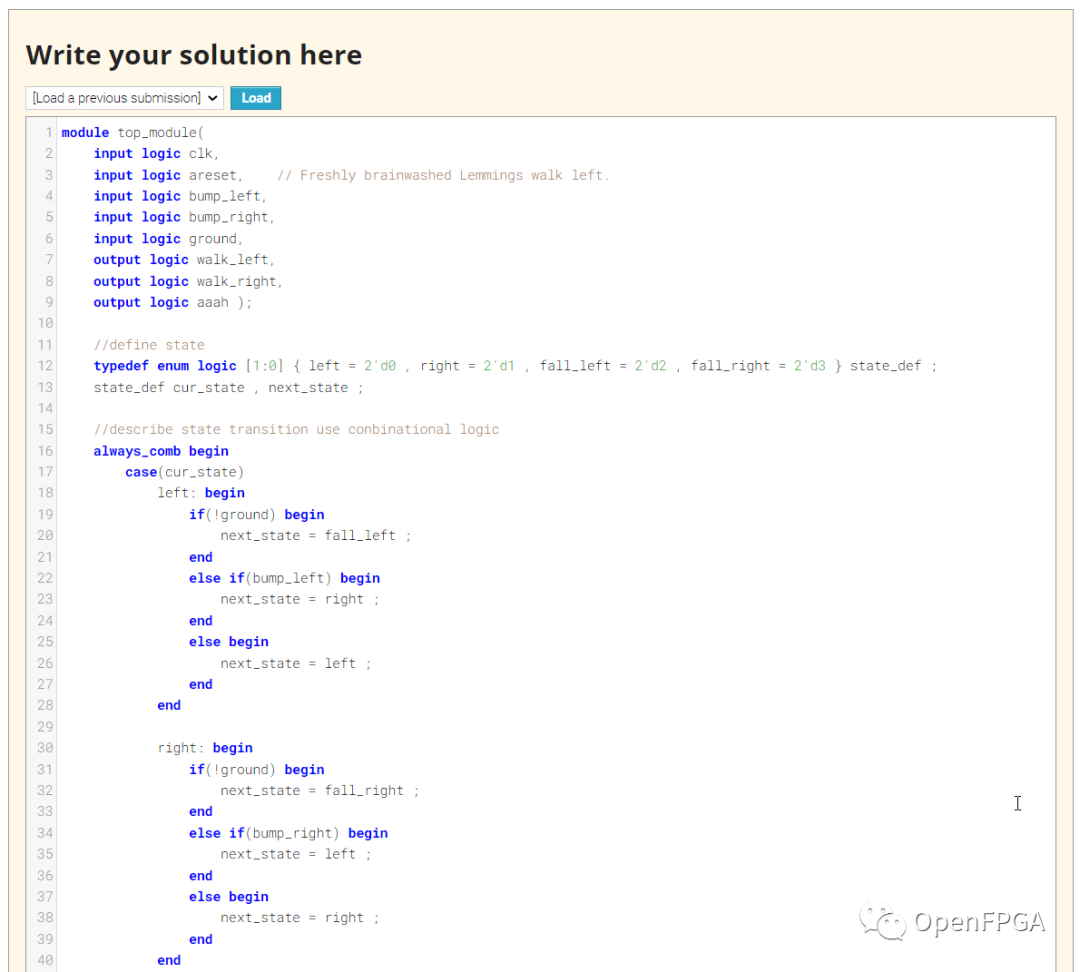

Problem 128-Lemmings2

题目说明

在上一题基础上,除了左右行走之外,如果地面在它们下方消失,旅鼠还会掉落(并且大概会发出“啊啊!”)。

除了左右行走和碰撞时改变方向外,当ground=0时,旅鼠会倒下并说“啊啊!”。当地面重新出现 ( ground=1 ) 时,旅鼠将继续沿与坠落前相同的方向行走。跌倒时被撞不影响行走方向,与地面消失(但尚未跌落)同周期被撞,或跌倒时地面再次出现,也不影响行走方向。

构建一个模拟此行为的有限状态机。

图片来自HDLBits

模块端口声明

moduletop_module( inputclk, inputload, input[255:0]data, output[255:0]q); endmodule

题目解析

还是优先画出状态转移图:

moduletop_module(

inputlogicclk,

inputlogicareset,//FreshlybrainwashedLemmingswalkleft.

inputlogicbump_left,

inputlogicbump_right,

inputlogicground,

outputlogicwalk_left,

outputlogicwalk_right,

outputlogicaaah);

//definestate

typedefenumlogic[1:0]{left=2'd0,right=2'd1,fall_left=2'd2,fall_right=2'd3}state_def;

state_defcur_state,next_state;

//describestatetransitionuseconbinationallogic

always_combbegin

case(cur_state)

left:begin

if(!ground)begin

next_state=fall_left;

end

elseif(bump_left)begin

next_state=right;

end

elsebegin

next_state=left;

end

end

right:begin

if(!ground)begin

next_state=fall_right;

end

elseif(bump_right)begin

next_state=left;

end

elsebegin

next_state=right;

end

end

fall_left:begin

if(ground)begin

next_state=left;

end

elsebegin

next_state=fall_left;

end

end

fall_right:begin

if(ground)begin

next_state=right;

end

elsebegin

next_state=fall_right;

end

end

endcase

end

//describestatesequencerusesequentiallogic

always_ff@(posedgeclkorposedgeareset)begin

if(areset)begin

cur_state<= left ;

end

else begin

cur_state <= next_state ;

end

end

//describe output decoder use conbinational logic

assign walk_left = (cur_state == left) ;

assign walk_right = (cur_state == right);

assign aaah = (cur_state == fall_left) || (cur_state == fall_right) ;

endmodule

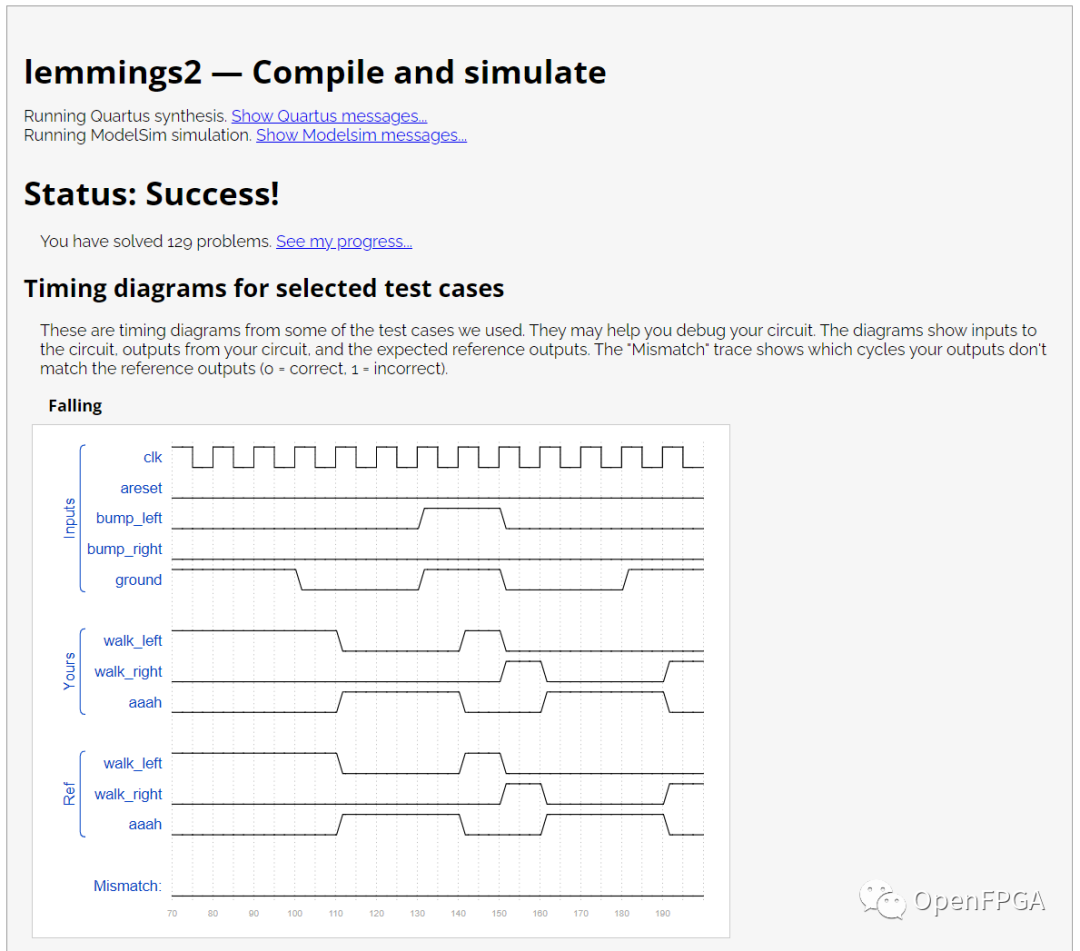

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

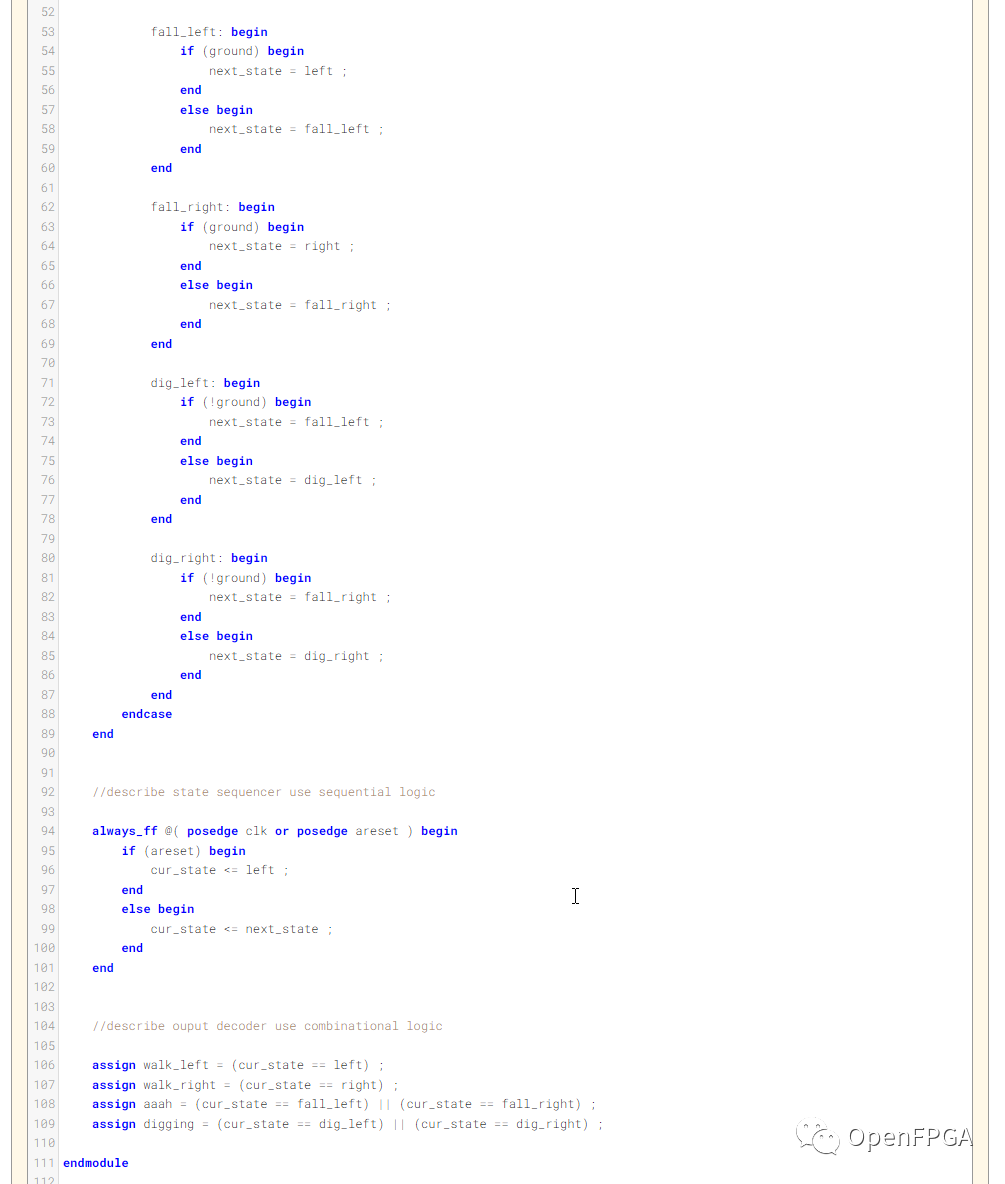

Problem 129-Lemmings3

题目说明

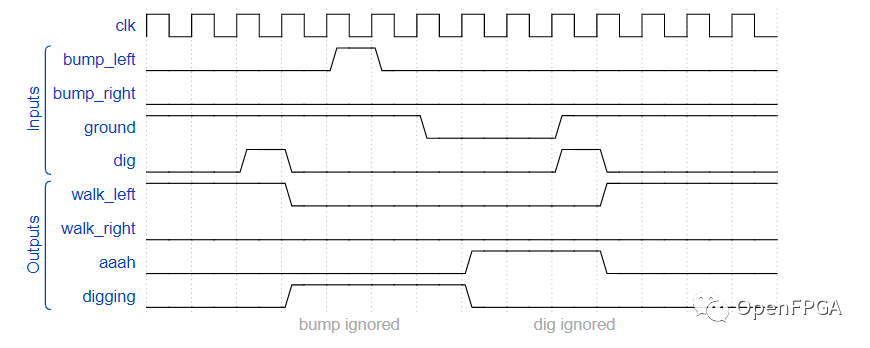

在Lemmings1和Lemmings2基础上。

除了行走和坠落之外,旅鼠有时会被告知做一些有用的事情,比如挖掘(它在dig=1时开始挖掘)。如果旅鼠当前正在地面上行走(ground=1且未掉落),则它可以挖掘,并且会继续挖掘直到到达另一侧(ground=0)。到那时,由于没有地面,它会掉落(啊啊!),然后在它再次着地后继续沿原来的方向行走。与掉落一样,在挖掘时被碰撞没有任何效果,而在掉落或没有地面时被告知挖掘将被忽略。

(换句话说,行走的旅鼠可以掉落、挖掘或转换方向。如果满足其中一个以上条件,则掉落的优先级高于挖掘,而挖掘的优先级高于转换方向。)

扩展您的有限状态机来模拟这种行为。

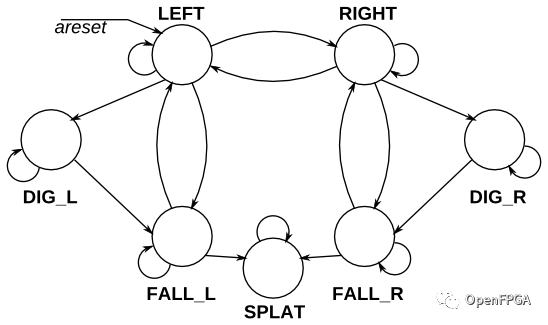

图片来自HDLBits

模块端口声明

moduletop_module( inputclk, inputareset,//FreshlybrainwashedLemmingswalkleft. inputbump_left, inputbump_right, inputground, inputdig, outputwalk_left, outputwalk_right, outputaaah, outputdigging);

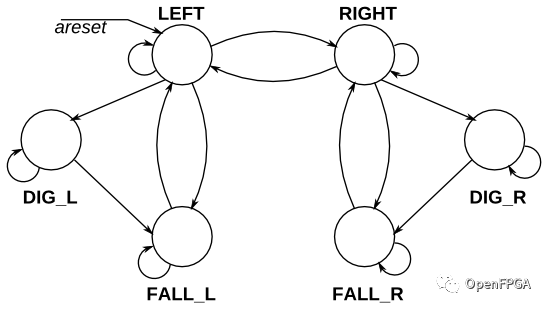

题目解析

状态转移图:

moduletop_module(

inputlogicclk,

inputlogicareset,//FreshlybrainwashedLemmingswalkleft.

inputlogicbump_left,

inputlogicbump_right,

inputlogicground,

inputlogicdig,

outputlogicwalk_left,

outputlogicwalk_right,

outputlogicaaah,

outputlogicdigging);

//definestate

typedefenumlogic[2:0]{left=3'd0,right=3'd1,

fall_left=3'd2,fall_right=3'd3,

dig_left=3'd4,dig_right=3'd5}state_def;

state_defcur_state,next_state;

//describenextstatetransitionusecombinationallogic

always_combbegin

case(cur_state)

left:begin

if(!ground)begin

next_state=fall_left;

end

elseif(dig)begin

next_state=dig_left;

end

elseif(bump_left)begin

next_state=right;

end

elsebegin

next_state=left;

end

end

right:begin

if(!ground)begin

next_state=fall_right;

end

elseif(dig)begin

next_state=dig_right;

end

elseif(bump_right)begin

next_state=left;

end

elsebegin

next_state=right;

end

end

fall_left:begin

if(ground)begin

next_state=left;

end

elsebegin

next_state=fall_left;

end

end

fall_right:begin

if(ground)begin

next_state=right;

end

elsebegin

next_state=fall_right;

end

end

dig_left:begin

if(!ground)begin

next_state=fall_left;

end

elsebegin

next_state=dig_left;

end

end

dig_right:begin

if(!ground)begin

next_state=fall_right;

end

elsebegin

next_state=dig_right;

end

end

endcase

end

//describestatesequencerusesequentiallogic

always_ff@(posedgeclkorposedgeareset)begin

if(areset)begin

cur_state<= left ;

end

else begin

cur_state <= next_state ;

end

end

//describe ouput decoder use combinational logic

assign walk_left = (cur_state == left) ;

assign walk_right = (cur_state == right) ;

assign aaah = (cur_state == fall_left) || (cur_state == fall_right) ;

assign digging = (cur_state == dig_left) || (cur_state == dig_right) ;

endmodule

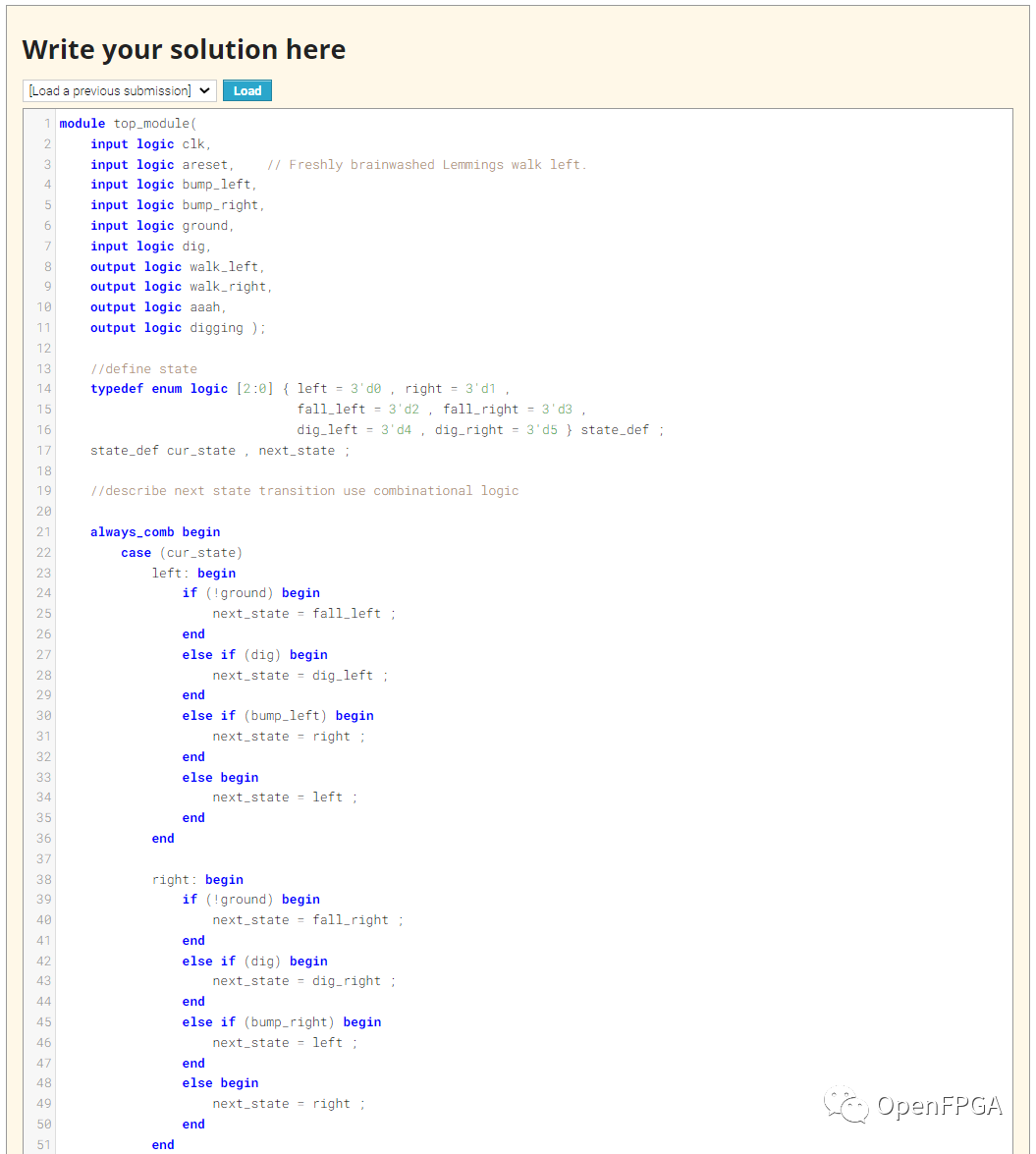

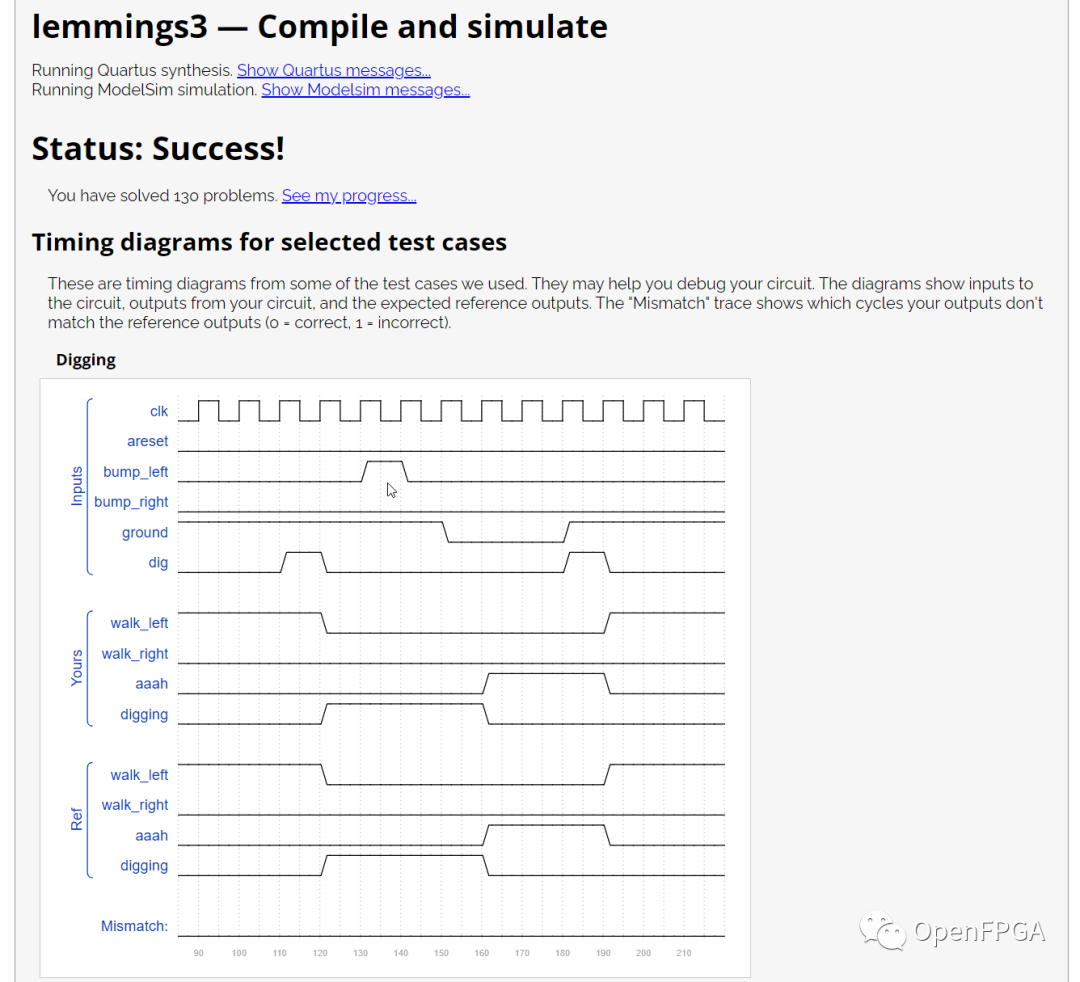

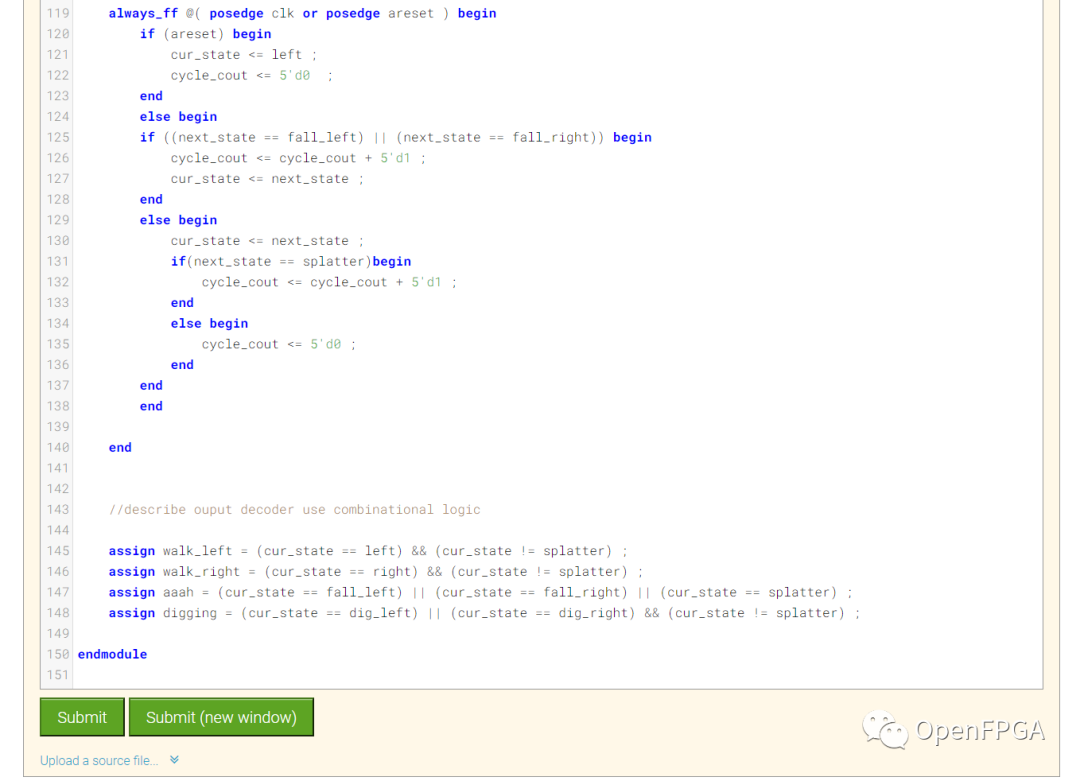

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

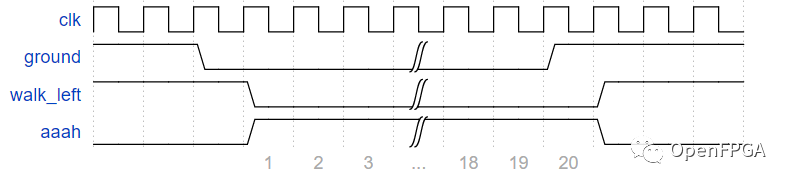

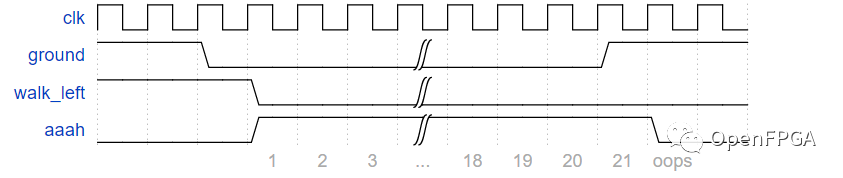

Problem 130-Lemmings4

题目说明

在Lemmings1、Lemmings2和Lemmings3基础上:

尽管旅鼠可以行走、跌倒和挖掘,但旅鼠并非无懈可击。如果旅鼠掉落的时间太长然后撞到地面,它可能会死亡。特别是,如果旅鼠掉落超过 20 个时钟周期然后撞到地面,它将永远停止行走、掉落或挖掘(所有 4 个输出变为 0)(或直到 FSM 复位)。旅鼠在撞到地面之前可以跌落多远没有上限。旅鼠只会在撞到地面时死亡;它们不会死亡到半空中。

扩展之前的有限状态机来模拟这种行为。

跌倒 20 个周期是可以生存的:

图片来自HDLBits

下降 21 个周期会导致死亡:

图片来自HDLBits

模块端口声明

moduletop_module( inputclk, inputareset,//FreshlybrainwashedLemmingswalkleft. inputbump_left, inputbump_right, inputground, inputdig, outputwalk_left, outputwalk_right, outputaaah, outputdigging);

题目解析

状态转移图:

moduletop_module(

inputlogicclk,

inputlogicareset,//FreshlybrainwashedLemmingswalkleft.

inputlogicbump_left,

inputlogicbump_right,

inputlogicground,

inputlogicdig,

outputlogicwalk_left,

outputlogicwalk_right,

outputlogicaaah,

outputlogicdigging);

//definestate

typedefenumlogic[2:0]{left=3'd0,right=3'd1,

fall_left=3'd2,fall_right=3'd3,

dig_left=3'd4,dig_right=3'd5,

splatter=3'd6,aaah_reset=3'd7

}state_def;

state_defcur_state,next_state;

varlogic[4:0]cycle_cout;

//describenextstatetransitionusecombinationallogic

always_combbegin

case(cur_state)

left:begin

if(!ground)begin

next_state=fall_left;

end

elseif(dig)begin

next_state=dig_left;

end

elseif(bump_left)begin

next_state=right;

end

elsebegin

next_state=left;

end

end

right:begin

if(!ground)begin

next_state=fall_right;

end

elseif(dig)begin

next_state=dig_right;

end

elseif(bump_right)begin

next_state=left;

end

elsebegin

next_state=right;

end

end

fall_left:begin

if(ground)begin

next_state=left;

end

elsebegin

if(cycle_cout==5'd20)begin

next_state=splatter;

end

elsebegin

next_state=fall_left;

end

end

end

fall_right:begin

if(ground)begin

next_state=right;

end

elsebegin

if(cycle_cout==5'd20)begin

next_state=splatter;

end

elsebegin

next_state=fall_right;

end

end

end

dig_left:begin

if(!ground)begin

next_state=fall_left;

end

elsebegin

next_state=dig_left;

end

end

dig_right:begin

if(!ground)begin

next_state=fall_right;

end

elsebegin

next_state=dig_right;

end

end

splatter:begin

if(ground)begin

next_state=aaah_reset;

end

elsebegin

next_state=splatter;

end

end

aaah_reset:begin

next_state=aaah_reset;

end

endcase

end

//describestatesequencerusesequentiallogic

always_ff@(posedgeclkorposedgeareset)begin

if(areset)begin

cur_state<= left ;

cycle_cout <= 5'd0 ;

end

else begin

if ((next_state == fall_left) || (next_state == fall_right)) begin

cycle_cout <= cycle_cout + 5'd1 ;

cur_state <= next_state ;

end

else begin

cur_state <= next_state ;

if(next_state == splatter)begin

cycle_cout <= cycle_cout + 5'd1 ;

end

else begin

cycle_cout <= 5'd0 ;

end

end

end

end

//describe ouput decoder use combinational logic

assign walk_left = (cur_state == left) && (cur_state != splatter) ;

assign walk_right = (cur_state == right) && (cur_state != splatter) ;

assign aaah = (cur_state == fall_left) || (cur_state == fall_right) || (cur_state == splatter) ;

assign digging = (cur_state == dig_left) || (cur_state == dig_right) && (cur_state != splatter) ;

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

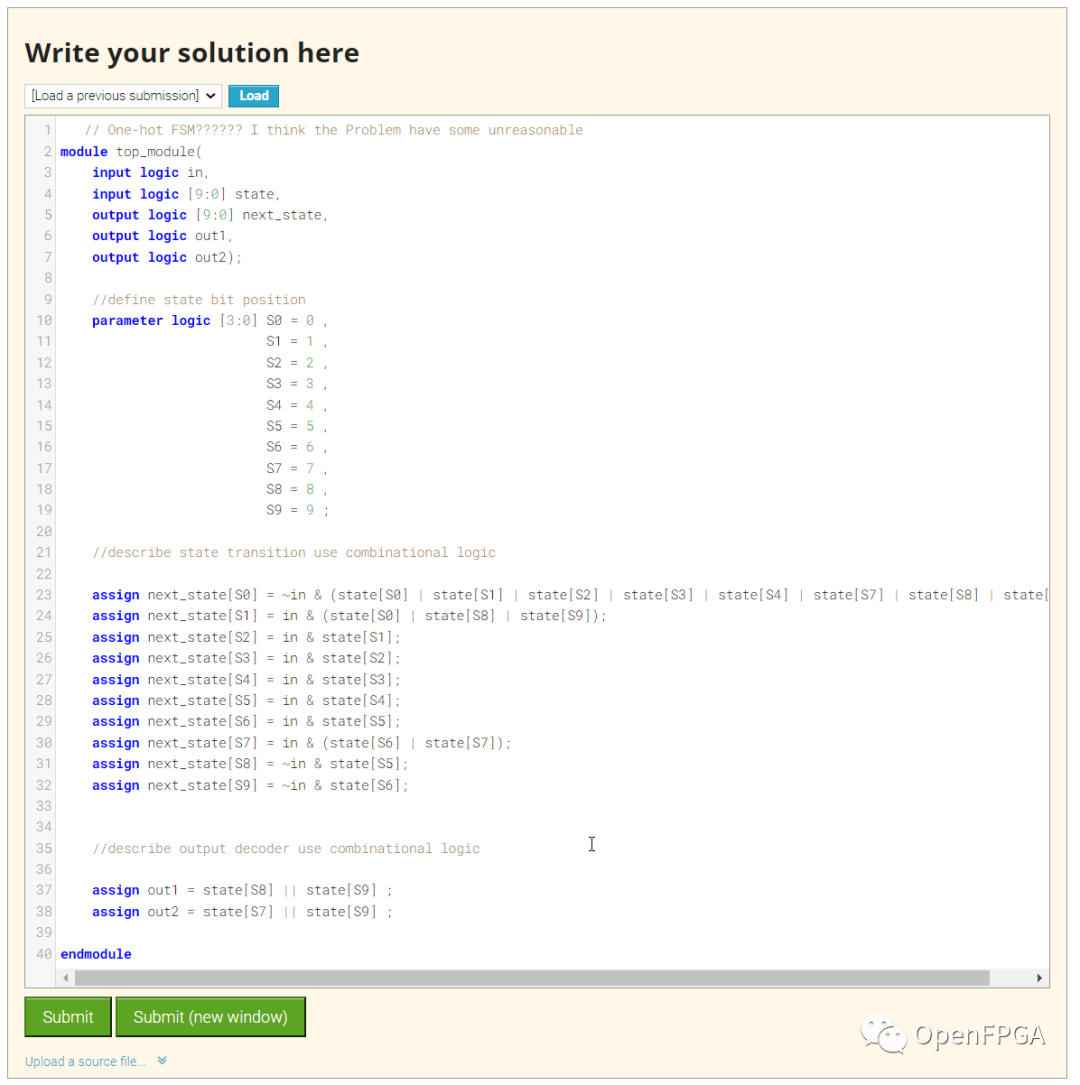

Problem 131-Fsm_onehot

题目说明

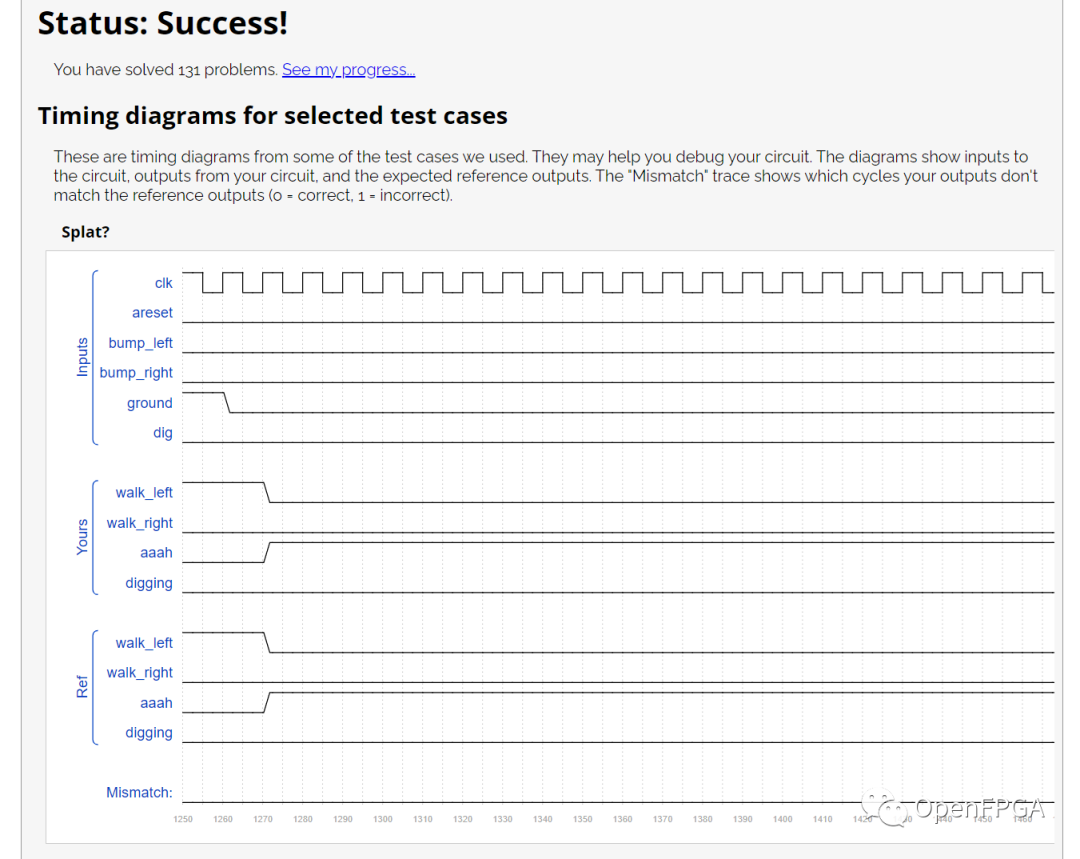

给定以下具有 1 个输入和 2 个输出的状态机:

图片来自HDLBits

假设这个状态机使用 one-hot 编码,其中state[0]到state[9]分别对应于状态 S0 到 S9。除非另有说明,否则输出为零。

实现状态机的状态转换逻辑和输出逻辑部分(但不是状态触发器)。在state[9:0]中获得了当前状态,并且必须生成next_state[9:0]和两个输出。

假设使用one-hot编码,通过检查推导出逻辑方程。(测试平台将使用非热输入进行测试,以确保你不会尝试做更复杂的事情)。

模块端口声明

moduletop_module( inputin, input[9:0]state, output[9:0]next_state, outputout1, outputout2);

题目解析

可以通过查看状态转换图的转移的路径来导出独热码状态转换逻辑的逻辑方程式。

仔细观察发现在当前状态state为正常独热码(0x100, 0x1, 0x80)的时候,输出的波形是正确的,但是输入不是独热码(0x900, 0x180)的时候,输出就不正常了,这就是这道题所考察的地方,写错的同学自行翻看前一个独热码状态机的题目(Problem 125 fsm3onehot)再看正确答案。

//One-hotFSM??????IthinktheProblemhavesomeunreasonable moduletop_module( inputlogicin, inputlogic[9:0]state, outputlogic[9:0]next_state, outputlogicout1, outputlogicout2); //definestatebitposition parameterlogic[3:0]S0=0, S1=1, S2=2, S3=3, S4=4, S5=5, S6=6, S7=7, S8=8, S9=9; //describestatetransitionusecombinationallogic assignnext_state[S0]=~in&(state[S0]|state[S1]|state[S2]|state[S3]|state[S4]|state[S7]|state[S8]|state[S9]); assignnext_state[S1]=in&(state[S0]|state[S8]|state[S9]); assignnext_state[S2]=in&state[S1]; assignnext_state[S3]=in&state[S2]; assignnext_state[S4]=in&state[S3]; assignnext_state[S5]=in&state[S4]; assignnext_state[S6]=in&state[S5]; assignnext_state[S7]=in&(state[S6]|state[S7]); assignnext_state[S8]=~in&state[S5]; assignnext_state[S9]=~in&state[S6]; //describeoutputdecoderusecombinationallogic assignout1=state[S8]||state[S9]; assignout2=state[S7]||state[S9]; endmodule

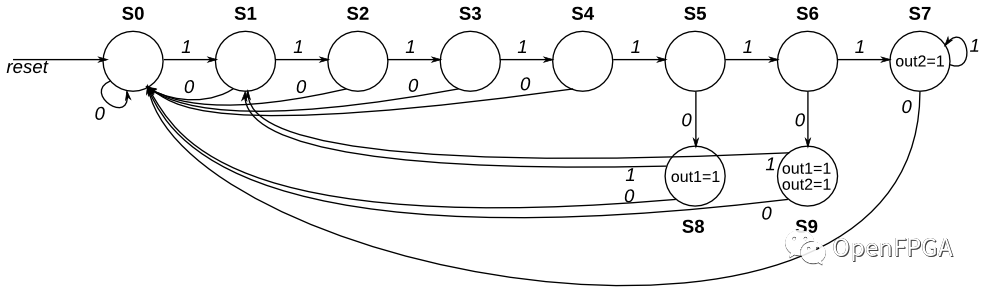

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

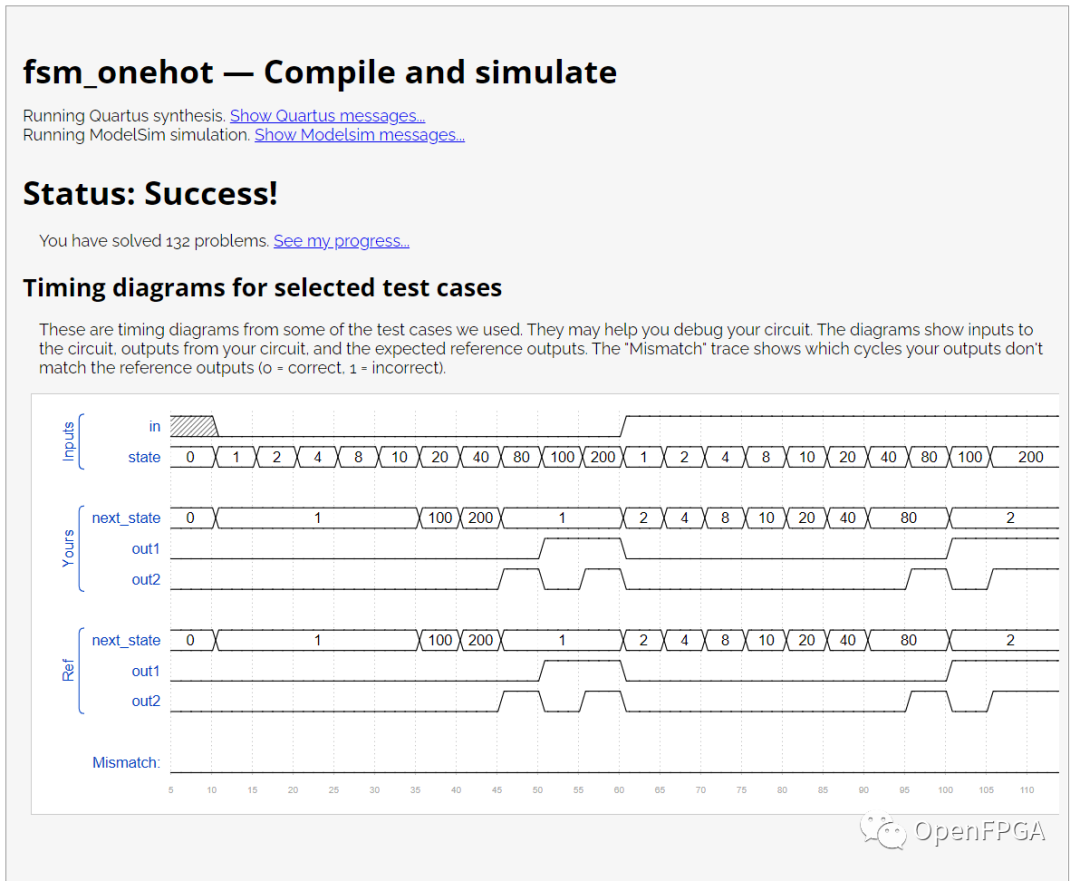

Problem 132-Fsm_ps2

题目说明

PS/2 鼠标协议发送三个字节长的消息。但是,在连续的字节流中,消息的开始和结束位置并不明显。唯一的迹象是每个三字节消息的第一个字节始终具有bit[3]=1(但其他两个字节的 bit[3] 可能为 1 或 0,具体取决于数据)。

我们想要一个有限状态机,它会在给定输入字节流时搜索消息边界。我们将使用的算法是丢弃字节,直到我们看到一个带有bit[3]=1的字节。然后我们假设这是消息的第 1 个字节,并在接收到所有 3 个字节(完成)后发出消息接收信号。

FSM 应在成功接收到每条消息的第三个字节后立即在周期内发出完成信号。

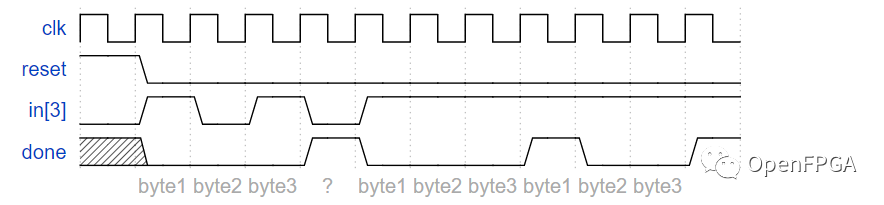

一些时序图来解释所需的行为

在没有错误的情况下,每三个字节组成一条消息:

图片来自HDLBits

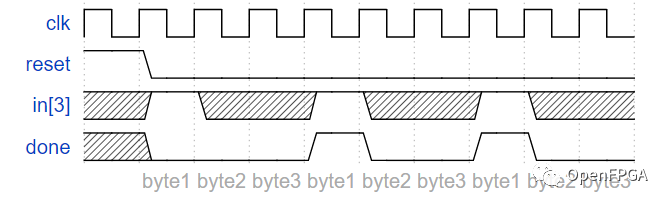

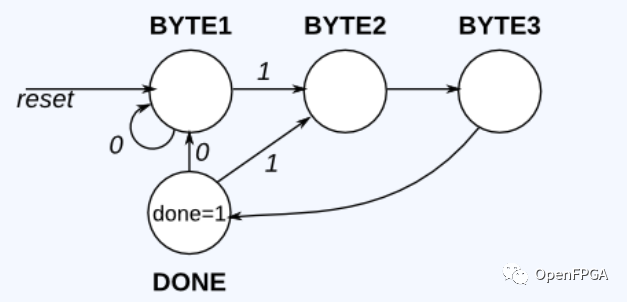

发生错误时,搜索字节 1:

请注意,这与1xx序列识别器不同。此处不允许重叠序列:

图片来自HDLBits

模块端口声明

moduletop_module( inputclk, input[7:0]in, inputreset,//Synchronousreset outputdone);

题目解析

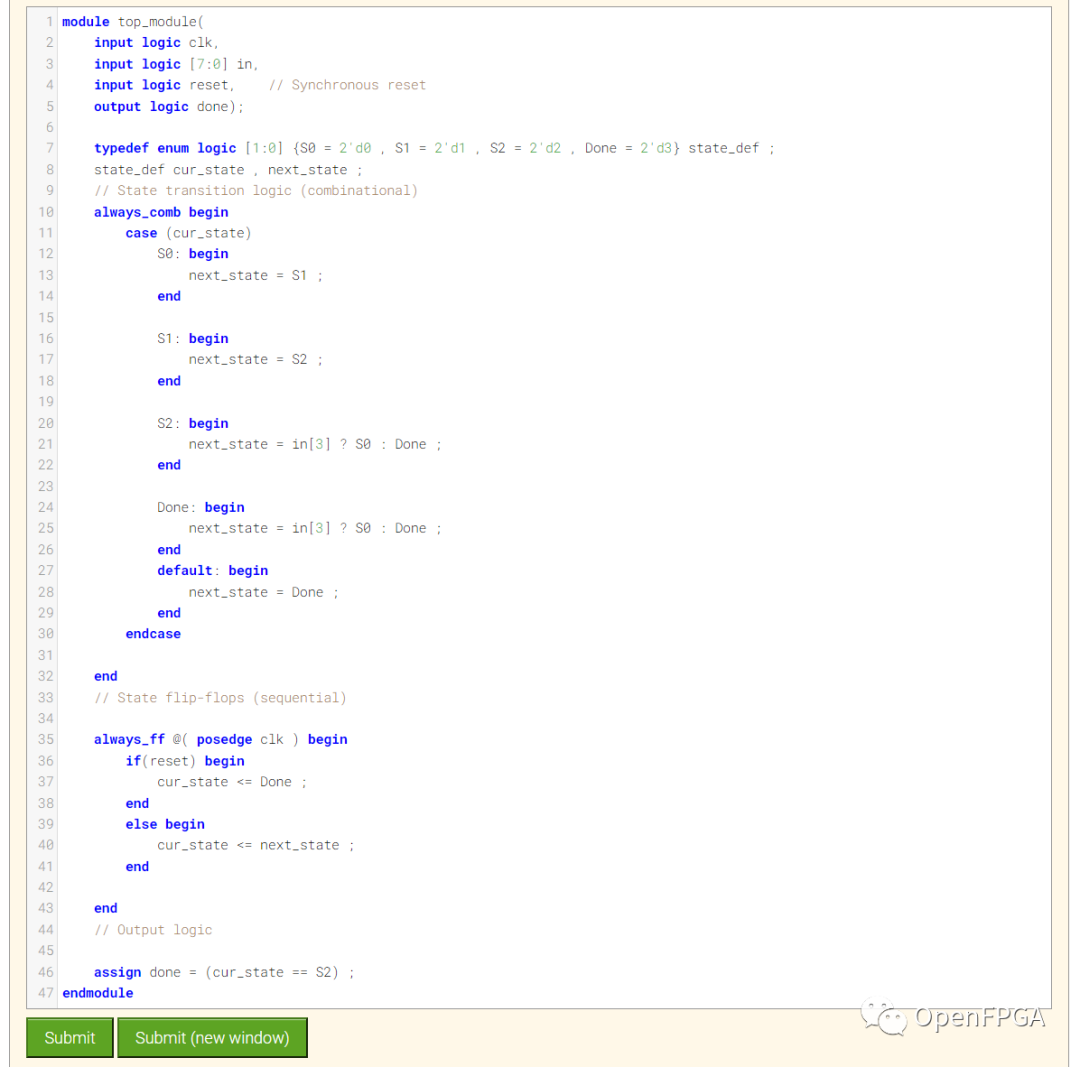

尽管in[7:0]是一个字节,但状态机使用一个输入in[3]就够了。

该状态机可能有4个状态,但其中的三种状态没有输出是为了最后一个状态输出done桌准备。而对于接收到的某个消息,仅需一个时钟周期即可判断完成。

状态图。。。

moduletop_module(

inputlogicclk,

inputlogic[7:0]in,

inputlogicreset,//Synchronousreset

outputlogicdone);

typedefenumlogic[1:0]{S0=2'd0,S1=2'd1,S2=2'd2,Done=2'd3}state_def;

state_defcur_state,next_state;

//Statetransitionlogic(combinational)

always_combbegin

case(cur_state)

S0:begin

next_state=S1;

end

S1:begin

next_state=S2;

end

S2:begin

next_state=in[3]?S0:Done;

end

Done:begin

next_state=in[3]?S0:Done;

end

default:begin

next_state=Done;

end

endcase

end

//Stateflip-flops(sequential)

always_ff@(posedgeclk)begin

if(reset)begin

cur_state<= Done ;

end

else begin

cur_state <= next_state ;

end

end

// Output logic

assign done = (cur_state == S2) ;

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

Problem 133-Fsm_ps2data

题目说明

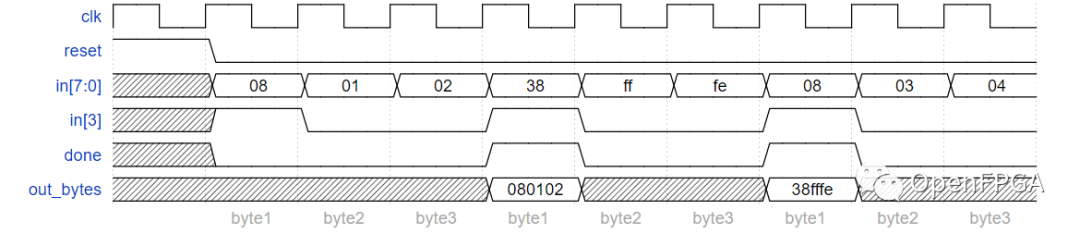

现在,已经写了一个PS/2接口的状态机,该状态机可以标识PS/2字节流中的三字节消息。请在这个状态机中添加一条数据路径,该数据路径可以在接收数据包的同时输出24bits(3字节)的消息(out_bytes[23:16]为第一字节,out_bytes[15:8]为第二字节,以此类推)。

当发出接收完成信号done时,out_bytes必须是有效的,其他时候可以输出任何的内容(即不在乎输出什么。)

小提示:使用前一题Problem 134 PS/2 packet parser / Fsm ps2 中的状态机,并添加用于捕捉输入字节的数据路径即可。

图片来自HDLBits

模块端口声明

moduletop_module( inputclk, input[7:0]in, inputreset,//Synchronousreset output[23:0]out_bytes, outputdone);

题目解析

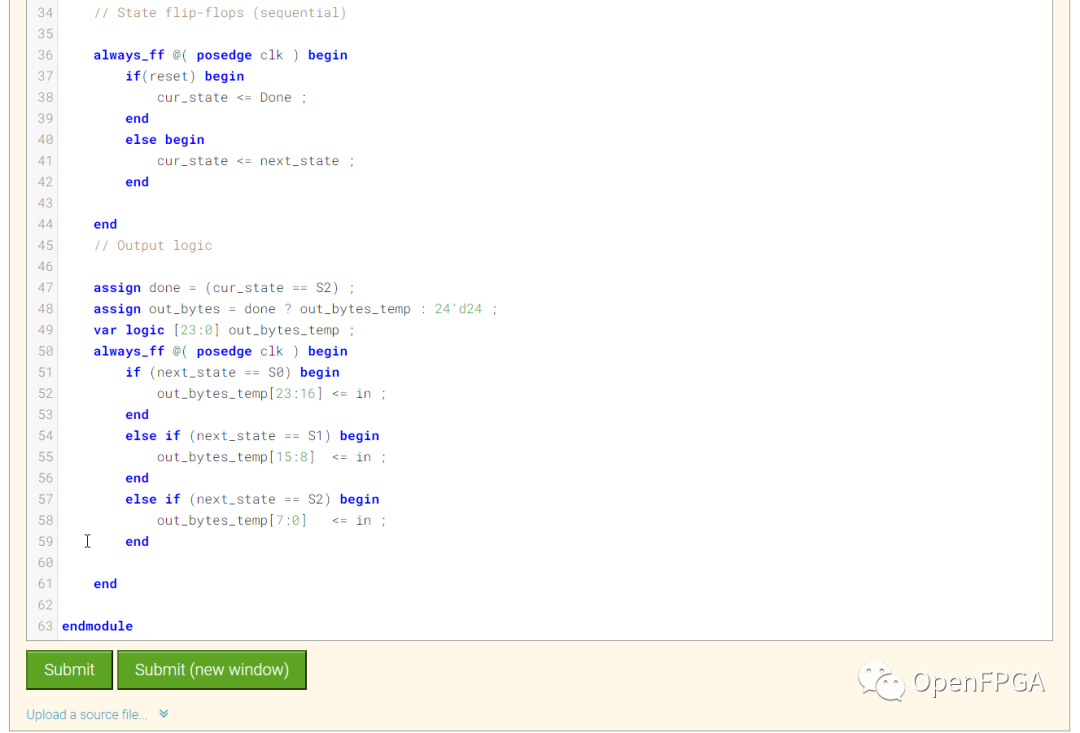

本题在前一题的三个没有输出动作的状态上添加out_bytes等于输入即可完成。值得注意的是状态4可以跳转为状态2,所以状态4也需要对out_bytes赋值。

moduletop_module(

inputlogicclk,

inputlogic[7:0]in,

inputlogicreset,//Synchronousreset

output[23:0]out_bytes,

outputlogicdone);

typedefenumlogic[1:0]{S0=2'd0,S1=2'd1,S2=2'd2,Done=2'd3}state_def;

state_defcur_state,next_state;

//Statetransitionlogic(combinational)

always_combbegin

case(cur_state)

S0:begin

next_state=S1;

end

S1:begin

next_state=S2;

end

S2:begin

next_state=in[3]?S0:Done;

end

Done:begin

next_state=in[3]?S0:Done;

end

default:begin

next_state=Done;

end

endcase

end

//Stateflip-flops(sequential)

always_ff@(posedgeclk)begin

if(reset)begin

cur_state<= Done ;

end

else begin

cur_state <= next_state ;

end

end

// Output logic

assign done = (cur_state == S2) ;

assign out_bytes = done ? out_bytes_temp : 24'd24 ;

var logic [23:0] out_bytes_temp ;

always_ff @( posedge clk ) begin

if (next_state == S0) begin

out_bytes_temp[23:16] <= in ;

end

else if (next_state == S1) begin

out_bytes_temp[15:8] <= in ;

end

else if (next_state == S2) begin

out_bytes_temp[7:0] <= in ;

end

end

endmodule

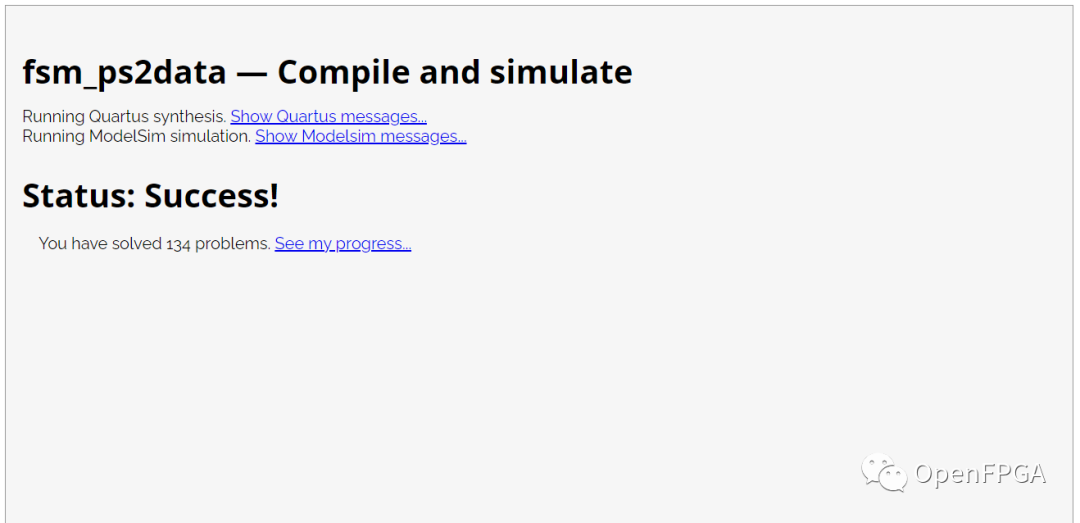

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

总结

今天的几道题就结束了,对于状态机的理解还是有益处的,三段式状态机是题目一直推崇的,类似状态机的公示,可以“套”进去。

审核编辑:刘清

-

HDL

+关注

关注

8文章

327浏览量

47374 -

状态机

+关注

关注

2文章

492浏览量

27526 -

fsm

+关注

关注

0文章

35浏览量

12821 -

Verilog语言

+关注

关注

0文章

113浏览量

8224

原文标题:HDLBits: 在线学习 SystemVerilog(十九)-Problem 126-133(状态机二)

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Verilog状态机+设计实例

如何写好状态机

浅谈状态机的要素、分类

什么是状态机?状态机5要素

状态模式(状态机)

如何合理高效地使用状态机呢?

如何合理高效地使用状态机呢?

评论