使用always_ff和在灵敏度列表中指定一个时钟边沿并不意味着过程中的所有逻辑都是时序逻辑。综合编译器将推断出每个被非阻塞赋值的变量的触发器。阻塞赋值也可能推断出触发器,这取决于赋值语句相对于程序中其他赋值和操作的顺序和上下文。

然而,在有些情况下,组合逻辑数据流行为将从时序逻辑程序中推断出来。

时序赋值右侧的操作符将综合为组合逻辑,其输出成为触发器的D输入。

如果时序分配的右侧调用一个函数,该函数将综合为组合逻辑,其输出成为触发器的D输入。

围绕着赋值语句的决策语句可能会综合为组合式多路复用逻辑,选择那个表达式作为触发器的D输入。

在begin-end语句组中对临时变量的阻塞赋值,将综合为组合逻辑,其中临时变量成为在begin-end中后续非阻塞赋值推断出的触发器的输入。

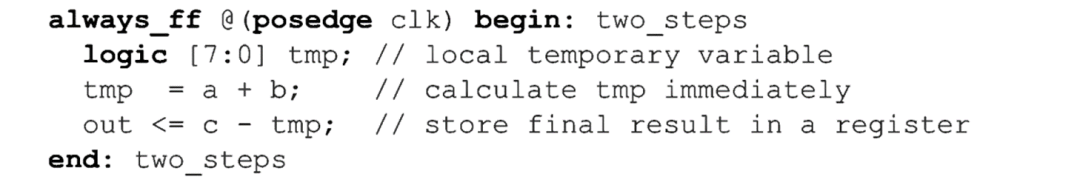

下面非例子说明了在begin-end语句组中对临时变量的阻塞赋值,将综合为组合逻辑。

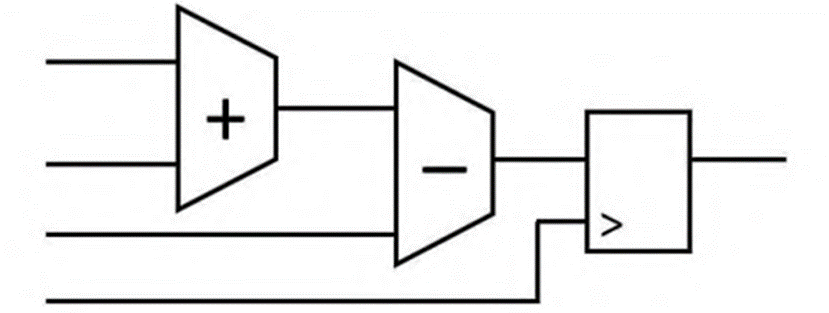

下面就是上面的例子中推断的示意图。

对中间临时变量的阻塞赋值

审核编辑 :李倩

-

逻辑

+关注

关注

2文章

833浏览量

29464 -

触发器

+关注

关注

14文章

2000浏览量

61132 -

时序

+关注

关注

5文章

387浏览量

37318

原文标题:【数字实验室】时序逻辑程序中推断组合逻辑?

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

时序逻辑程序中推断组合逻辑?

时序逻辑程序中推断组合逻辑?

评论