2001年,英特尔公布了第三代I/O技术——3GIO技术(后更名为PCI Express,即PCIe),以高性能、高扩展性、高可靠性及出色的兼容性取代了包括AGP和PCI在内所有的内部总线并且不断升格。例如,2019年5月底公布的PCIe 5.0,其以32Gb/s的单通道带宽与32GT/s(Giga Transmission per second)每通道数据传输速率,满足了现今绝大多数的需求。但应对数据TB级增长、异构计算大行其道的当下,PCIe在内存使用效率、延迟和数据吞吐量等方面,已经面临压力。

二十年后,在如今这个数据爆炸式增长,异构计算大行其道的当下,曾经的“未来之星“PCI-e 已经开始出现后继无人的现象,无法成为 CPU、GPU、FPGA 以及其他 AI 计算设备之间沟通的桥梁。为了达到最佳的计算效果,我们越来越期待一种以内存为中心的、富有变革性的新技术出现,基于PCI-e协议的CXL技术便在此环境下出世。

2019年,英特尔推出的CXL技术似乎杀出了重围。短短几年时间,CXL便成为业界公认的先进设备互联标准,其最为强劲的竞争对手Gen-Z、OpenCAPI都纷纷退出了竞争,并将Gen-Z协议、OpenCAPI协议转让给CXL。

1、**什么是CXL?**

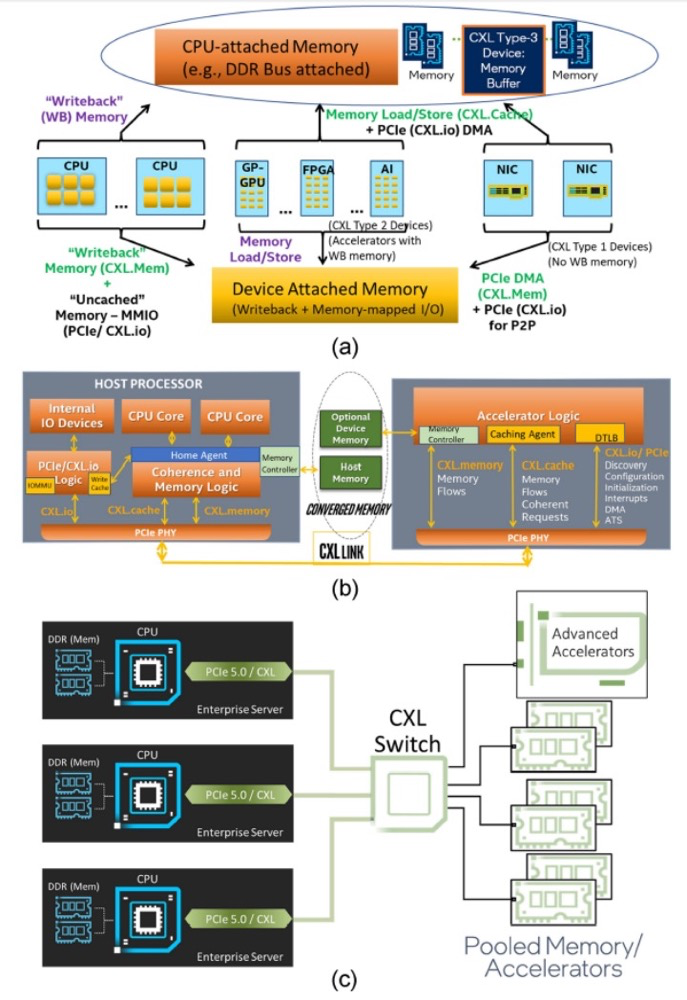

CXL全称为Compute Express Link,作为一种全新的开放式互联技术标准,其能够让CPU与GPU、FPGA或其他加速器之间实现高速高效的互联,从而满足高性能异构计算的要求,并且其维护CPU内存空间和连接设备内存之间的一致性。总体而言,其优势高度概括在极高兼容性和内存一致性两方面上。

** 2、CXL 协议**

CXL 标准定义了 3 个协议,这些协议在通过标准 PCIe 5.0 PHY 以 32 GT/s 传输之前一起动态复用:

CXL.io 协议本质上是经过一定改进的 PCIe 5.0 协议,用于初始化、链接、设备发现和列举以及寄存器访问。它为 I/O 设备提供了非一致的加载/存储接口。

CXL.cache 协议定义了主机和设备之间的交互,允许连接的 CXL 设备使用请求和响应方法以极低的延迟高效地缓存主机内存。

CXL.mem 协议提供了主机处理器,可以使用加载和存储命令访问设备连接的内存,此时主机 CPU 充当主设备,CXL 设备充当从属设备,并且可以支持易失性和持久性存储器架构。

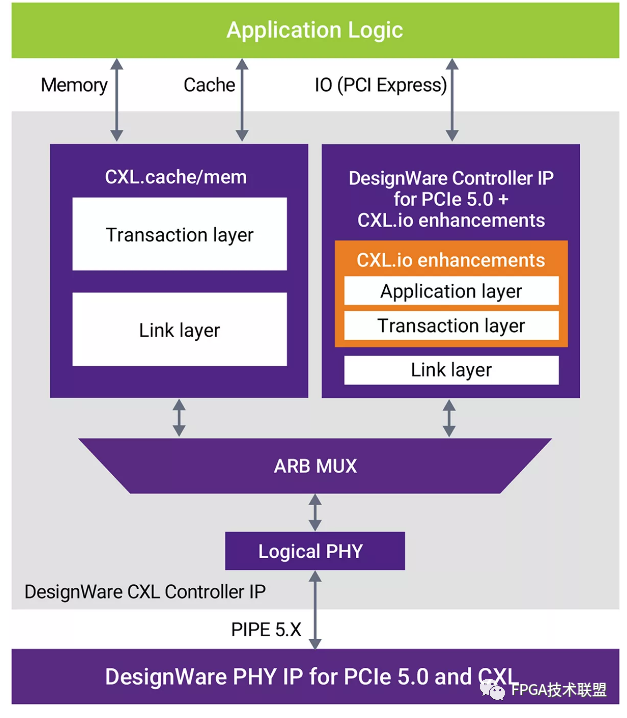

如图 1 所示,CXL.cache 和 CXL.mem 合并且共享一个公共链路和事务层,而 CXL.io 有自己的链路和事务层。

三个协议产生的数据都通过仲裁和多路复用 (ARB/MUX) 模块一起动态复用,然后被移交到 PCIe 5.0 PHY,进而以 32GT/s 的速度进行传输。ARB/MUX 在 CXL 链路层(CXL.io 和 CXL.cache/mem)发出的请求之间进行仲裁,并根据仲裁结果复用数据,仲裁结果使用加权循环仲裁,权重由主机设置。ARB/MUX 还处理链路层发出的功耗状态转换请求,向物理层创建实现有序降耗操作的单个请求。

CXL 通过固定宽度的 528 位微片传输数据,该微片由四个 16 字节时隙组成,并添加了两个字节 CRC:(4 x 16 + 2 = 66 字节= 528 位)。插槽采用多种格式定义,可专用于 CXL.cache 协议或 CXL.mem 协议。片头定义了插槽格式,并携带允许事务层将数据正确路由到预期协议的信息。

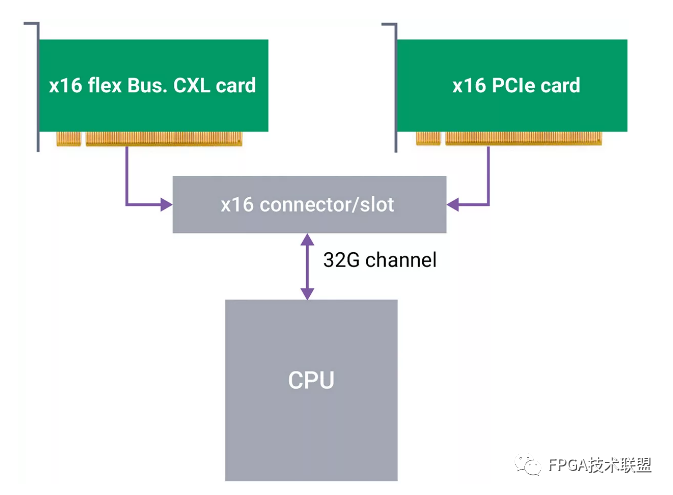

由于 CXL 使用 PCIe 5.0 PHY 和电气元件,它可以有效地插入到任何可以通过 Flex Bus 使用 PCIe 5.0 的系统中。Flex Bus 是一个灵活的高速端口,可以静态配置为支持 PCIe 或 CXL。图 2 举例显示了 Flex Bus 链路。这种方法使 CXL 系统能够利用 PCIe 重定时器;但是,目前 CXL 仅定义为直连 CPU 链路,因此无法利用 PCIe 交换机。随着标准的逐步完善,交换功能可能会被添加到标准中;如果是这样,则需要创建新的 CXL 交换机。

3、CXL 设备类型

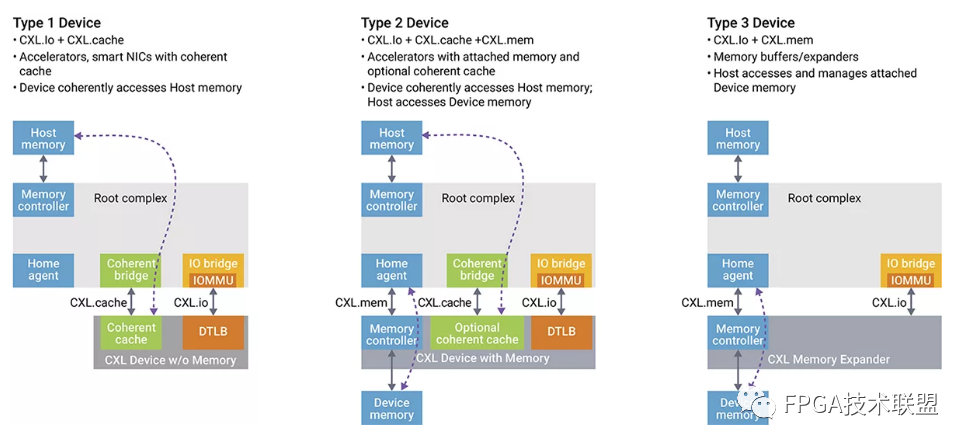

CXL.io 协议用于初始化和链接,所以必须获得所有 CXL 设备的支持,如果 CXL.io 协议发生故障,链接就无法运行。其他两个协议的不同组合产生了总共三种被定义并受 CXL 标准支持的独特 CXL 设备类型。

图 3 显示了三种已定义的 CXL 设备类型及其相应的协议、典型应用以及支持的存储器访问类型。

对于 2 型设备,CXL 定义了两个一致性“偏置”,用于控制 CXL 对主机和设备连接存储器之间的一致性数据的处理方式。偏置模式指主机偏置和设备偏置,并且操作模式可以根据需要发生改变,从而在链路操作期间优化给定任务的性能。

2 型设备(例如,加速器)处理提交给主机的工作时间及其后续完成之间的数据时,设备偏置模式用于确保设备可以直接访问其设备连接的存储器,而无需与主机的一致性引擎通信。因此,设备可保证主机没有缓存线路。这为设备提供了最优的延迟性能,使得设备偏置成为加速器执行工作的主要操作模式。主机处于设备偏置模式时,主机仍然可以访问设备连接的存储器,但性能却不是最优。

主机偏置模式优先考虑从主机到设备连接存储器的一致性访问。该模式通常在工作提交期间使用,此时数据会从主机写入设备连接的存储器,而且在主机将数据从设备连接的存储器中导出后,可使用该模式完成工作。在主机偏置模式下,设备连接的存储器对于设备而言就像主机连接的存储器一样,如果设备需要访问,就通过一条发送到主机的请求进行处理。

可以使用软件或硬件,通过软件辅助和硬件自治这两种受支持的模式管理机制来控制偏置模式。加速器或其他 2 型设备可以选择偏置模式,如果两种模式均未选择,则系统默认为主机偏置模式,这样就必须通过主机路由对设备连接存储器进行所有访问。偏置模式可以使用 4KB 页面的颗粒度进行更改,并通过 2 型设备中执行的偏置表进行跟踪。

CXL 标准的一个重要特征是一致性协议是不对称的。Home 缓存代理仅停留在主机中。因此,主机控制存储器的缓存,从而解决连接的 CXL 设备请求的给定地址的整个系统的一致性问题。这完全不同于正在使用的现有专有和公开的一致性协议,特别是那些用于 CPU 到 CPU 连接的协议,因为它们通常是对称的,会使得所有互连设备都变得对等。

虽然这样有一些优点,但是对称的高速缓存一致性协议更加复杂,并且所有设备都必须处理由此产生的复杂性。具有不同架构的设备可以采用不同的方法来实现在微架构级别优化的一致性,而这一情况可能会为实现广泛的行业采用增加难度。通过使用主机控制的非对称方法,可以将不同的 CPU 和加速器轻松纳入新兴 CXL 生态系统。

** 4、CXL的未来**

可以设想在具有内存一致性的大型系统中同时使用多个协议来处理 CPU 到 CPU、CPU 到连接设备以及更长距离的机箱到机箱要求。目前,CXL 致力于为服务器提供经过优化的解决方案。CXL 固有的不对称性意味着它可能不适用于 CPU 到 CPU 或加速器到加速器的连接。

-

FPGA

+关注

关注

1629文章

21729浏览量

602960 -

cpu

+关注

关注

68文章

10854浏览量

211567 -

gpu

+关注

关注

28文章

4729浏览量

128887

发布评论请先 登录

相关推荐

关于Gen-Z语义存储(memory-semantic)体系架构探讨

如何创建最佳的网络和架构 一文解析Gen-Z架构

CXL事务层的结构是由哪些部分组成的

DirectCXL内存分解原型设计实现

一文详解CXL链路层格式的定义

DesignWare CXL为SoC提供优化的多芯片IP堆栈

Saniffer开放实验室库存并提供测试工具

澜起科技发布全球首款CXL™ 内存扩展控制器芯片

一文读懂CXL协议

CXL协议和标准介绍, CXL2.0和3.0有什么新功能?

SMART Modular 世迈科技推出高性能服务器专用全新CXL® 内存扩充卡系列

打造异构计算新标杆!国数集联发布首款CXL混合资源池参考设计

如何利用CXL协议实现高效能的计算架构

什么是CXL协议

什么是CXL协议

评论