你可能已经在智能手机上播放过成百上千个视频了,那么,你有没有想过当你按下“播放”键时发生了什么?

• 一触碰那个小三角形按键,便会立刻发生很多事。在几微秒内,手机处理器上空闲的计算内核就启动了。与此同时,它们的电压和时钟频率会迅速上升,以确保视频解压和显示不会延迟。同时,在后台运行任务的其他内核也会降低速度。电荷会涌进活跃内核的数百万个晶体管中,在新闲置的内核中则慢得像涓涓细流。

•这种跳动在片上系统(SoC)的处理器中不断发生着,被称为“动态电压和频率缩放”(DVFS),它支撑着手机和笔记本电脑以及服务器的运行。

这一切都是为了平衡计算的性能和功耗,这对智能手机来说尤其具有挑战性。应用DVFS的电路会力图确保在电流激增时,时钟和电压水平稳定可靠,它们也是最难设计的部分之一。 这主要是因为,时钟产生电路和电压调节电路与智能手机SoC上的任何东西都不同,它们是vwin

电路。得益于半导体制造业的进步,我们已越来越习惯于每年都会出现运算能力大大提高的新处理器。将一个数字设计从旧半导体工艺“移植”到新工艺中绝非易事,但与尝试将模拟电路移植到一个新工艺上相比,这算不了什么。

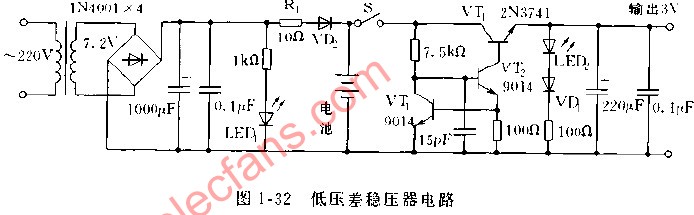

实现DVFS的模拟元件,尤其是一种称为“低压差稳压器”(LDO)的电路,并不会像数字电路那样按比例缩小,基本上每一代新产品都必须从头开始重新设计。 如果我们可以用数字元件来制作LDO或其他模拟电路,那么其移植难度就会大大降低,从而节省大量设计成本,并且能解放工程师,让他们去解决尖端芯片设计面临的其他问题。此外,由此制成的数字LDO会比模拟LDO小得多,且在某些方面的表现会更好。过去几年,业界和学术界的研究团队已经测试了至少十几种设计,尽管还存在一些缺点,但商业上有用的数字LDO可能很快就能实现。

典型的智能手机SoC是一个集成奇迹。它在一块硅片上集成了多个中央处理机(CPU)核、一个图形处理单元、一个数字信号处理器、一个神经处理单元、一个图像信号处理器、一个调制解调器,以及其他专用逻辑块。当然,提高驱动这些逻辑块的时钟频率会提高它们完成工作的速度。不过,要在更高的频率下工作,也需要更高的电压。否则,晶体管就无法在处理器时钟下一次走动之前打开或关闭。当然,更高的频率和电压是以耗电为代价的。因此,根据完成分配工作(拍摄视频、播放音乐文件、在通话中传输语音等)所需的能源效率和性能之间的平衡,这些内核和逻辑单元会动态地改变其时钟频率和电源电压,通常在0.95到0.45伏之间。

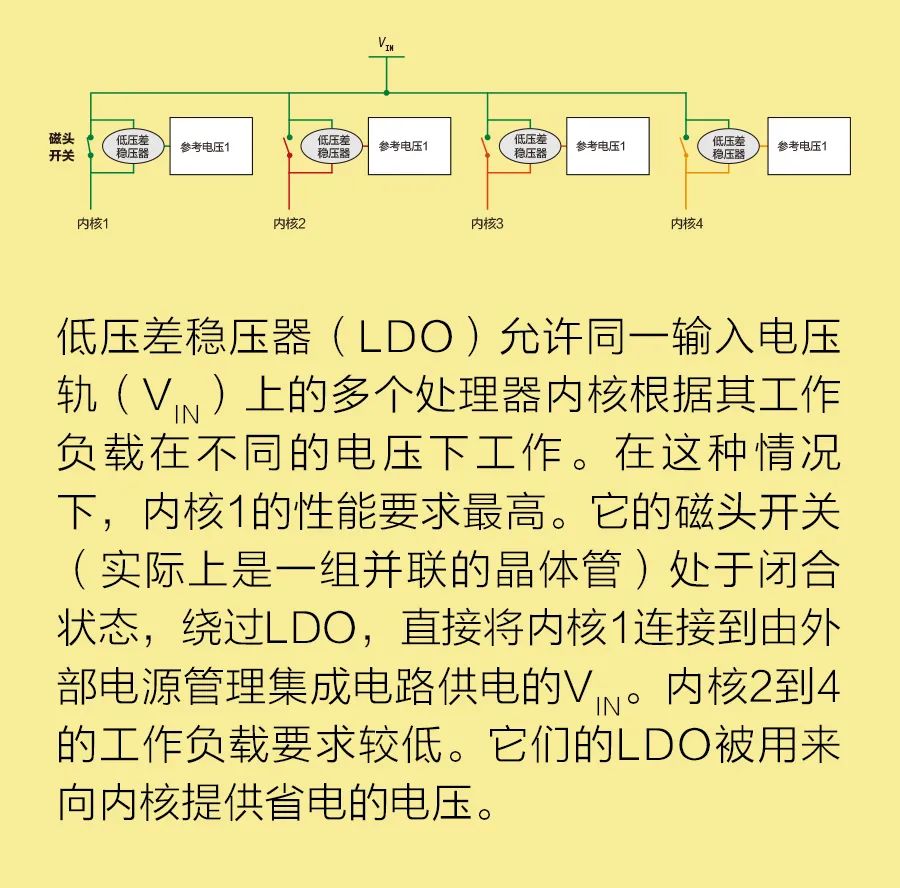

通常,外部电源管理集成电路会为手机SoC生成多个输入电压(VIN)值。这些电压会沿着被称为“轨”的宽连接线被输送到SoC芯片的各个区域,但是电源管理芯片与SoC之间的连接数量有限,因此,SoC上的多个内核必须共享同一个VIN轨。 不过,由于存在低压差稳压器,它们不必都具备相同的电压。LDO以及专用的时钟发生器允许共享轨上的每个内核按照独有的电源电压和时钟频率运行。需要最高电源电压的内核会决定共享的VIN值。电源管理芯片将VIN设置为这个值,该内核则会通过被称为“磁头开关”的晶体管绕过LDO。

为了将功耗降到最低,其他内核可以在较低的电源电压下工作。软件决定了这个电压值应该是多少,而模拟LDO在提供相应电压方面做得相当好。它们结构紧凑、制造成本低,而且集成在芯片上也相对简单,因为它们不需要大型电感器或电容器。

不过,这些LDO只能在特定的电压窗口下工作。就其高值而言,目标电压必须低于VIN和LDO本身的电压下降(也叫“电压差”)之间的差值。例如,如果内核最有效的电源电压为0.85伏,但VIN为0.95伏,LDO的电压差为0.15伏,则该内核无法利用LDO来达到0.85伏,相反必须在0.95伏下工作,这就浪费了一些功率。

类似地,如果VIN已经被设置在某个电压限制以下,那么LDO的模拟元件将无法正常工作,电路也无法进一步降低该内核的电源电压。 如果所需电压落在LDO的窗口内,软件将启用电路并激活与目标电源电压相等的参考电压。

那么LDO如何提供正确的电压呢?

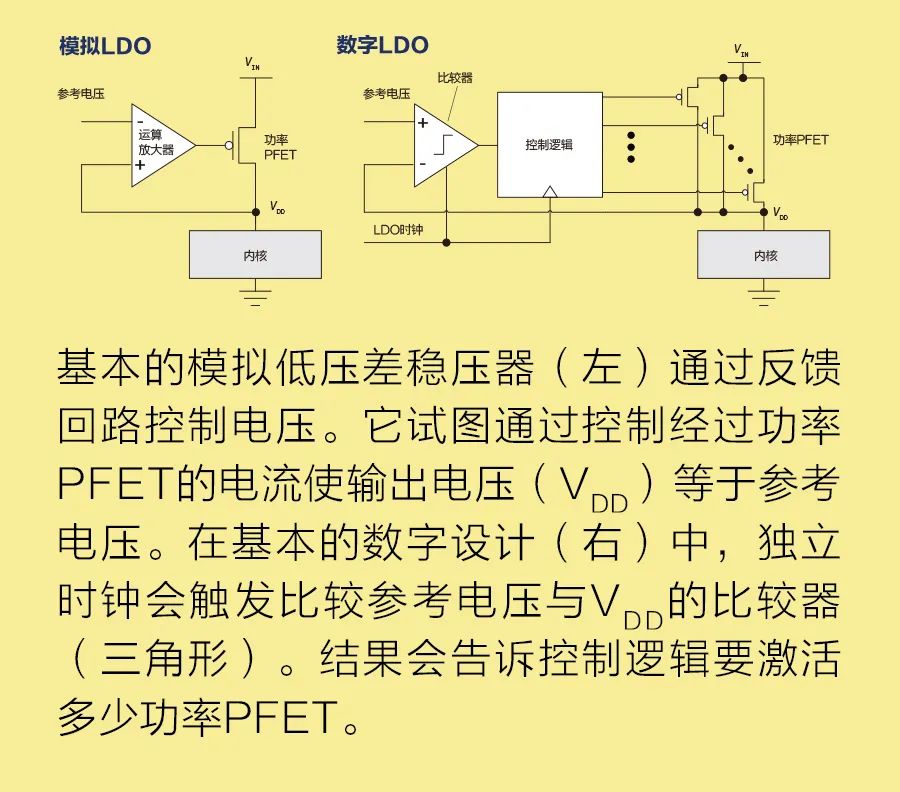

在基本的模拟LDO设计中,它是通过运算放大器、反馈和专用功率p沟道场效应晶体管(PFET)实现的。后者是一种晶体管,可随着电压增加至栅极而减小其电流。该功率PFET的栅极电压来自运算放大器的模拟信号,范围在0伏和VIN之间。

运算放大器会持续比较电路的输出电压(内核的电源电压或VDD)与目标参考电压。如果LDO的输出电压下降到参考电压以下,就像新激活的逻辑突然需要更多电流时一样,运算放大器会降低功率PFET的栅极电压,增加电流并将VDD提升到参考电压值。相反,如果输出电压上升到参考电压以上,就像内核的逻辑不太活跃时一样,那么运算放大器就会提高晶体管的栅极电压以降低电流和VDD。

另一方面,一个基本的数字LDO由一个电压比较器、控制逻辑和多个并联功率PFET组成。(LDO也有自己的时钟电路,与处理器内核使用的时钟电路分开。)在数字LDO中,电源PFET的栅极电压是二进制值而不是模拟值,所以要么是0伏要么是VIN。 随着时钟的每一次走动,比较器会测量输出电压是低于还是高于基准源提供的目标电压。

比较器输出会引导控制逻辑确定要激活多少功率PFET。如果LDO的输出低于目标值,则控制逻辑会激活更多功率PFET。它们的组合电流支撑着内核的电源电压,而该值会反馈给比较器,使其与目标一致。如果高于目标值,比较器就会向控制逻辑发送信号,关闭一些PFET。

当然,无论是模拟LDO还是数字LDO都不是理想的选择。模拟设计的主要优点在于,它可以快速响应电源电压的瞬态下降和过冲,当涉及急剧变化时这尤为重要。之所以会发生这些瞬变,是因为内核对电流的需求可以在几纳秒内大幅上升或下降。除了快速响应外,模拟LDO还能很好地抑制来自轨上其他内核的VIN变化。

最后,在电流需求变化不大时,它还能严格控制输出,而不会以一种在VDD中引入波纹的方式不断地对目标进行过冲和下冲。 这些特性使得模拟LDO不仅在提供处理器内核方面具有优势,而且在几乎所有要求安静、稳定电源电压的电路中都具备优势。然而,有一些关键性挑战因素限制了这些设计的有效性。

首先,模拟元件比数字逻辑复杂得多,在先进的技术节点上实现它们需要长时间的设计。其次,VIN较低时,它们无法正常工作,从而限制了它们向内核传输的VDD最低值。最后,模拟LDO的电压差并不像设计者希望的那么小。 综合最后这几点,模拟LDO提供了一个其能够工作的有限电压窗口。这意味着无法用LDO实现省电,而用LDO实现省电能够显著提高智能手机电池的寿命。 数字LDO则解决了其许多弱点:没有复杂的模拟元件,设计师能够利用丰富的工具和其他资源进行数字设计。

因此,为了使用一种新的工艺技术而缩小电路规模所需要做的工作更少。数字LDO也将在更大的电压范围内工作。在低电压端,数字元件可以在超出模拟元件范围的VIN值下工作。在高电压端,数字LDO的电压差将更小,从而能有效地节省内核功率。 不过,凡事各有利弊,数字LDO也有一些严重的缺点。其中大部分是因为电路只会间歇性地测量和改变其输出,而不会连续测量和改变输出。这意味着电路对电源电压下降和过冲的响应相对较慢。它对VIN的变化也更敏感,而且往往会在输出电压中产生小波动,这两种情况都会降低内核的性能。

目前,限制数字LDO使用的主要障碍是其缓慢的瞬态响应。当内核汲取的电流在响应其工作负载的变化时突然发生变化,则内核会经历下降和过冲。要限制电压下降的程度和持续时间,LDO对下降事件的响应时间至关重要。传统内核给电源电压增加了一个安全裕度,以确保其在下降期间能正常工作。更多的预期下降意味着裕度必须更大,这就降低了LDO的能效效益。因此,加快数字LDO对下降和过冲的响应是这一领域前沿研究的主要焦点。

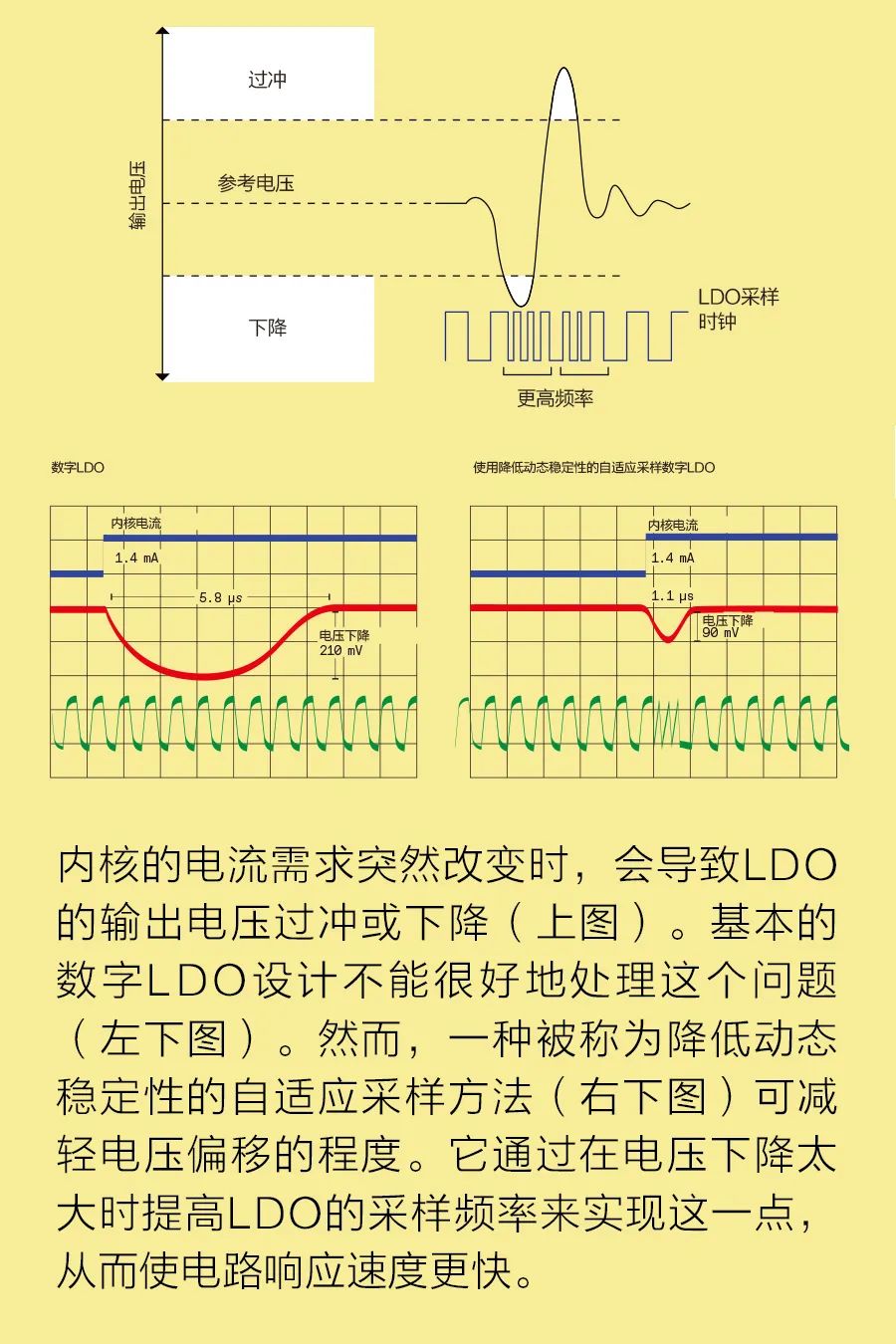

最近取得的一些进步有助于加速电路对下降和过冲的响应。其中一种方法将数字LDO的时钟频率作为控制旋钮,以稳定性和功率效率换取响应时间。 较低的频率提高了LDO的稳定性,这是因为输出不会经常改变。它还降低了LDO的功耗,因为构成LDO的晶体管切换频率较低。

不过,其代价是对来自处理器内核的瞬态电流需求的响应较慢。细想可知,如果频率太低,就可能在一个单一时钟周期内发生一个瞬态事件,因此会出现这种情况。 高LDO时钟频率反而会缩短瞬态响应时间,因为比较器进行输出采样的频率足以在瞬态事件发生之前改变LDO的输出电流。

然而,这种恒定采样会降低输出的稳定性并消耗更多的功率。 这种方法的要点是引入一种其频率能够适应这种情况的时钟,即降低动态稳定性的自适应采样频率方法。当电压下降或过冲超过一定水平时,时钟频率会提高,以更快地减少瞬态效应。然后它会减慢速度以消耗更少的功率并保持输出电压稳定。

这种效果是通过添加一对额外的比较器来检测过冲和下降情况,并触发时钟来实现的。在测量使用这种技术的测试芯片时,VDD的电压下降从210毫伏降低到了90毫伏,与标准的数字LDO设计相比降低了57%。电压恢复到稳定状态的时间从5.8微秒缩短到1.1微秒,所需时间缩短了81%。

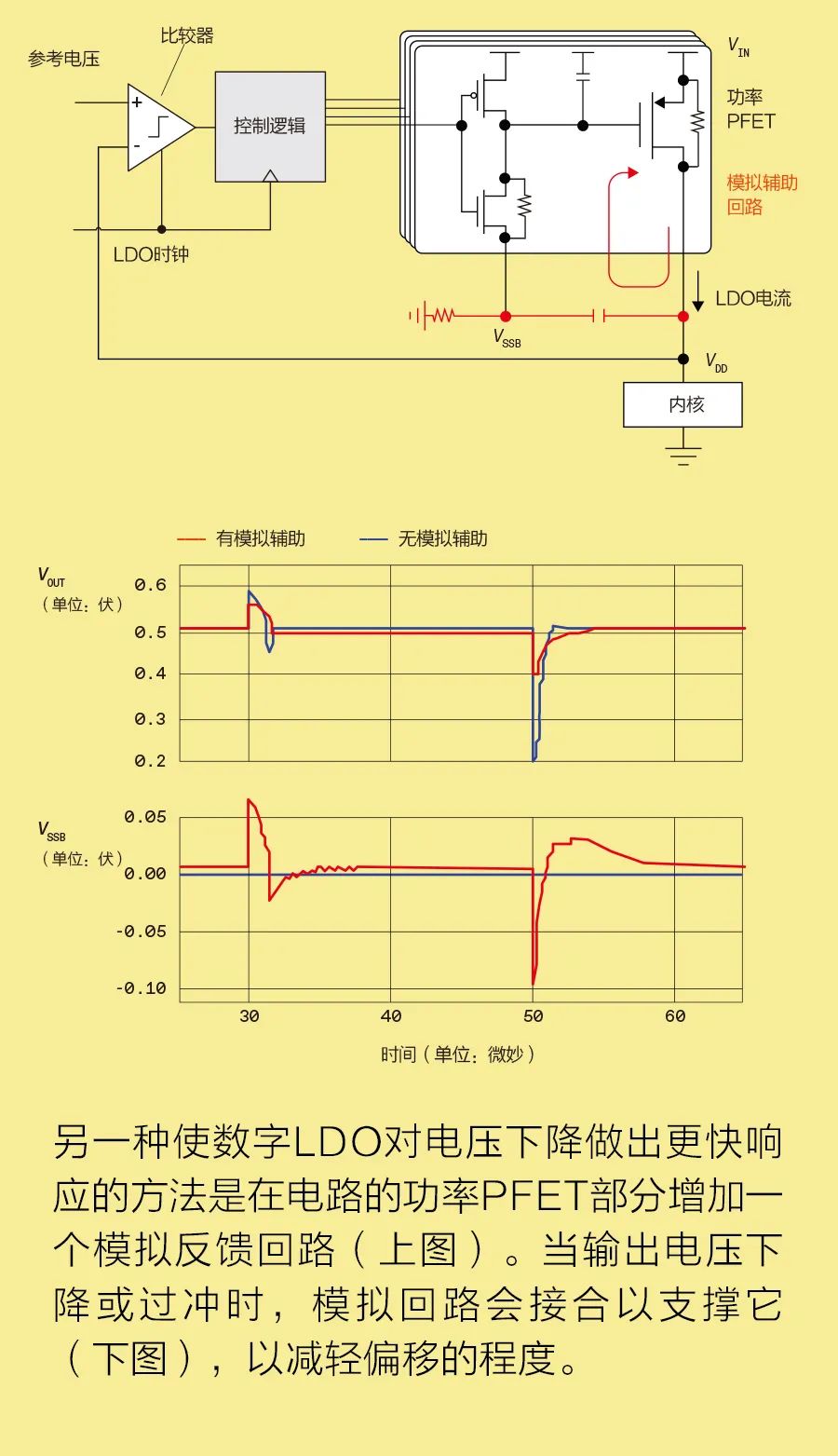

另一种缩短瞬态响应时间的方法是给数字LDO增加一点模拟性。这种设计集成了一个独立的模拟辅助回路,可对负载电流瞬变作出即时响应。模拟辅助回路可通过一个电容器将LDO的输出电压耦合到LDO的并联PFET,从而形成一个仅在输出电压急剧变化时才接合的反馈回路。因此,当输出电压下降时,它会降低已激活PFET栅极的电压,并瞬间增加流向内核的电流,以降低电压下降幅度。

现已证明,这种模拟辅助回路可以将电压下降从300毫伏降低到106毫伏(改善65%),可将过冲从80毫伏降低到70毫伏(改善13%)。 当然,这两种技术都有各自的缺点。首先,两者都不能真正匹配现在的模拟LDO的响应时间。此外,自适应采样频率技术需要两个额外的比较器,还需要生成并校准下降和过冲参考电压,以便电路知道何时使用更高的频率。

模拟辅助回路包括了一些模拟元件,会减少全数字系统的设计时间效益。 商用SoC处理器的发展即使不能完全匹配模拟性能,也可能有助于数字LDO取得更大的成功。如今,商用SoC处理器集成了全数字自适应电路,以便在出现电压下降时缓解性能问题。

例如,这些电路会暂时延长内核的时钟周期,防止计时错误。这种缓解技术可以放宽瞬态响应时间限制,允许使用数字LDO并提高处理器效率。如果是这样,我们就可以期待更高效的智能手机和其他电脑,同时让它们的设计过程更加轻松简单。

审核编辑:刘清

-

稳压器

+关注

关注

24文章

4222浏览量

93755 -

晶体管

+关注

关注

77文章

9681浏览量

138070 -

低压差稳压器

+关注

关注

0文章

158浏览量

20709 -

DVFS

+关注

关注

1文章

17浏览量

11996 -

LDO电路

+关注

关注

0文章

26浏览量

2444

原文标题:可延长电池寿命的电路

文章出处:【微信号:CloudBrain-TT,微信公众号:云脑智库】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

LDO低压差线性稳压器

LDO低压差线性稳压器的简介

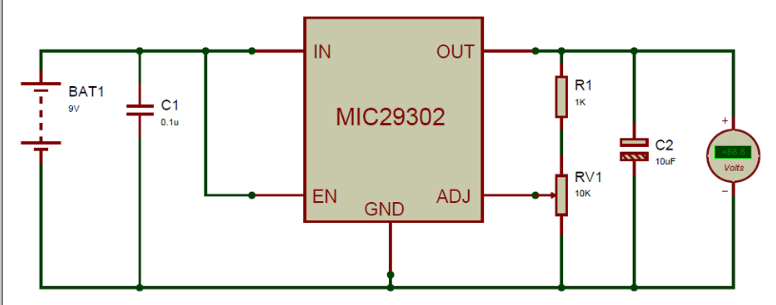

使用MIC29302构建LDO稳压器或低压差稳压器电路

具有ULQ™ 模式、可延长电池寿命的4.5V至24V、8A同步降压稳压器TPS51396A数据表

可延长电池寿命的电路—低压差稳压器LDO电路

可延长电池寿命的电路—低压差稳压器LDO电路

评论