Maxim生产多条延迟块。本应用笔记比较了每个可编程延迟块和非可编程延迟块,以帮助客户选择适合其应用的器件。由于这些器件的许多特性不容易分类到在线参数数据库中的字段中,因此本应用笔记旨在展示延迟块系列成员的并排比较,并消除在尝试选择器件时筛选大量数据手册的麻烦。

可编程延迟线比较

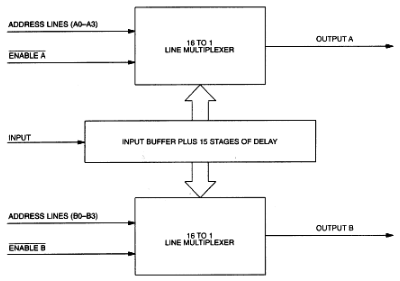

Maxim的可编程延迟块采用5.0V电源供电,提供SO或DIP封装 包。可编程延迟块使客户能够在器件使用后对延迟进行编程 安装在应用程序中。下面对每个器件进行描述,并在表1中比较了主要特性。一个 可编程延迟块的功能图如图1所示。

图1.可编程延迟块功能图。

DS1020

DS1020为8位延迟线。DS1020提供5种版本(虚线号),具有不同的步长(0.15ns、0.25ns、0.5ns、1ns和2ns)。延迟范围为 10ns 至 520ns,可使用 3 线串行接口或 8 位并行接口进行编程。

DS1021

DS1021与DS1020相同,只是只有两种步长(0.25ns和0.5ns),最小值抄送上电时间。延迟范围为 10ns 至 137.5ns,可使用 3 线串行接口或 8 位并行接口进行编程。

DS1023

DS1023与DS1020/1021类似,但增加了一些功能。该器件能够将信号延迟长达一整周期或更长时间,并且信号也可以反转。DS1023还可以输出脉宽调制信号。片内基准延迟产生0ns的阶跃零延迟。延迟范围为 0ns 至 1275ns,具有 5 种不同的步长(0.25ns、0.5ns、1ns、2ns 和 5ns),可使用 3 线串行接口或 8 位并行接口进行编程。

DS1040

DS1040为可调的单脉冲发生器。脉冲宽度范围为 5ns 至 500ns 和步进 可以使用并行接口在 2.5ns 至 100ns 范围内编程,具体取决于版本。

DS1045

DS1045为4位双通道延迟线。该器件具有两个独立可编程输出。延迟范围为 9ns 至 84ns,步长为 3ns、4ns 或 5ns(取决于版本),可使用并行接口进行编程。

表 1.可编程延迟块比较

| DS1020 | DS1021 | DS1023 | DS1040 | DS1045 | |

| Vcc | 5V | 5V | 5V | 5V | 5V |

| Package | 16 引脚 DIP,16 引脚 SO | 16 针 SO | 16 引脚 DIP,16 引脚 SO | 8 引脚 DIP,8 引脚 SO | 16 引脚 DIP,16 引脚 SO |

| 可用步长 (ns) | 0.15, 0.25, 0.5, 1, 2 | 0.25, 0.5 | 0.25, 0.5, 1, 2, 5 | 2.5, 15, 20, 30, 40, 50, 100 | 3, 4, 5 |

| 程序步骤数 | 256 | 256 | 256 | 5 | 16 |

| 脉冲宽度的最小/最大延迟 (ns) | 10/520 | 10/138 | 0/1275 | 5/500 | 9/84 |

| 使? | 是的 | 是的 | 是的 | 不 | 是的 |

| 参考/PWM输出? | 不 | 不 | 是(参考/PWM 引脚) | 不 | 不 |

| 有源电源电流 | 30毫安 | 30毫安 | 60毫安 | 75毫安 | 35毫安 |

| 输出数量 | 1 | 1 | 1 | 2(输出、输出引脚) | 2 |

| 编程接口 | 3 线或 8 位并行 | 3 线或 8 位并行 | 3 线或 8 位并行 | 3 位并行 | 4 位并行 |

注意

:此处提供了设备规格以供设备比较。如果本应用笔记与数据手册不一致,则以数据手册为准。

非可编程延迟线比较

表2和表3列出了每个非可编程延迟块的一些器件规格。有并行和抽头的不可编程延迟线。

并行延迟线

下面列出的器件是并行延迟块。平行延迟块具有多个独立的延迟单元。并行延迟块的功能图见图2。

图2.非可编程三合一并行延迟块功能图。

DS1013/DS1135/DS1135L

DS1013、DS1135和DS1135L为三合一硅延迟线。DS3为1.1135V高速版本,推荐替代DS5和DS0。DS1013L是DS1035的1135.3V版本,推荐替代DS3。所有这些器件都具有前沿和后沿精度。DS1135/DS1033L的标称延迟容限优于DS1135。DS1135的标称延迟容差为±1013.1013ns,DS2/DS0L的标称延迟容差为±1135.1135ns。DS1有0个版本(虚线号),延迟从1013ns到17ns不等。DS10有200个版本,延迟从1135ns到8ns。DS6L有30个版本,延迟从1135ns到6ns。

DS1033/DS1035

DS1033为3.3V器件,DS1035为5.0V器件。两款器件均具有 3 个独立的延迟,具有前沿和后沿精度。标称延迟容差为 ±1.5ns。DS1033有7个版本,延迟范围为8ns至30ns。DS1035有8个版本,延迟范围为6ns至30ns。DS1135是DS1035的推荐替代品,DS1135L是DS1033的推荐替代品。

DS1044

DS1044具有与DS1035相同的容差,但它具有4个延迟,而不是3个延迟。此外,可用的延迟略有不同。DS1044有10个版本,延迟范围为5ns至25ns。标称延迟容差为 ±1.5ns。

DS1007

DS1007具有7个延迟。前 4 个延迟(1 至 4)可以设置在 3ns 到 10ns 之间,并且仅具有前沿精度。最后 3 个延迟(5 至 7)可以设置在 9ns 和 40ns 之间,并具有前沿和后沿精度。标称延迟容差为 ±2.0ns。

表 2.非可编程并行延迟线比较

| DS1013 | DS1033 | DS1035 | DS1135 | DS1135L | DS1044 | DS1007 | |

| Vcc | 5V | 3.3V | 5V | 5V | 3.3V | 5V | 5V |

| Package | 14 引脚 DIP,16 引脚 SO,8 引脚 DIP | 8 引脚 DIP,8 引脚 SO | 8 引脚 DIP,8 引脚 SO | 8 引脚 DIP、8 引脚 SO、8 引脚 μSOP | 8 引脚 SO,8 引脚 μSOP | 14 引脚 DIP,14 引脚 SO | 16 引脚 DIP,16 引脚 SO |

| 独立延迟数 | 3 | 3 | 3 | 3 | 3 | 4 | 7 |

| 可用延迟总数 (ns) | 10 到 200 | 8 到 30 | 6 到 30 | 6 到 30 | 10 到 30 | 5 到 25 | 3 至 10、9 至 40 |

| 标称公差 | ±2.0纳秒 | ±1.5纳秒 | ±1.5纳秒 | ±1.0纳秒 | ±1.0纳秒 | ±1.5纳秒 | ±2.0纳秒 |

注意

:此处提供了设备规格以供设备比较。如果本应用笔记与数据手册不一致,则以数据手册为准。

抽头延迟线

下面列出的器件是具有前沿和后沿精度的分接延迟块。抽头延迟线具有多个串联的延迟单元。当应用需要具有一个输入和多个延迟输出的延迟线(例如多相时钟)时,分接延迟非常有用。有关抽头延迟块功能图,请参见图3。

图3.非可编程5抽头延迟线功能图。

DS1000

DS1000已经过时,但已被引脚对引脚兼容的DS1100取代。请参见下面的DS1100/DS1110L部分。

DS1004

DS1004为5抽头延迟线。延迟范围为 5ns 至 25ns。步长从 2ns 到 5ns 不等,具体取决于器件的版本。输入到抽头的标称延迟容差为 ±1.5ns。DS1004还具有±0.75ns的抽头到抽头标称容差。

DS1005

DS1005也是5抽头延迟线,但延迟和步长都比DS1004大。延迟范围为 12ns 至 250ns。步长从 12ns 到 50ns 不等,具体取决于器件的版本。输入到抽头的标称延迟容差为 ±2ns。

DS1100/DS1100L

DS1100和DS1100L为5抽头延迟线。DS1100和DS1100L是改进型,分别是DS1000的5V和3.3V版本的直接替代品。延迟范围为 4ns 至 500ns。步长从 4ns 到 100ns 不等,具体取决于器件的版本。输入到抽头的标称延迟容差为 ±2ns。

DS1010

DS1010为10抽头延迟线。延迟范围为 5ns 至 500ns。步长从 5ns 到 50ns 不等,具体取决于器件的版本。输入到抽头的标称延迟容差为 ±2ns。

DS1110/DS1110L

DS1110和DS1110L为10抽头延迟线。DS1110和DS1110L分别是DS1010的改进型和5V和3.3V版本的直接替代品。DS5的延迟范围为500ns至1110ns,步长为5ns至50ns,具体取决于器件的版本。DS10L的延迟范围为500ns至1110ns,步长为10ns至50ns,具体取决于器件的版本。DS2/DS1110L的输入抽头标称延迟容差为±1110ns。

表 3.非可编程抽头延迟线比较

| DS1004 | DS1005 | DS1100 | DS1100L | DS1010 | DS1110 | DS1110L | |

| Vcc | 5V | 5V | 5V | 3.3V | 5V | 5V | 3.3V |

| Package | 8 引脚 DIP,8 引脚 SO | 14 引脚 DIP,16 引脚 SO,8 引脚 DIP | 8 引脚 DIP、8 引脚 SO、8 引脚 μSOP | 8 引脚 DIP、8 引脚 SO、8 引脚 μSOP | 14 引脚 DIP,16 引脚 SO | 14 引脚 DIP,16 引脚 SO,14 引脚 TSSOP | 14 针 TSSOP |

| 抽头数量 | 5 | 5 | 5 | 5 | 10 | 10 | 10 |

| Delat to First Tap (ns) | 5 | 12 到 50 | 4 到 60 | 4 到 60 | 5 到 100 | 5 到 50 | 5 到 50 |

| 点按递增(步长)(纳秒) | 2、3、4 或 5 | 12 到 50 | 4 到 100 | 4 到 100 | 5 到 100 | 5 到 50 | 5 到 50 |

| 可用延迟总数 (ns) | 5 到 25 | 12 到 250 | 4 到 500 | 4 到 500 | 5 到 500 | 5 到 500 | 5 到 500 |

| 标称公差 | ±1.5纳秒 | ±2纳秒 | ±5纳秒 | ±5纳秒 | ±5纳秒 | ±5纳秒 | ±5纳秒 |

注意:此处提供了设备规格以供设备比较。如果本应用笔记与数据手册不一致,则以数据手册为准。

结论

本应用笔记比较了Maxim的延迟块,以帮助客户选择适合其应用的器件。这种比较将防止客户筛选多个数据表和在线参数数据库。

审核编辑:郭婷

-

电源

+关注

关注

184文章

17704浏览量

249949 -

Maxim

+关注

关注

8文章

859浏览量

87170 -

DIP

+关注

关注

0文章

241浏览量

30137

发布评论请先 登录

相关推荐

有谁使用过延迟线······

SY89297U,GB以太网交换机延迟线评估板

通过数字控制和模拟控制延迟输入信号的SY89296L可编程延迟线评估板

SY89296L 2.5V/3.3V 2.5GHz可编程延迟线评估板

如何计算延迟线的最大工作频率

基于CARRY4延迟线的设计怎么实现?

Data Delay Device, Inc模拟和数字延迟线以及延迟线应用模块和滤波器的设计者

基于CPLD的高速可程控数字延迟线系统的设计与实现

FPGA/可编程逻辑器件(4)

DS1045双通道4位可编程延迟线的器件特性

Maxim可编程延迟线比较

Maxim可编程延迟线比较

评论